Packaging technique and packaging structure

A packaging process and packaging structure technology, applied in the direction of semiconductor/solid-state device components, semiconductor devices, electrical components, etc., can solve problems such as fragmentation and reduce production yield, and achieve the effect of preventing fragmentation, reducing difficulty, and increasing strength

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

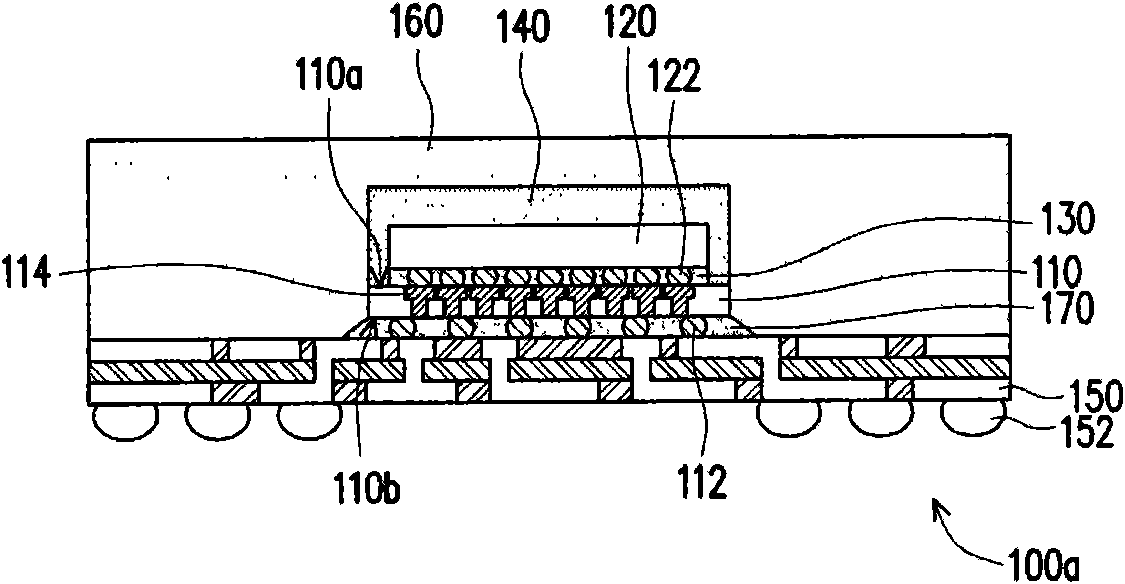

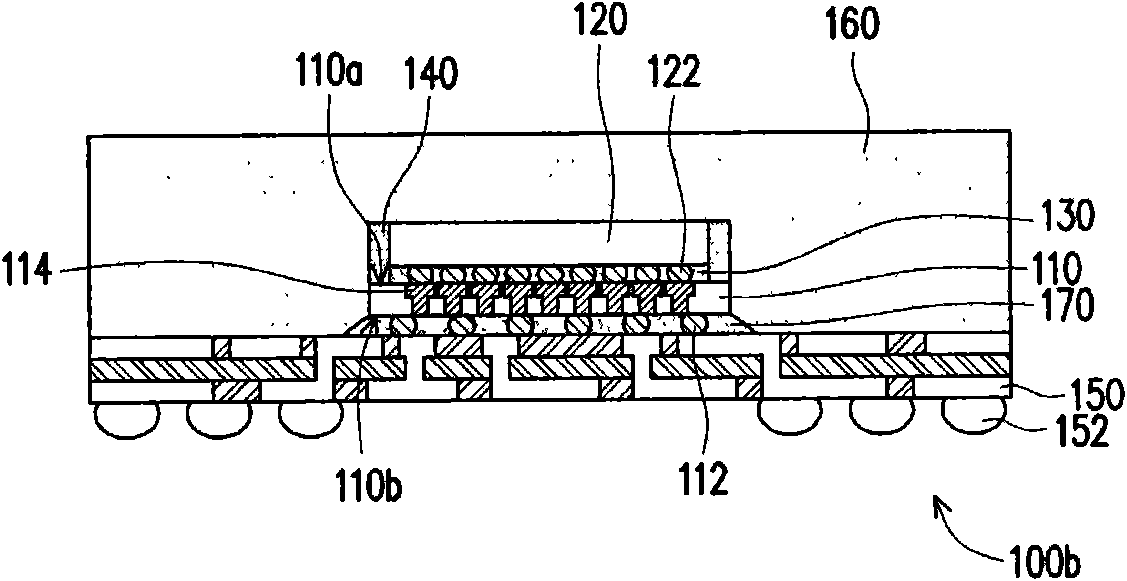

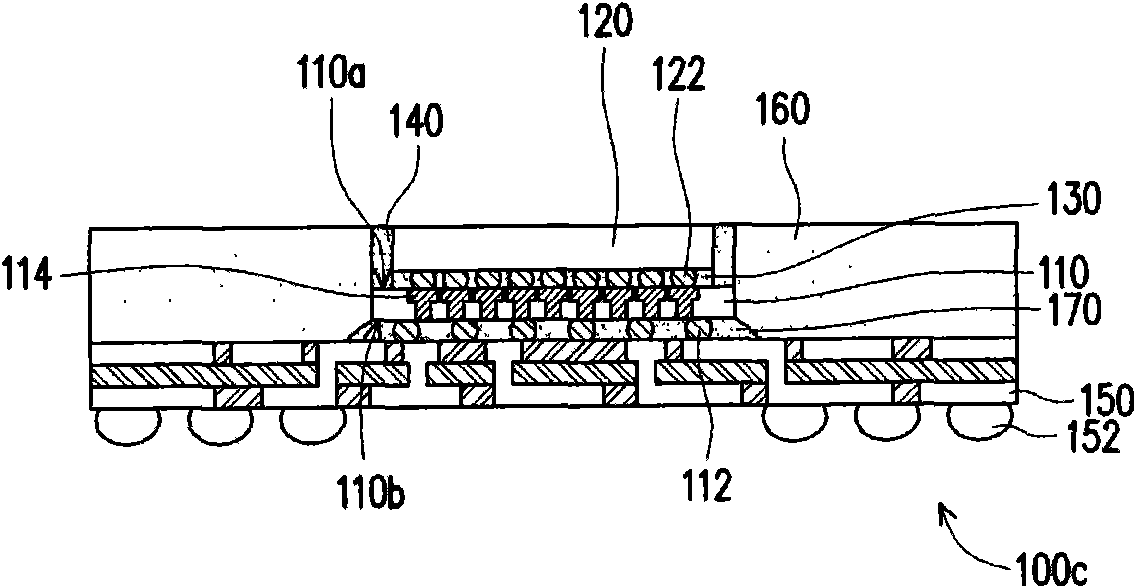

[0053] Figure 1A It is a schematic cross-sectional view of a package structure according to an embodiment of the present invention. Please refer to Figure 1A The packaging structure 100 a includes a semiconductor substrate 110 , a chip 120 , a first primer 130 and a first packaging compound 140 .

[0054]The semiconductor substrate 110 is, for example, a silicon substrate, which has an upper surface 110a, wherein the thickness of the semiconductor substrate 110 is less than 8 mils, such as less than 4 mils, or even 2 mils. The chip 120 is disposed on the upper surface 110 a of the semiconductor substrate 110 , and the bottom of the chip 120 has a plurality of first conductive bumps 122 . The first primer 130 is disposed between the semiconductor substrate 110 and the chip 120 to cover the first conductive bumps 122 . The first encapsulant 140 is disposed on the semiconductor substrate 110, and covers the side surfaces of the chip 120, the first primer 130, and the top surfa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More