A voltage level shifter

一种电压电平移位、电压域的技术,应用在使用介电元件的逻辑电路、电气元件、逻辑电路等方向,能够解决逻辑弱化、单一NWELL电压移位器不可用等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

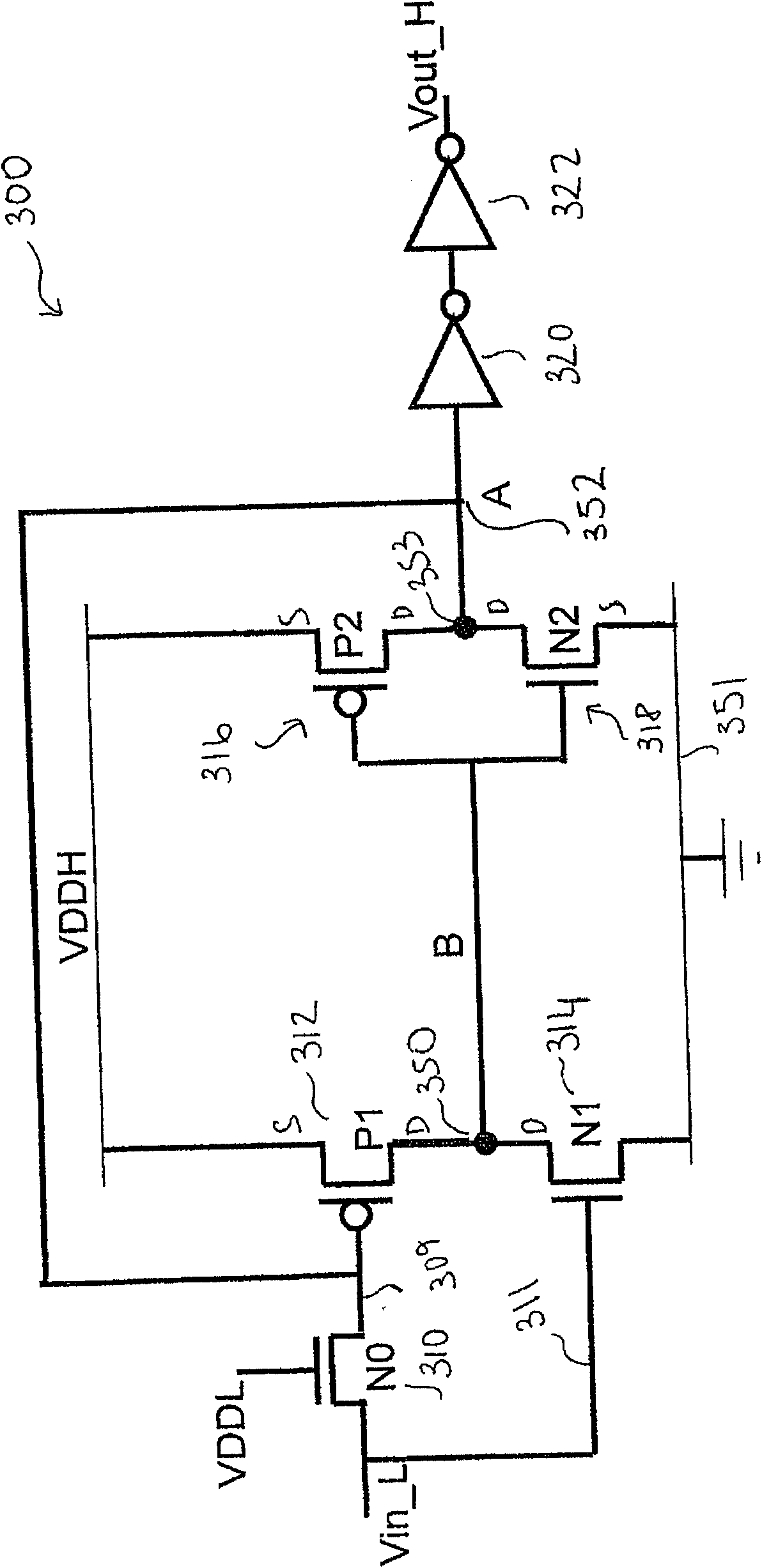

[0051] image 3 A design of a single well voltage level shifter suitable for a standard cell according to a first embodiment of the present invention is schematically illustrated. The circuit includes an NMOS pass transistor 310 and four transistors 312 , 314 , 316 and 318 connected between a high voltage domain VDDH (source voltage) and a ground voltage rail 351 . These four transistors include a first PMOS transistor 312 whose gate is connected to the output terminal of pass transistor 310 and whose source is connected to the high voltage domain VDDH. The drain of PMOS transistor 312 is connected to the drain of NMOS transistor 314 , and the source of NMOS transistor 314 is in turn connected to ground rail 351 .

[0052] The transistor pair including PMOS transistor 316 and NMOS transistor 318 collectively form an inverter circuit. The source of PMOS transistor 316 is connected to the high voltage domain VDDH, while the source of NMOS transistor 318 is connected to ground ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More