Electrostatic discharge (ESD) protection structure of integrated circuit

An ESD protection and integrated circuit technology, applied in the direction of circuits, electrical components, electric solid devices, etc., can solve problems such as ineffective energy consumption, and achieve the effect of improving anti-ESD performance and high reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

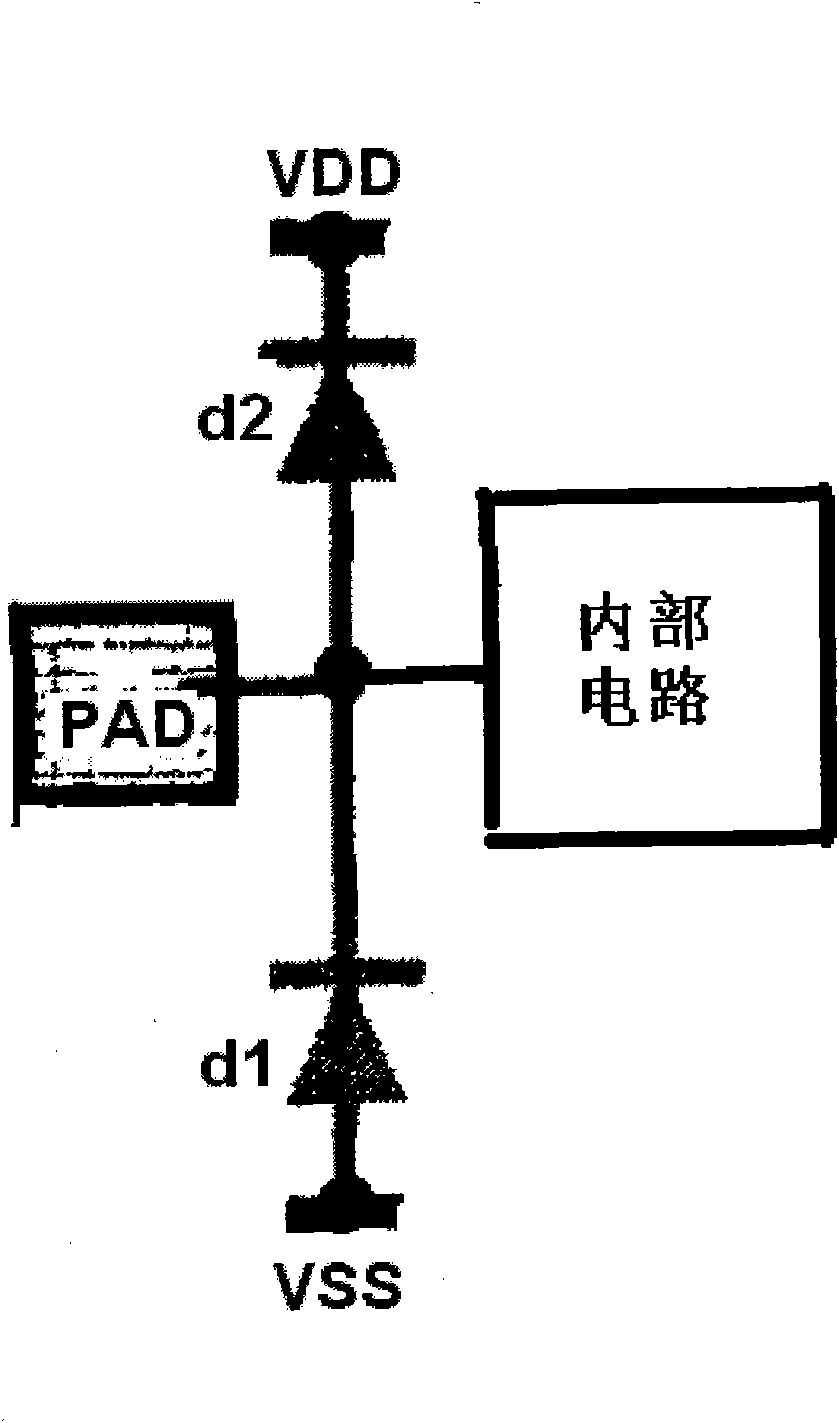

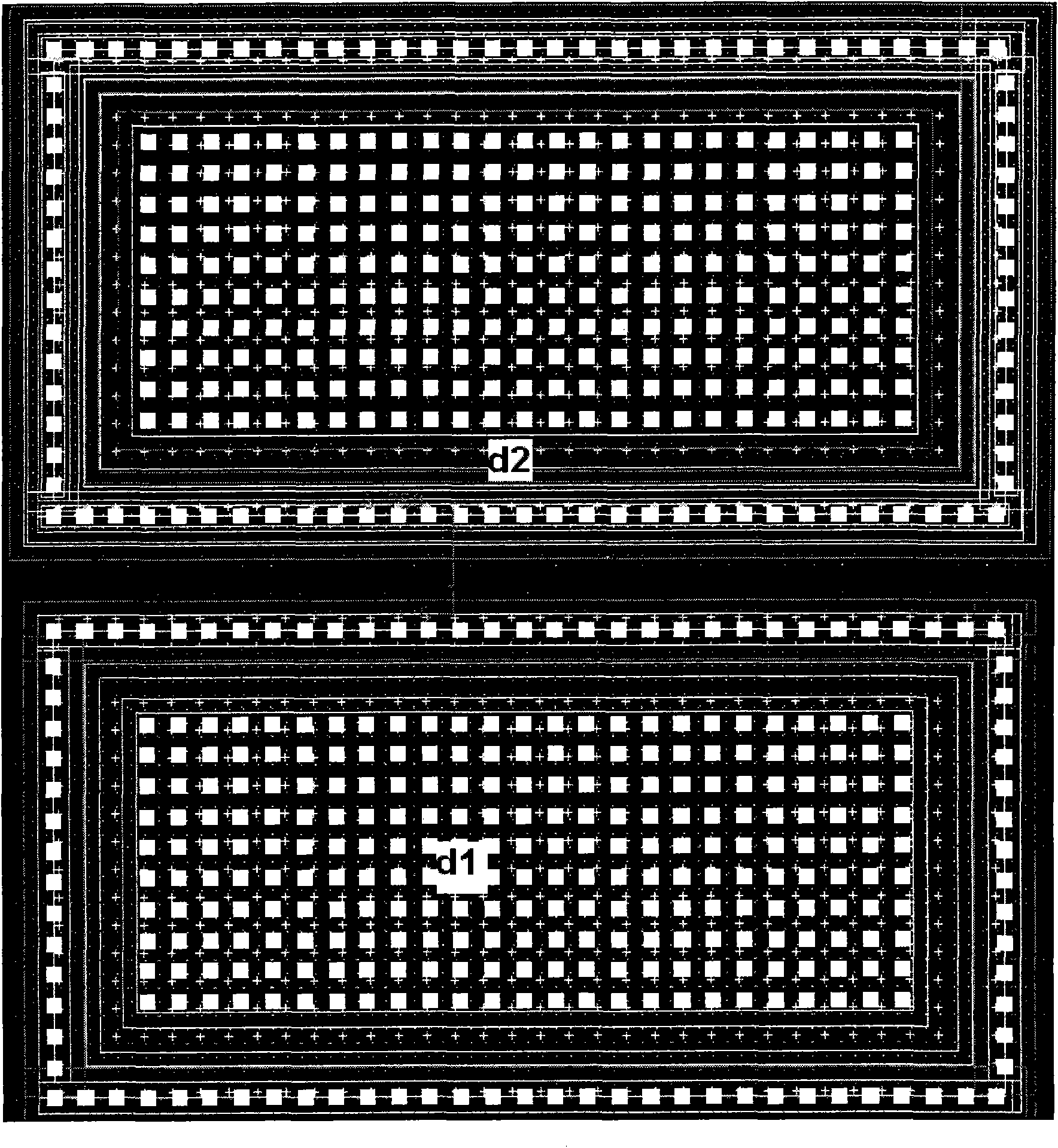

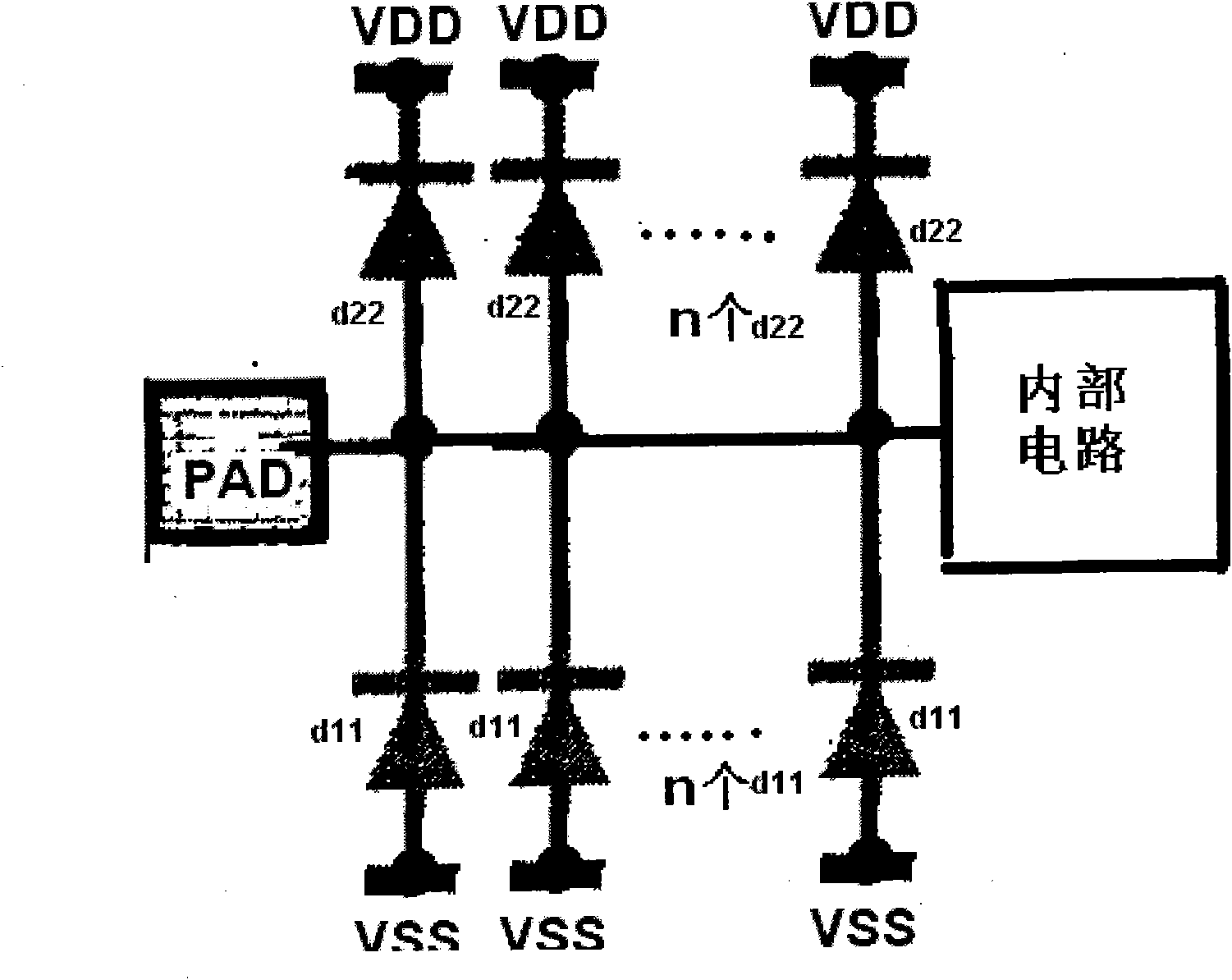

[0016] The ESD protection structure in the integrated circuit disclosed by the present invention is based on the prior art, and the prior art ( figure 1 In ), the PN junctions d1 and d2 formed as a whole are improved and designed, and they are designed as complex PN junctions placed between the internal circuit of the integrated circuit and the pad PAD without increasing the area occupied by the PN junction on the chip. These PN junctions form ESD protection for the internal circuits of integrated circuits in the form of semiconductor diodes.

[0017] like image 3 As shown, the complex PN junctions of the ESD protection structure of the present invention include a plurality of first-type PN junctions d11 and a plurality of second-type PN junctions d22, wherein the plurality of first-type PN junctions d11 are connected in parallel, and It may be a PN junction such as NSD / PSUB type, and the plurality of second type PN junctions d22 are also connected in parallel, which may be ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More