Failure positioning method of chip

A failure location and chip technology, applied in the direction of electronic circuit testing, etc., can solve the problems of difficult operation and difficulty for users, and achieve the effect of improving accuracy, speed and speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0010] The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

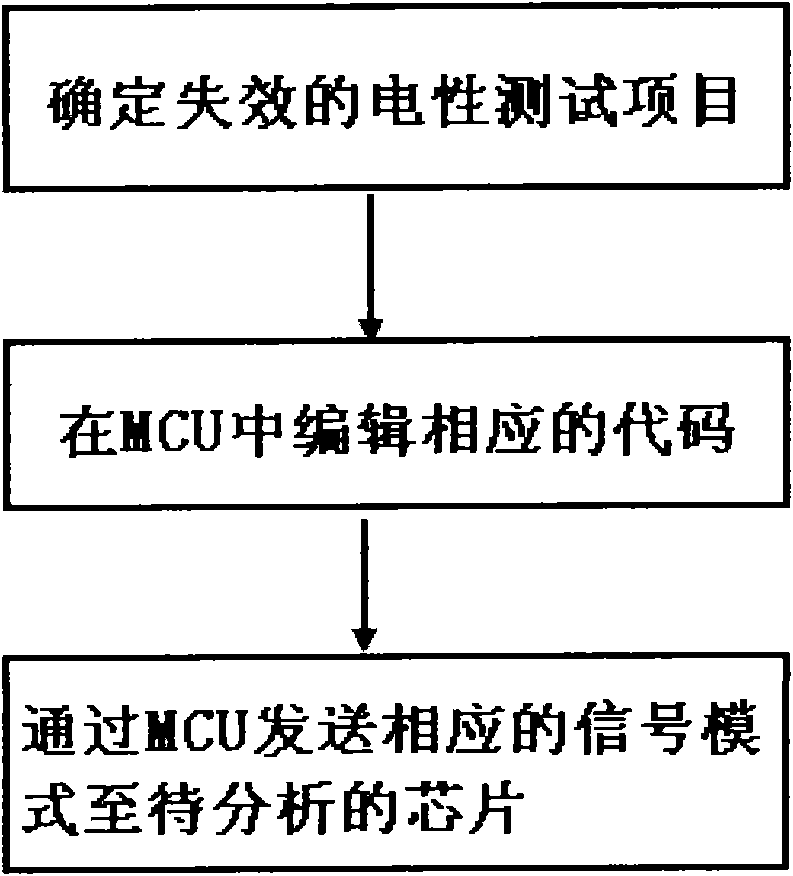

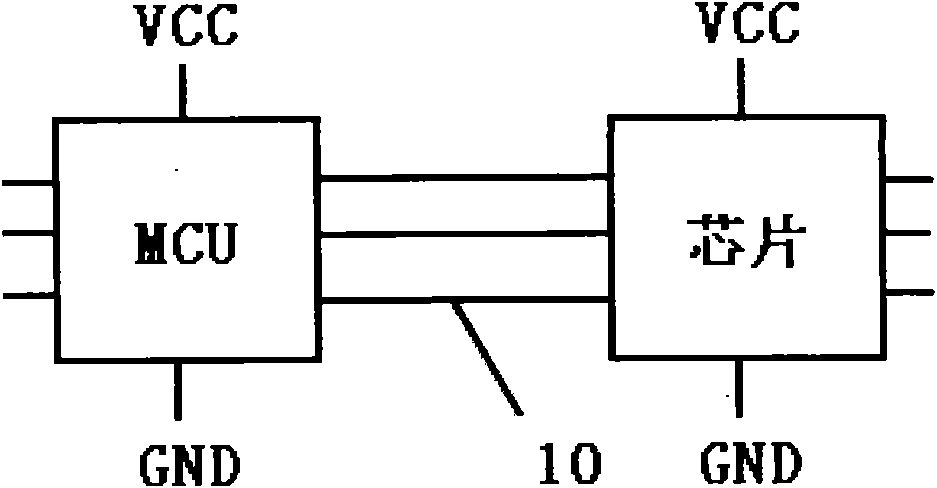

[0011] The so-called failure location of the chip refers to observing the hot spots of the normal chip and the failed chip under the Emmision Microscope (EMMI for short), finding the abnormal points through comparison, and further analyzing the root cause of the chip failure. Therefore, when performing failure analysis on the chip, it is first necessary to determine the failed electrical test items. Since many items on the chip can be tested, such as whether the pins on the chip are leaking, static power consumption, and dynamic power consumption, etc., so when performing Test items need to be specified before failure location. The chip itself contains several modules, and different modules control different functions on the chip. Therefore, when the signal at the input end is the same, the chip module after failure is different from the normal module....

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More