Time interpolation flash adc having automatic feedback calibration

An analog-to-digital converter and flash technology, applied in the direction of analog-to-digital converter, analog/digital conversion, code conversion, etc., can solve problems such as distortion and noise

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

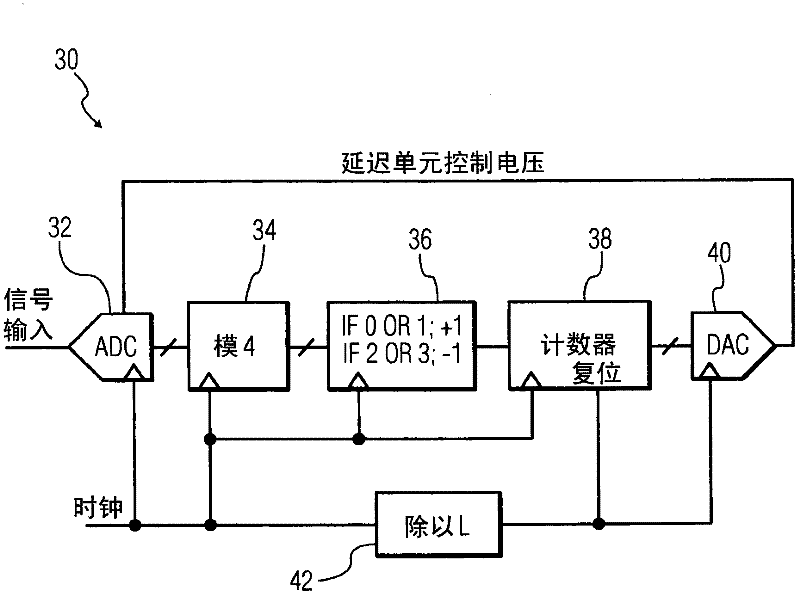

example 30

[0088] image 3 A functional block diagram of an example negative feedback calibration 30 according to one embodiment is shown. image 3Examples 30 include a flash ADC 32 according to any one of the disclosed M-bit flash ADC embodiments, such as figure 1 Combination of example 10 structure, modulo-4 event detector 34, counter increment / decrement unit 36, counter 38, digital / analog converter (DAC) 40 and divide-by-L (divide-by-L) reset unit 42.

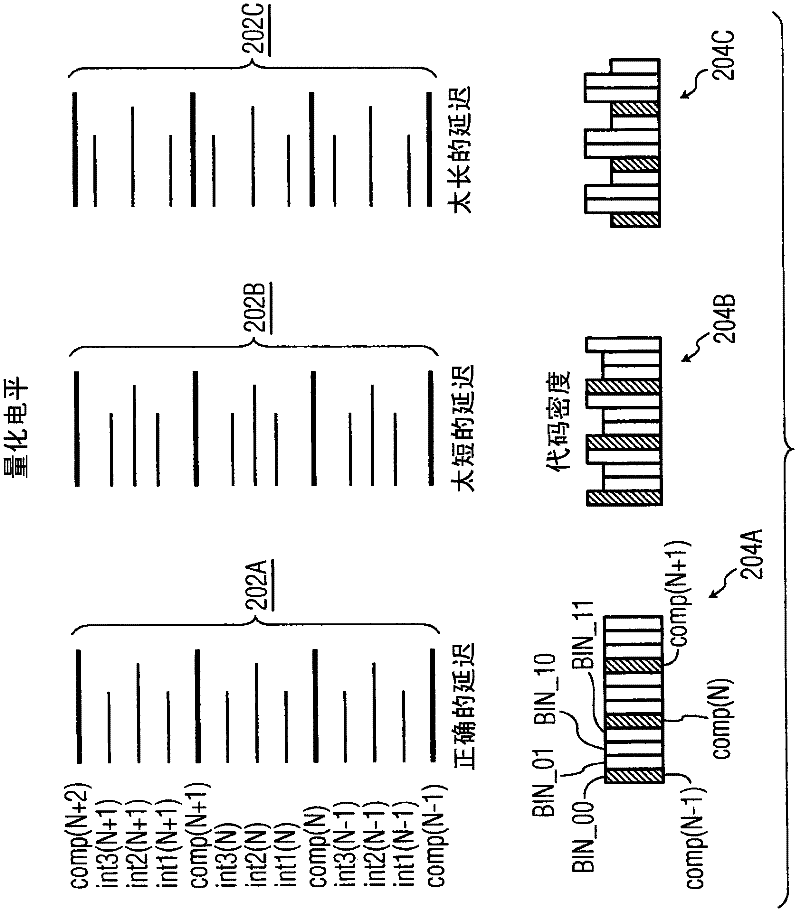

[0089] refer to image 3 , according to one aspect, the modulo-4 event detector 34 detects the operation of the binary output of the ADC 32, and in one example, if it is as figure 2 A binary 1 or a binary 0 sample, shown in item 204A, is in an outer bank such as BIN_00 or BIN_11 and the counter 36 is incremented. If it is a binary 2 or binary 3 sample, then in the inner bank such as BIN_01 or BIN_10 and the counter 36 is decremented.

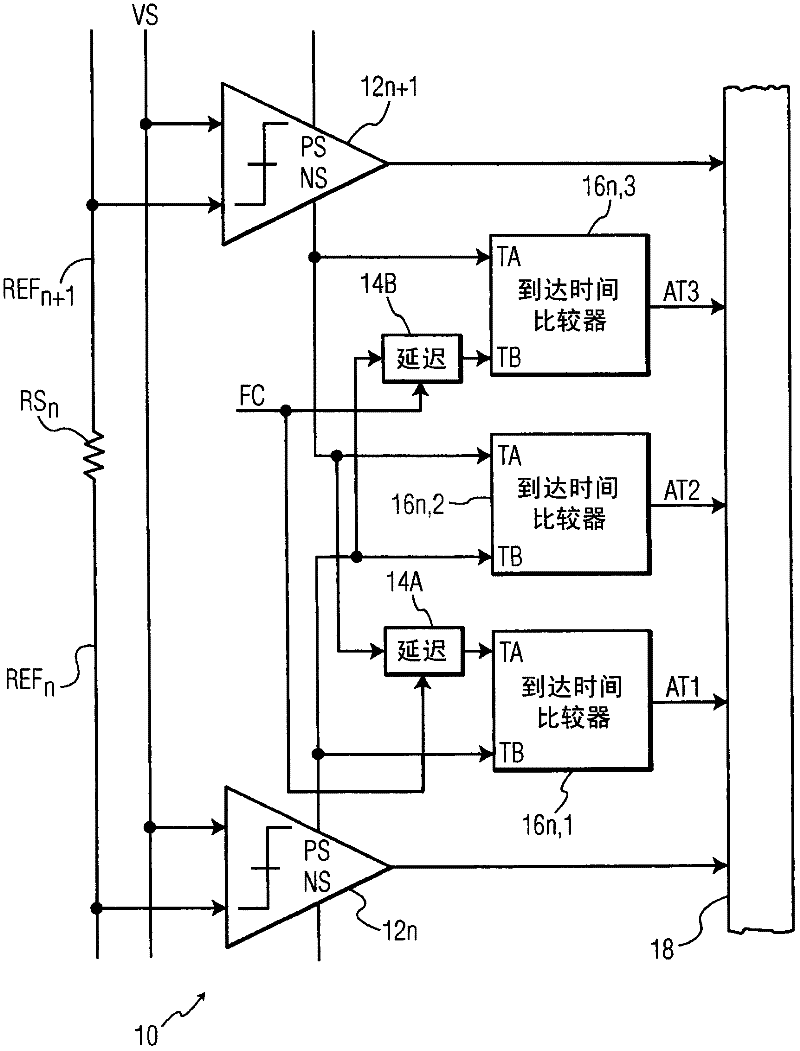

[0090] Feedback the output of the counter 36 to control the delay, e.g. figure 1 CD 14A and 14B...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More