Method and device for chip testing

A technology of chip testing and test vectors, applied in the direction of electronic circuit testing, etc., can solve the problems of low test efficiency, time-consuming and resource-consuming source files, etc., and achieve the effect of reducing memory consumption, reducing production time, and improving operating speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] In order to make the purpose, technical solutions and advantages of the embodiments of the present invention more clear, specific embodiments will be described in detail below with reference to the accompanying drawings.

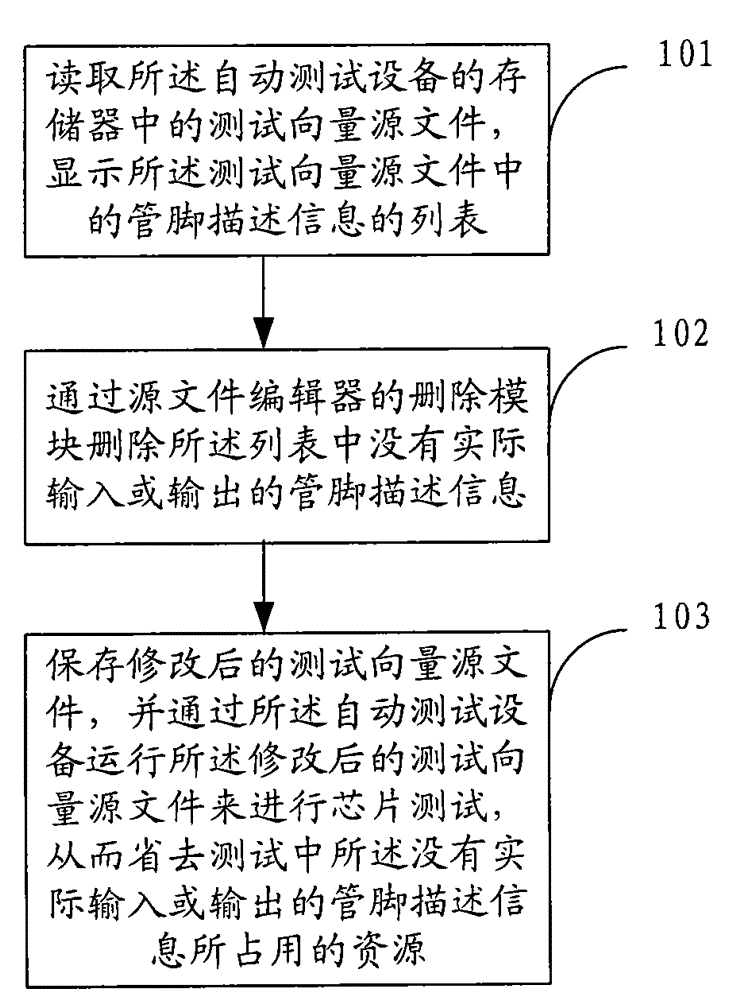

[0039] figure 1 The flow chart of the steps of the method provided by the embodiment of the present invention; as shown in the figure, the embodiment of the present invention provides a chip testing method for automatic test equipment, which includes the following steps:

[0040] Step 101, read the test vector source file in the memory of the automatic test equipment, and display the list of pin description information in the test vector source file;

[0041] Step 102, delete the pin description information that has no actual input or output in the list through the deletion module of the source file editor;

[0042] Step 103, save the modified test vector source file, and run the modified test vector source file through the automatic test equipment t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More