Field programmable gate array loading method and device

A gate array and programming logic technology, applied in the field of FPGA, can solve the problems of increased loading time of FPGA, increased startup time of single board, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] Hereinafter, the present invention will be described in detail with reference to the drawings and examples. It should be noted that, in the case of no conflict, the embodiments in the present application and the features in the embodiments can be combined with each other.

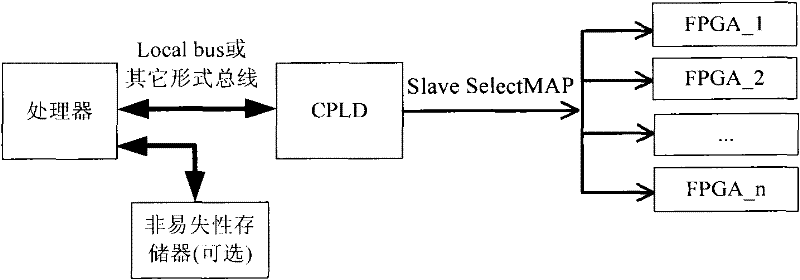

[0017] The processor loads the FPGA through the CPLD, and the FPGA is loaded using the Slave SelectMAP method. Embodiments of the present invention are implemented on this basis.

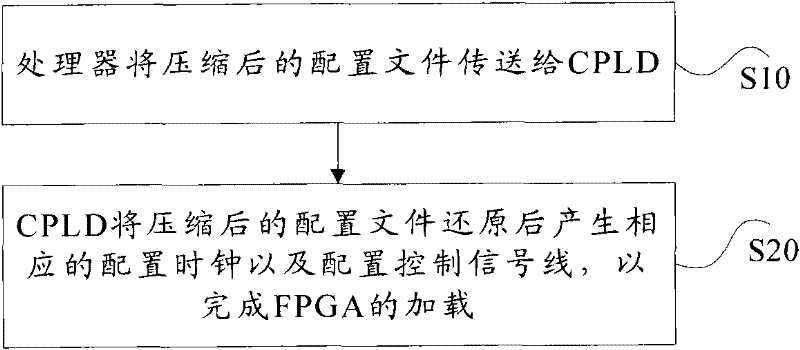

[0018] figure 2 It is a flow chart of the FPGA loading method according to an embodiment of the present invention, comprising the following steps:

[0019] Step S10, the processor transmits the compressed configuration file to the CPLD;

[0020] In step S20, the CPLD restores the compressed configuration file to generate corresponding configuration clocks and configuration control signal lines, so as to complete the loading of the FPGA.

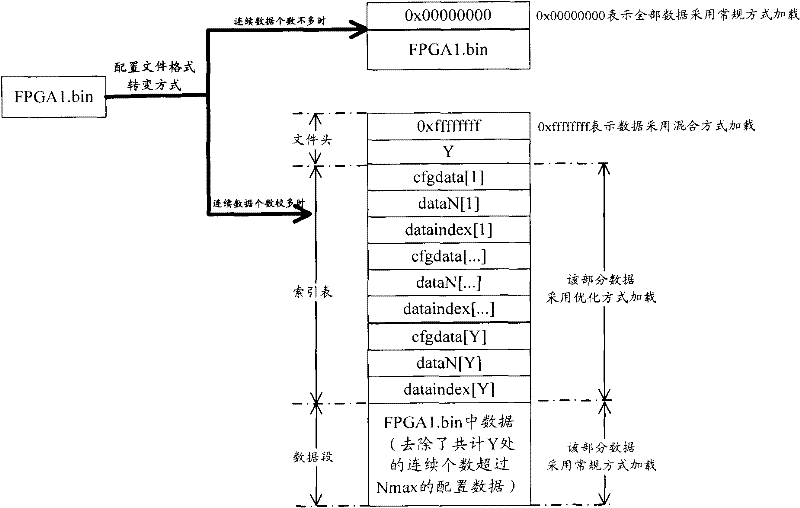

[0021] In the related art, the configuration file of the FPGA is directly transm...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More