Die size semiconductor element package and manufacturing method thereof

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problem that the packaging cost cannot be effectively reduced, and achieve material cost saving, process simplification, and quality improvement. The effect of competitiveness on rate and manufacturing cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

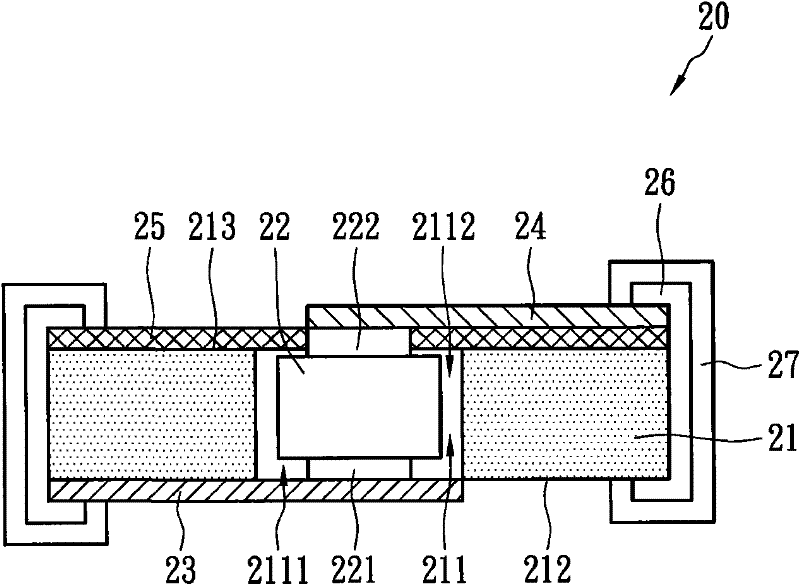

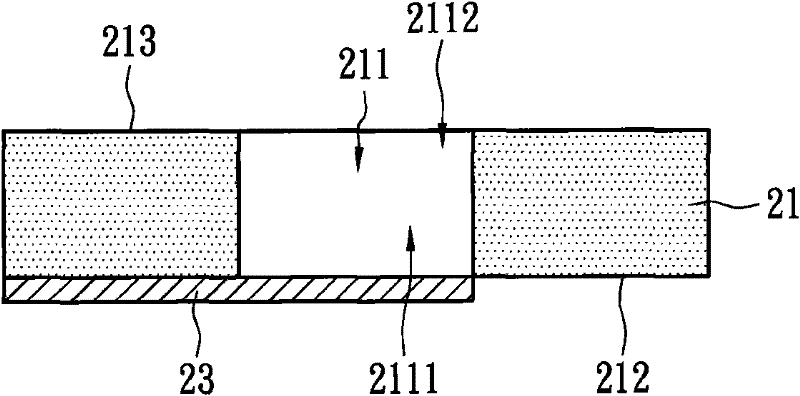

[0043] figure 2 It is a schematic cross-sectional view of a die-sized semiconductor device package according to an embodiment of the present invention. A die size semiconductor device package 20 includes a die 22 , an insulating substrate 21 having a through hole 211 , a first metal layer 23 , a second metal layer 24 and an insulating layer 25 . The first metal layer 23 is disposed on the first surface 212 of the insulating substrate 21 and the first opening 2111 of the through hole 211 . The insulating layer 25 covers the second surface 213 of the insulating substrate 21 and surrounds the second opening 2112 of the through hole 211 . The second metal 24 is disposed on the insulating layer 25 and the second opening 2112 . The die 22 is disposed in the through hole 211 and includes a first electrode 221 and a second electrode 222 . The first electrode 221 is electrically connected to the first metal layer 23 , and the second electrode 222 is electrically connected to the se...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More