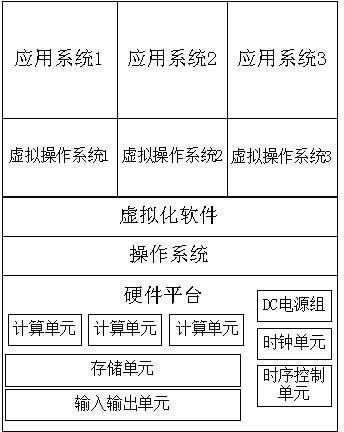

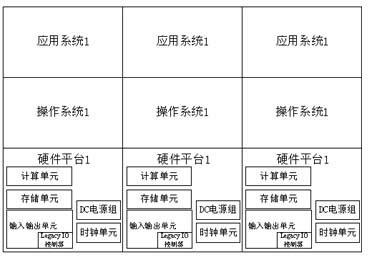

A timing control method for physical multi-partition computer architecture

A timing control and system structure technology, applied in the direction of combining various digital computers, generating/distributing signals, etc., can solve problems such as multiple system failures and affect system reliability, and achieve the effect of ensuring reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

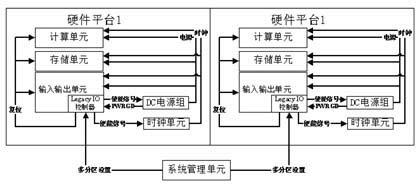

[0028] Legacy IO controllers use two different timing control methods when the system is divided into multiple independent multiprocessor systems or coupled into a complete computer system:

[0029] Timing Control for Multiprocessor Systems:

[0030] 1. Set the Legacy IO controller of the partition through the system management unit, and activate the Legacy IO controller of each partition;

[0031] 2. Each partition can be turned on and off independently. After a partition receives the power-on command, the Legacy IO controller sends an enable signal to the DC power supply group of the partition. Power supply, and feedback Power good signal to Legacy IO controller;

[0032] 3. The Legacy IO controller sends an enable signal to the partition clock unit, and this clock unit provides clocks to the computing units, storage units, and input and output units in the partition;

[0033] 4. After the Legacy IO controller waits until the system clock is stable, it resets the computing...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More