Hierarchical Block Irregular Low Density Check Code Decoder and Decoding Method

A low-density check code and decoder technology, which is applied in the field of layered and block irregular low-density check code decoders and decoding, to achieve the effects of eliminating pipeline conflicts, small resource consumption, and saving hardware resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] The embodiments of the present invention are described in detail below in conjunction with the accompanying drawings: this embodiment is implemented on the premise of the technical solution of the present invention, and detailed implementation methods and specific operating procedures are provided, but the protection scope of the present invention is not limited to the following the described embodiment.

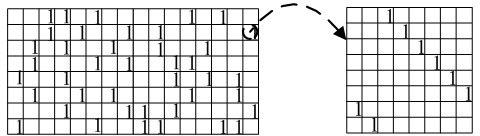

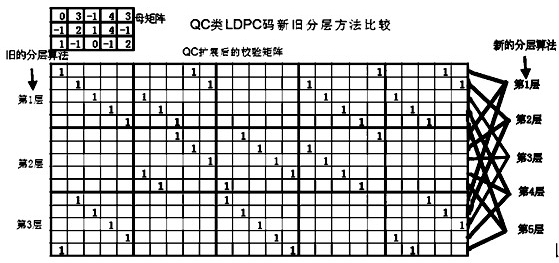

[0051] Such as figure 1 Shown is the mother matrix of the quasi-cyclic LDPC code and its extension method used by a decoder with a degree of parallelism k. The size of the codeword to be constructed is m*n, and the size of the corresponding mother matrix is (m / k)*(n / k), and each element in the mother matrix is expanded into a k*k matrix. The 0 in the mother matrix is expanded into a k*k zero matrix; the 1 in the mother matrix is expanded into a cyclic shift form of a k*k unit matrix. In the figure, the left side is the mother matrix diagram, and the righ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More