Preparation method of metal-oxide-semiconductor field-effect transistor with silicon-on-nothing (SON) structure

A gate region and active region technology, which is applied in the field effect transistor manufacturing process and the MOSFET manufacturing process field, can solve the problems of complex process, affecting yield and high cost, and achieve simple process, production cost saving, and yield improvement. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

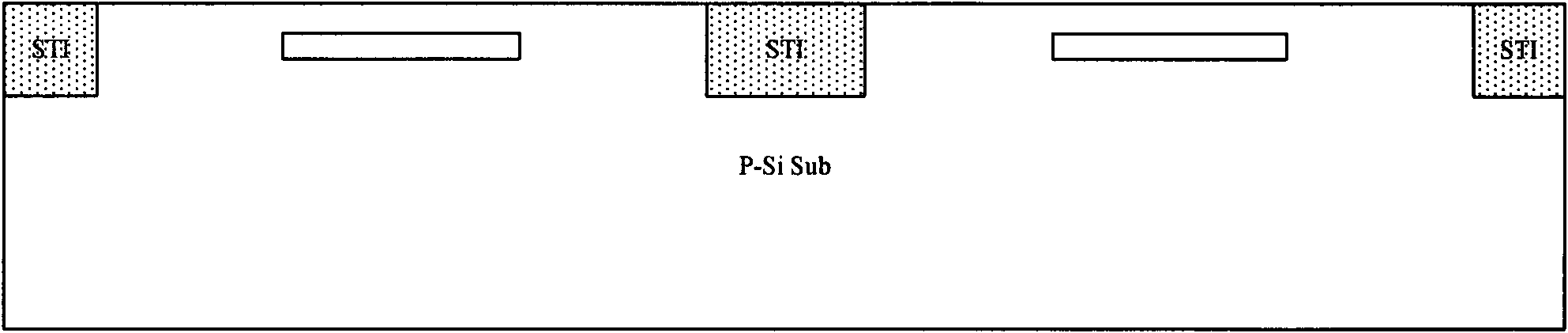

[0017] The device structure of the present invention will be further described below in conjunction with the accompanying drawings, which are not drawn to scale for the convenience of illustration.

[0018] Please see Figure 1-4 , using the preparation method of the present invention, taking a CMOS device as an example, comprises the following steps:

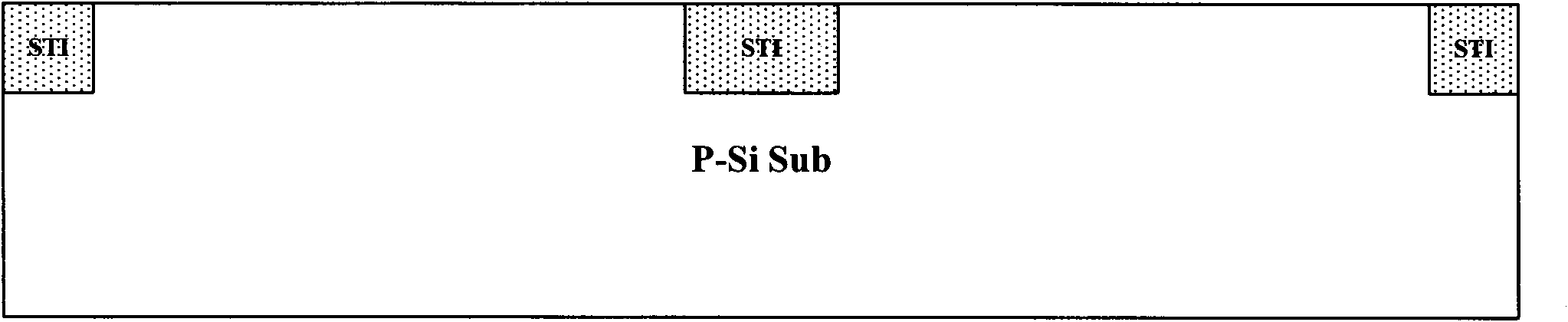

[0019] Step 1, such as figure 1 As shown, the active region is formed on the bulk silicon substrate (p-type Si substrate) by shallow trench isolation technology, which is exactly the same as the traditional bulk silicon CMOS process.

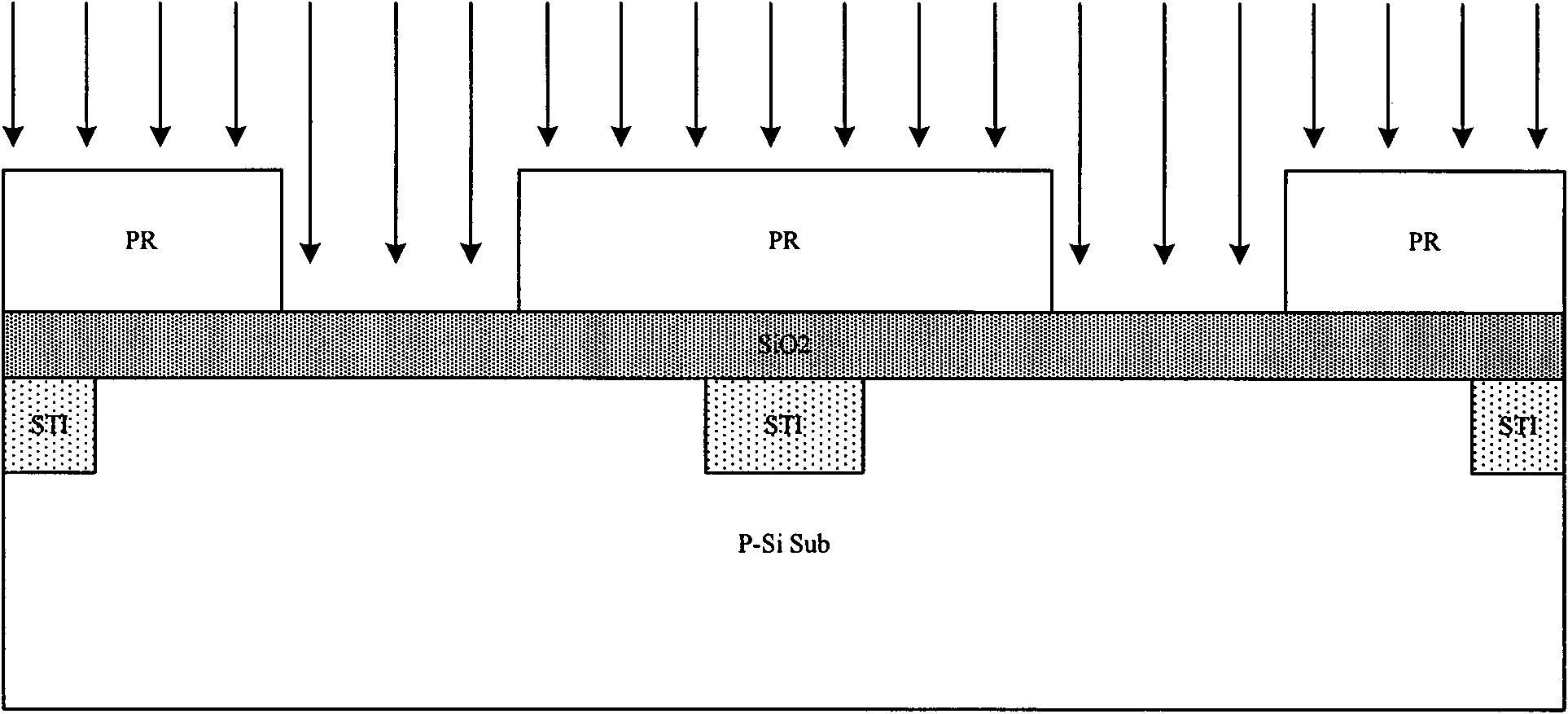

[0020] Step 2, forming a layer with a thickness on the active region by thermal growth or LPCVD Above SiO 2 The buffer layer.

[0021] Step three, such as figure 2 As shown, using a photolithography plate for the gate region, the photoresist with the opposite polarity to the photoresist used in the photolithography process for the gate region is used for photolithography, so that the posit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More