Method for making fine pattern on semiconductor device

A technology of fine patterns and production methods, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as difficult to realize, low production efficiency, complex SADP technology, etc., to achieve accurate definition and improve production efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] In order to make the object, technical solution, and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the accompanying drawings and examples.

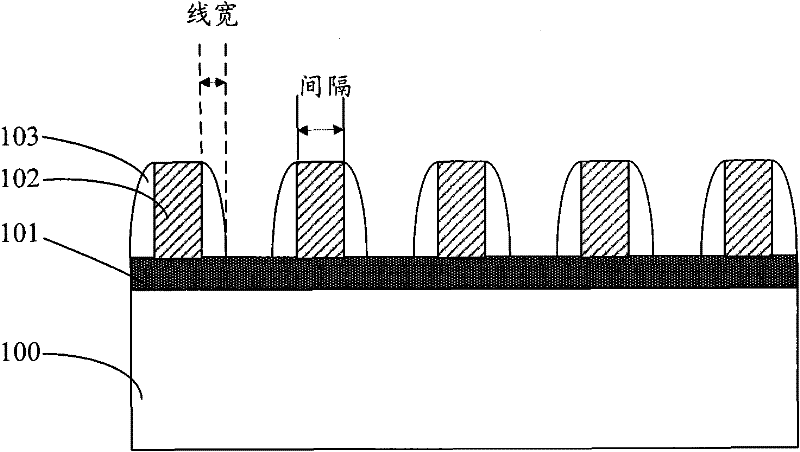

[0036] The present invention adopts simplified SADP technology to make the method flow diagram of fine pattern as figure 2 As shown, it includes the following steps, which are combined below Figure 2a to Figure 2e Be explained.

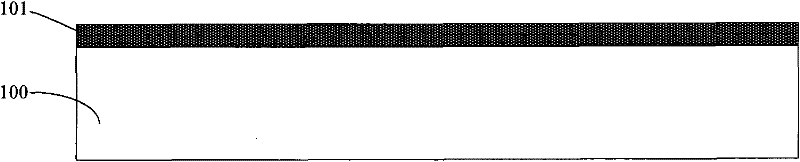

[0037] Step 21, see Figure 2a , deposit an etching target layer 201 on the semiconductor substrate 200 .

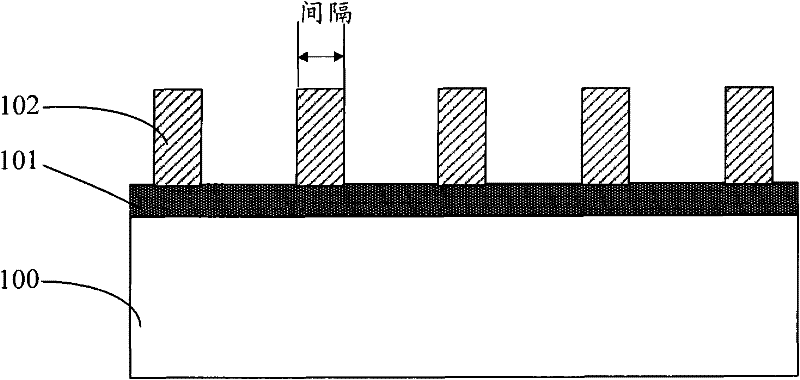

[0038] Step 22, see Figure 2b , sequentially depositing an organic layer 202, a first hard mask layer 203, and coating a photoresist layer (not shown in the figure) on the surface of the etching target layer 201, and exposing, developing and patterning the photoresist layer, patterning The gaps between the photoresist layers are used to define intervals of fine patterns; using the patterned photoresist layer as a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More