Anti-interference chip packaging structure

A chip packaging structure and chip technology, which is applied in the field of chip packaging structure and new chip packaging structure, can solve the problems of reducing the working stability of electrical equipment, the chip is easily affected by electromagnetic radiation, and disturbing the operating frequency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] The preferred embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings, so that the advantages and features of the present invention can be more easily understood by those skilled in the art, so as to define the protection scope of the present invention more clearly.

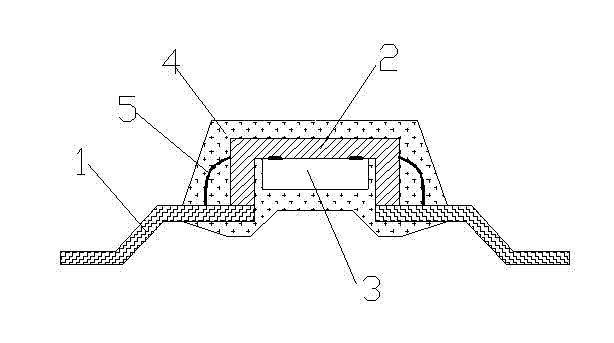

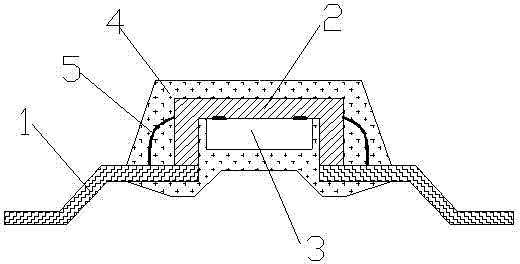

[0015] figure 1 It is a structural schematic diagram of an anti-jamming chip packaging structure in an embodiment of the present invention; the anti-jamming chip packaging structure mainly includes a lead frame 1, a substrate 2, a chip 3 and a package body 4, and it is characterized in that the substrate 2 adopts The "concave" shape structure is placed upside down on the lead frame 1 during packaging, and the chip 3 is flipped on the inner top of the substrate 2, and the two are electrically connected by soldering process.

[0016] In the anti-interference chip packaging structure mentioned in the present invention, glue is used to bond between t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com