Method for testing SOC (System On Chip) based on reference vector and bit mask

A technology of reference vectors and testing methods, applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc., can solve the problem of low compression rate and achieve the effect of high compression efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

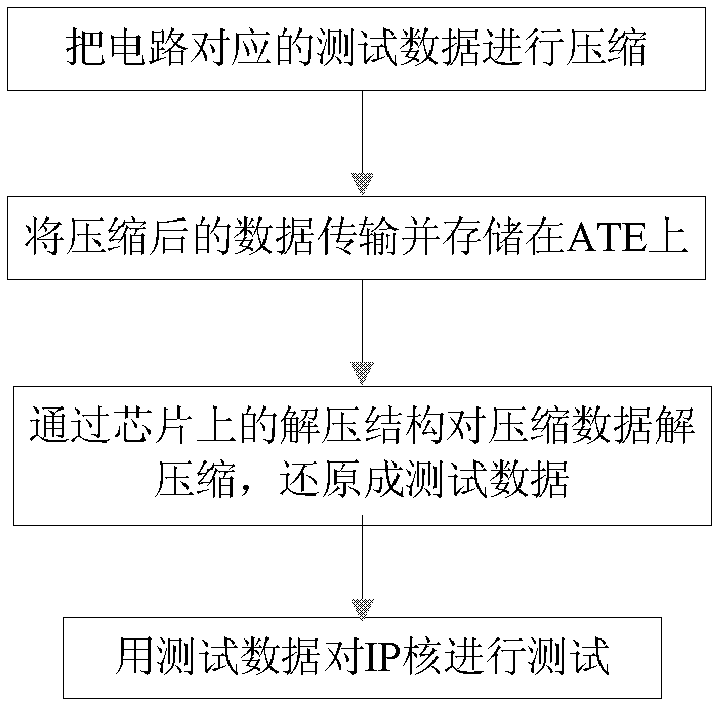

[0040] Specific implementation mode one: combine figure 1Describe this embodiment, the specific steps of the SOC test method based on reference vector and bitmask in this embodiment are:

[0041] Step 1: Compress the test data corresponding to the circuit;

[0042] Step 2: transmit and store the compressed data on ATE;

[0043] Step 3: Decompress the compressed data through the decompression structure on the chip, and restore it to test data;

[0044] Step 4: Test the IP core with test data.

[0045] The compression process of Step 1 is as follows:

[0046] Step 11: arrange the test data corresponding to the circuit in the form of multiple scan chains to obtain multiple test segments;

[0047] Step 1 and 2: Carry out group division for all test segments, and then select the test segment with high frequency in the group after division according to the capacity of the allocated dictionary in the hardware as a dictionary entry;

[0048] Step 13: According to the frequency of...

specific Embodiment approach 2

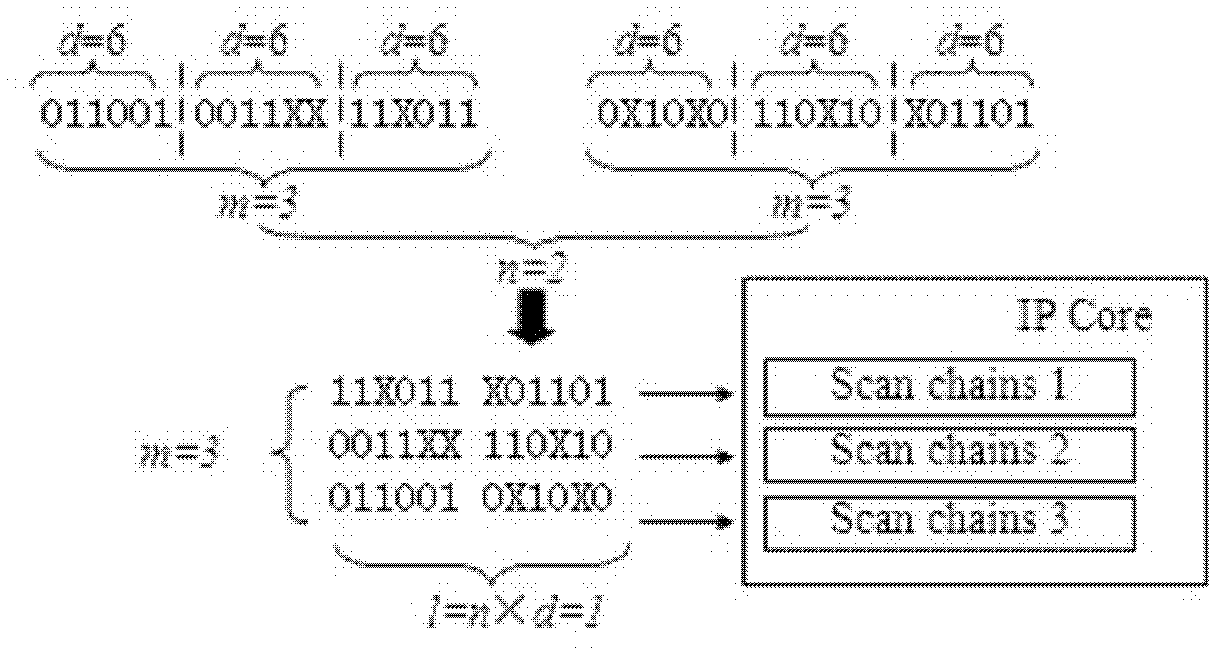

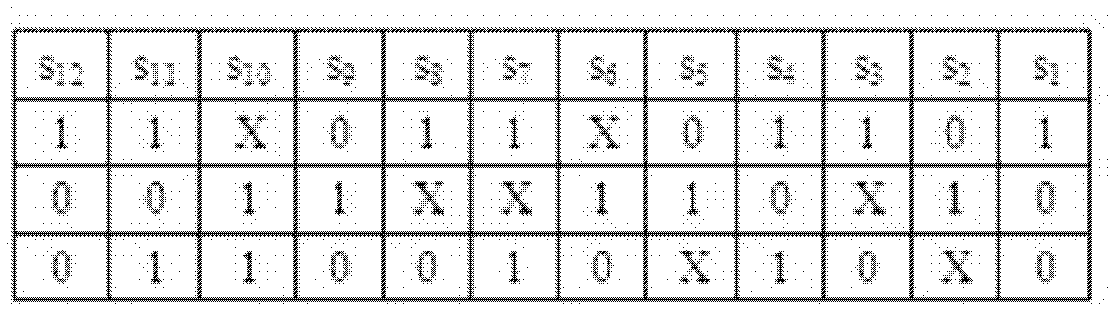

[0052] Specific embodiment 2: the feature of this embodiment is that in step one of specific embodiment 1, the method of arranging the test data corresponding to the circuit into test segments according to the form of multiple scan chains is: set the test data corresponding to the circuit as a test set T D , consisting of n vectors, respectively t 1 , t 2 , t 3 ,...,t n , the number of scan chains in the IP core is m, each test vector is divided into m groups on average, and each group contains d-bit data, if the number of bits of each test vector is Ntotal, d=Ntotal / m, if a certain group of data If the length is less than d, fill it up with the uncertain bit "X", combine the jth data of all test vectors together to form a scan chain, j=1, 2,..., m, the kth bit of all scan chains grouped together to form the kth test segment.

[0053] When the test set T D When n=2, m=3, and d=6, the process of arranging test segments in the form of multiple scan chains is as follows f...

specific Embodiment approach 3

[0054] Specific embodiment three: the characteristic of this embodiment is, the method for carrying out group division to test segment in the step one two of specific embodiment one is:

[0055] Step a: establish an undirected graph G=(V, E) for the test segment, wherein V is a vertex set, and E is an edge set; the test segment without an edge in the undirected graph is encoded using a bit mask, so that the test segment connected to vertices with edges;

[0056] Step b: Search for the point with the largest degree in the undirected graph, if the largest point is unique, execute step d; if the largest point is not unique, execute step c;

[0057] Step c: Select the vertex with the least irrelevant bits X as the point with the largest current degree;

[0058] Step d: use all the vertices connected to the current maximum degree vertex to establish a subgraph H;

[0059] Step e: Search the subgraph H, obtain the vertex pair with the most common neighbors in the subgraph H, if no...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More