Method and device for synchronizing clocks

A clock synchronization and master clock technology, applied in the field of communication, can solve problems such as low synchronization accuracy, uncertain bidirectional path, asymmetry, etc., to achieve the effect of eliminating uncertainty and asymmetry, and solving low synchronization accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

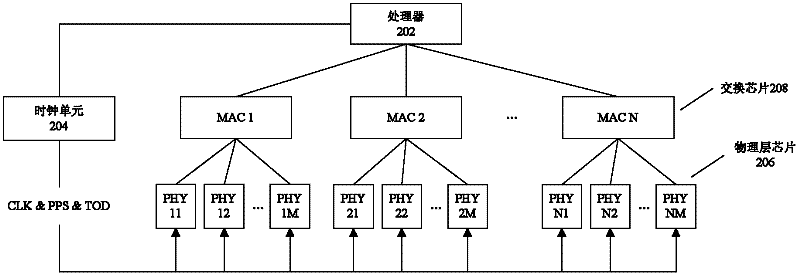

[0027] figure 1 It is a preferred structural diagram of a clock synchronization device according to an embodiment of the present invention, which includes: a processor 202, a clock unit 204, and a physical layer chip 206. Preferably, the clock synchronization device in this embodiment may also include: a switch Chip 208 .

[0028] The functions and interrelationships of each module in the above clock synchronization device will be described respectively below.

[0029] 1) Physical layer chip (PHY) 206: In addition to completing the physical layer codec function, it also realizes functions such as IEEE 1588 message detection and time stamp generation. Time synchronization with the main clock is realized by receiving the second pulse signal and the TOD signal output by the clock unit.

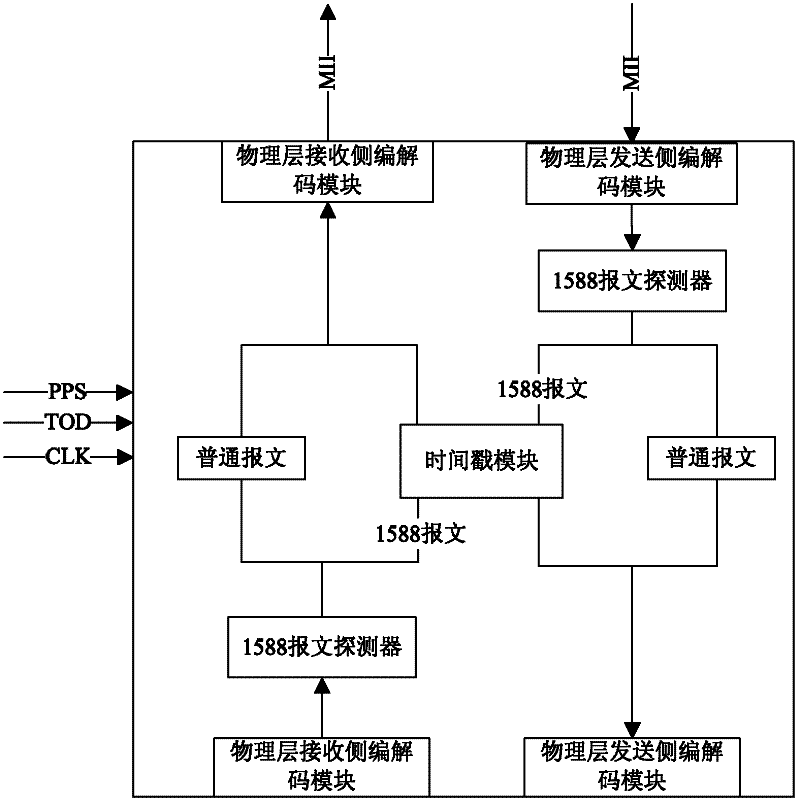

[0030] The present invention provides a preferred physical layer chip, such as figure 2As shown, the physical layer chip (PHY): includes a codec module, a 1588 message detector and a time sta...

Embodiment 2

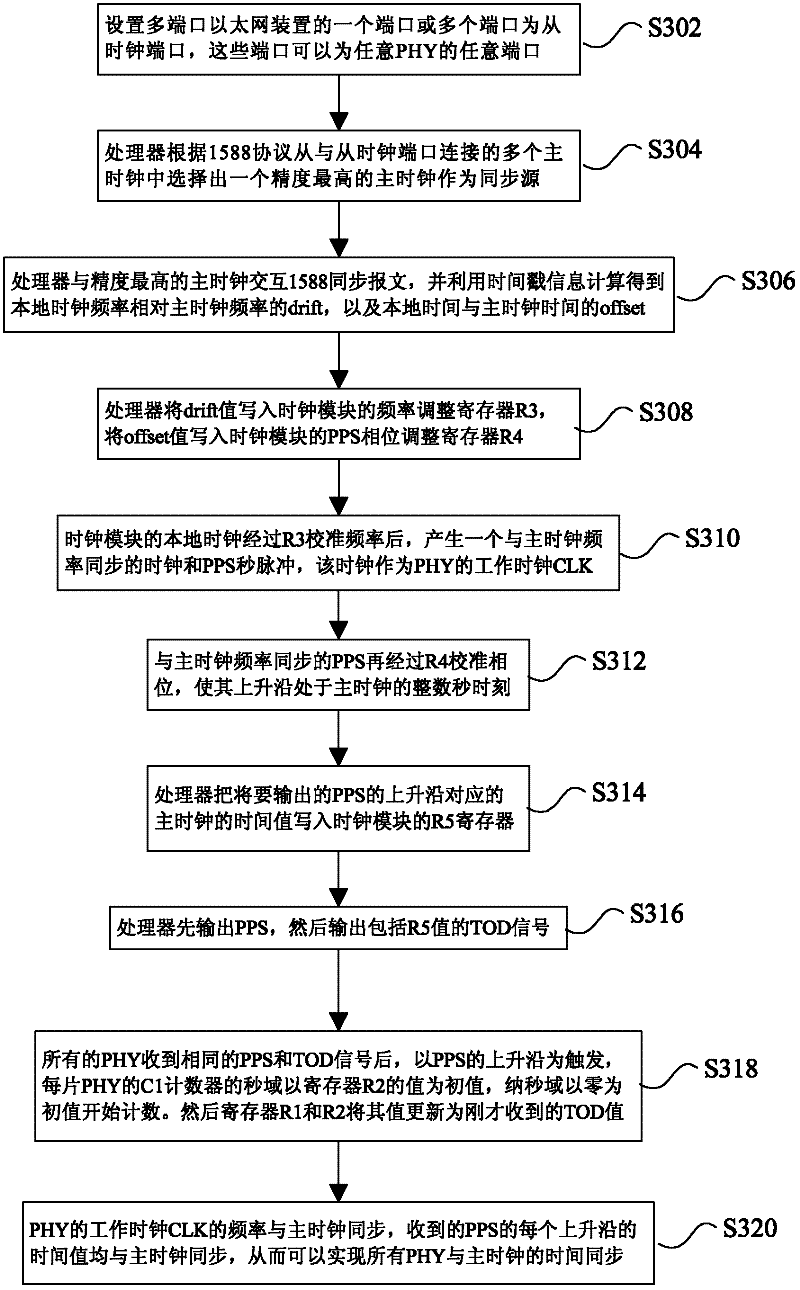

[0052] exist Figure 1-Figure 2 On the basis of the clock synchronization device shown, the present invention also provides a clock synchronization method, such as Figure 4 As shown, it includes: .

[0053] S402, calculating frequency drift and time offset between the local clock and the master clock;

[0054] S404, use the frequency drift to calibrate the local clock, and use the time offset to calibrate the second pulse signal;

[0055] S406, using the calibrated local clock, the calibrated second pulse signal, and the time value TOD of the rising edge of the calibrated second pulse signal to set the working clock and time stamp module in the physical layer chip Time is synchronized.

[0056] In the technical solution provided by this embodiment, use the calibrated local clock and the calibrated second pulse signal and TOD to synchronize the working clocks in multiple physical layer chips, so that the frequency of the working clock CLK of the physical layer chip is the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More