Memory element and flash memory array reading and operating method and structures thereof

A memory element and memory array technology, applied in static memory, read-only memory, information storage, etc., can solve the problems of affecting the continuous range, reading errors, shortening the length of word lines, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The content disclosed in the present invention provides many different embodiments or examples, and different technical features applied in different embodiments can be understood after reading this specification. The content and practice of specific embodiments will be described below to simplify the disclosure of the present invention. Of course, these examples are not intended to limit the present invention. In addition, in different embodiments, the present invention may reuse the same index numbers and / or words. The purpose of using these reference numbers and / or words is to simplify and clarify the present invention, but not to indicate that different embodiments and / or disclosed structures must have the same features.

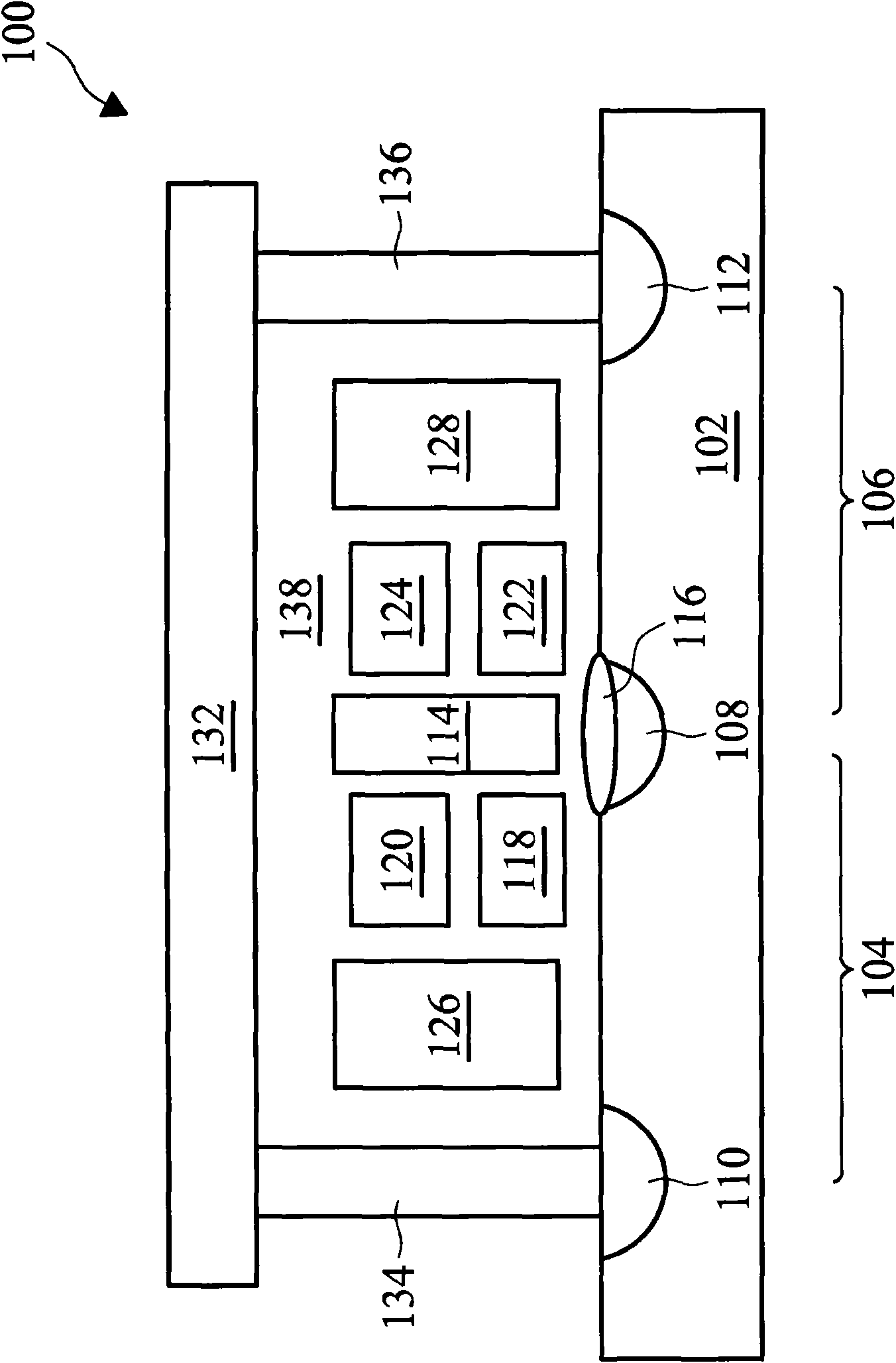

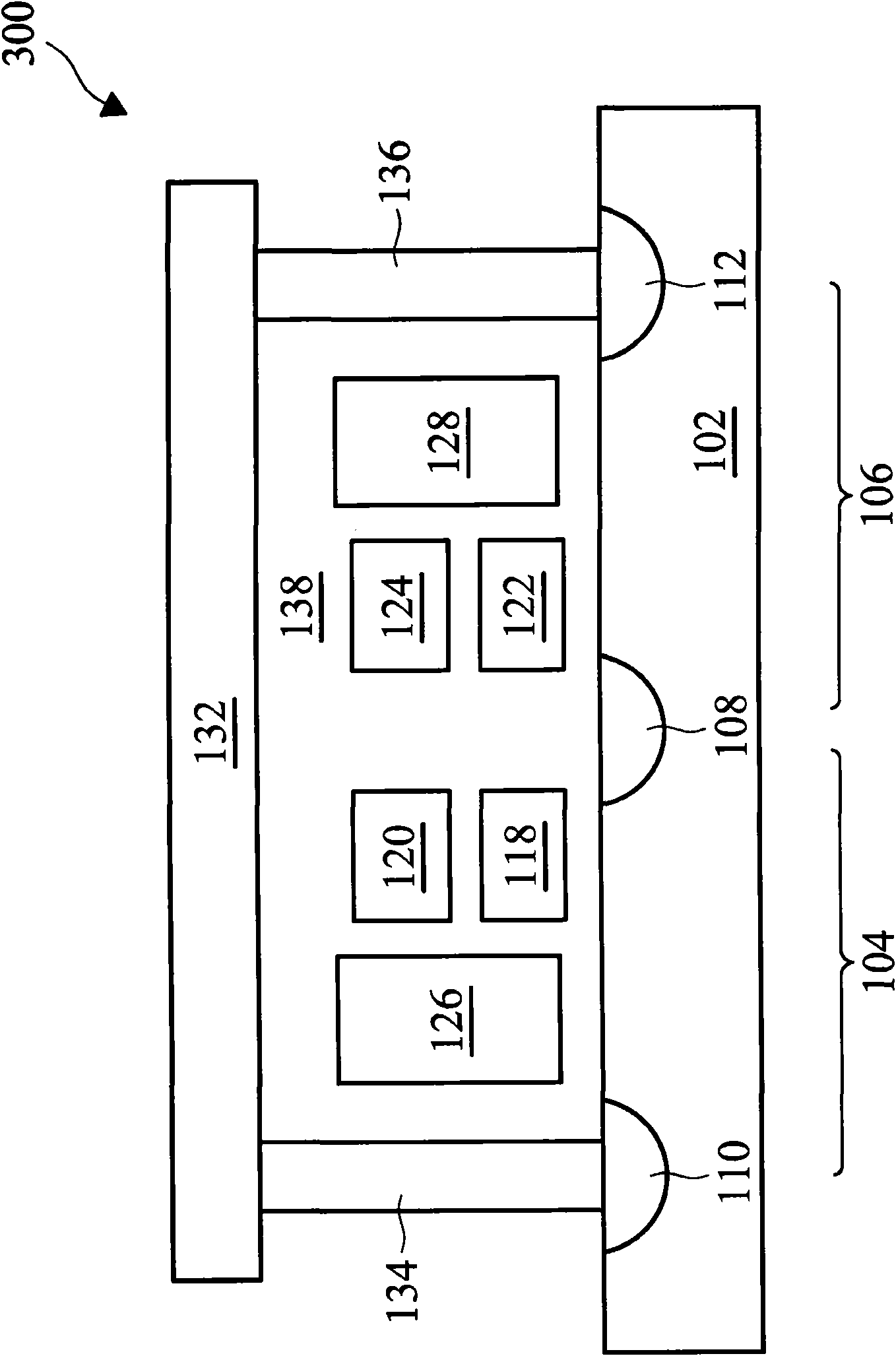

[0042] figure 1 A cross-sectional view of a flash memory structure 100 is shown according to an embodiment of the present invention. The flash memory structure 100 includes a semiconductor substrate 102 . In the disclosed embodiment, the semic...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com