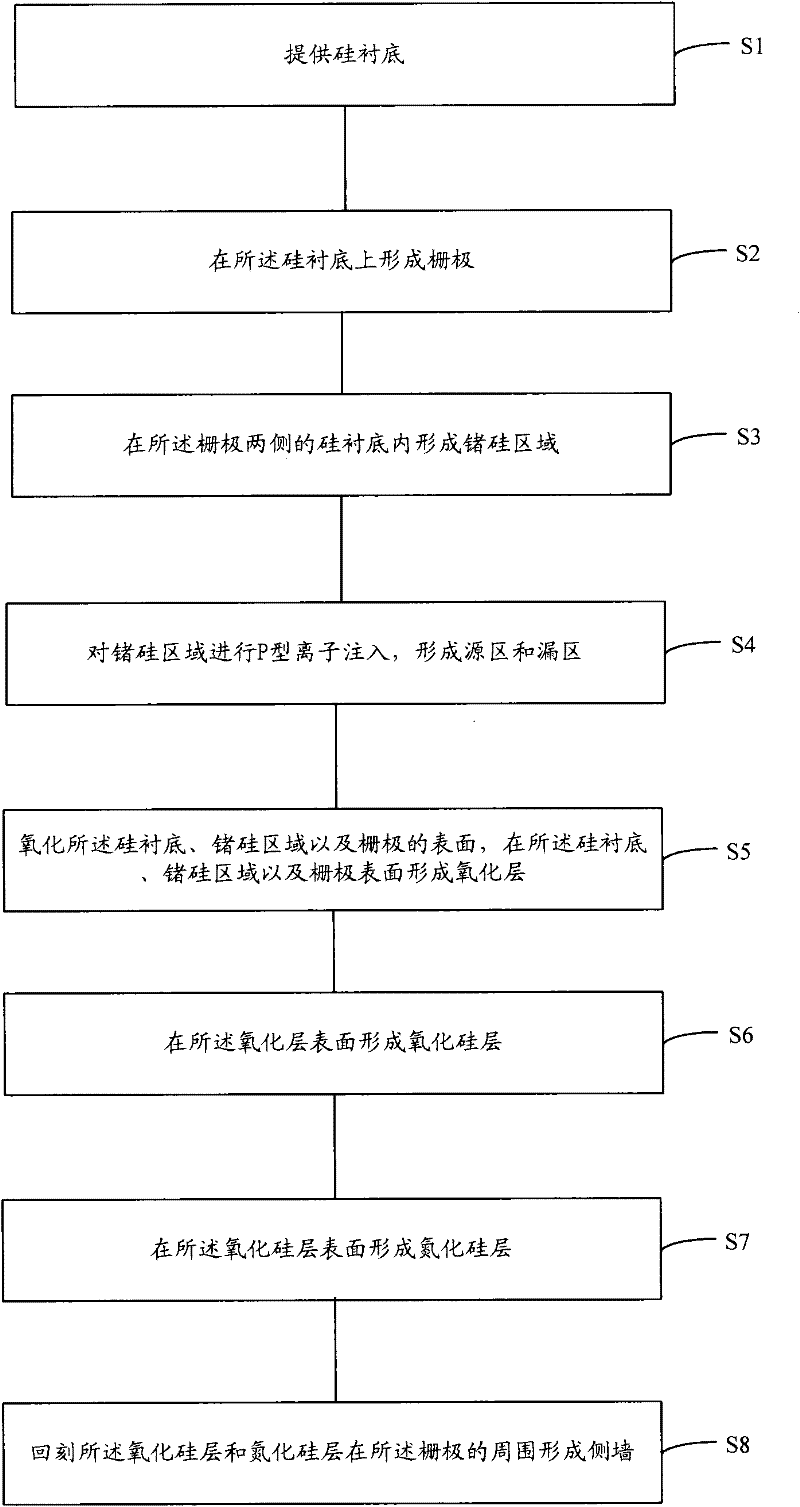

Method for forming side wall and p-channel metal oxide semiconductor (PMOS) transistor

A transistor and sidewall technology, which is applied in the field of forming sidewalls and PMOS transistors, can solve the problems of increasing stress difference between sidewalls and germanium-silicon, lattice mismatch, sidewall peeling, etc., and achieves the effect of good adhesion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

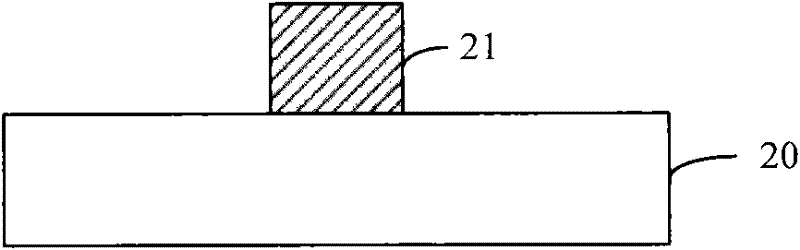

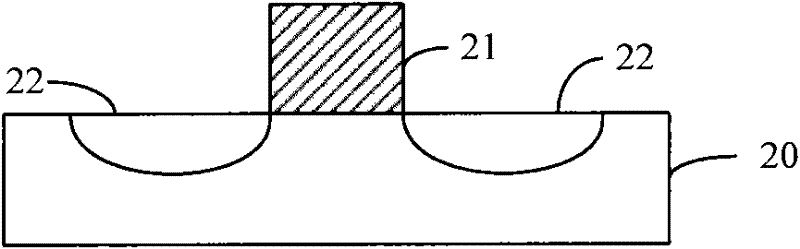

Embodiment Construction

[0039] There is no silicon oxide layer on the contact surface between the silicon germanium region and the side wall of the sidewall spacer formed by the method of the prior art, which causes the stress difference between the sidewall and the silicon germanium region to become larger, the lattice matching is out of adjustment, and the sidewall It is easy to peel off from the silicon substrate, thereby affecting the performance of the device. The inventors have studied hard and found the following reasons: if germanium ion implantation is used to form silicon germanium, when silicon germanium is formed, the surface of the silicon germanium region is damaged by the bombardment of germanium ions; when silicon germanium epitaxial growth is used to form silicon germanium , The adhesion between the surface of the silicon germanium area and silicon oxide is not good. After the silicon germanium region is formed in the silicon substrate, when the silicon germanium region is ion-implant...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com