Method for testing a scan-based integrated circuit by synthetic broadcaster and compact tool

A technology of compacting tools and integrated circuits, which is applied in the direction of measuring electricity, measuring electrical variables, and testing electronic circuits, etc., and can solve problems such as strong input restrictions and failure to obtain error coverage.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] The following description is presently contemplated as the best mode for carrying out the invention. This description is not intended to limit the invention, but merely to illustrate the principles of the invention. The scope of the invention will be determined by reference to the appended claims.

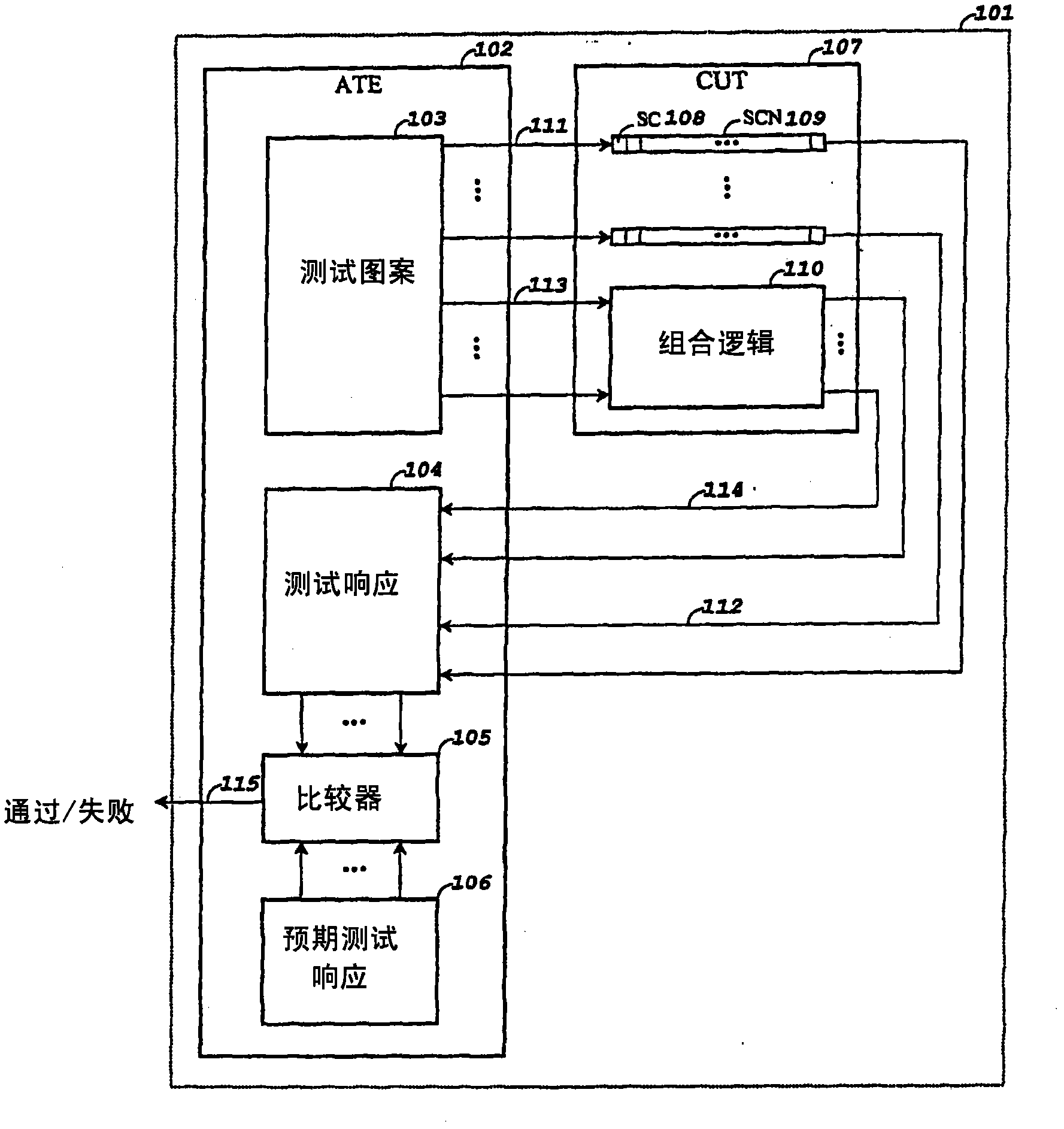

[0044] figure 1 A block diagram of a general system for testing scan-based integrated circuits using ATE is given. System 101 includes a tester or external automatic test equipment (ATE) 102 and a circuit under test (CUT) 107 including scan chain 109 .

[0045] ATE 102 applies a set of fully specified test patterns 103 to CUT 107 one by one in scan mode from external scan input probes 111 and from external primary input probes 113 through scan chain 109 . The CUT then enters standard mode with the applied test pattern as input and captures the response to the test pattern into the scan chain. The CUT then goes back into scan mode again, and the test responses are shifte...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More