Manufacturing method of MOS (metal oxide semiconductor) device

A technology of a MOS device and a manufacturing method, which is applied in the fields of semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of reduced control capability, consumption of single crystal silicon, etching of the semiconductor substrate 10, etc., to eliminate spacing, avoid effect of influence

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

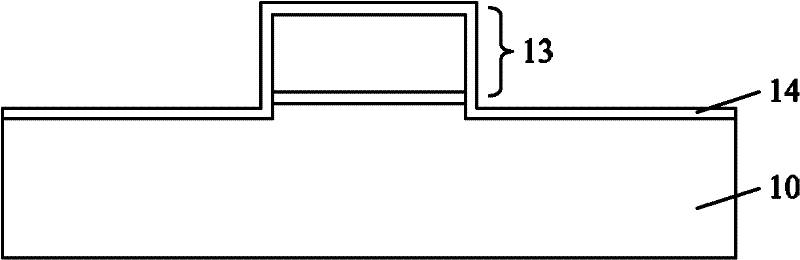

[0030] As mentioned in the background technology section, in the existing small feature size MOS device manufacturing method, due to the silicon recess phenomenon generated on the semiconductor substrate by the thermal oxidation process, a gap is formed between the bottom of the gate and the channel, and the distance between the gate and the channel The control ability of the MOS device is reduced, which in turn leads to an increase in the threshold voltage of the transistor, which affects the electrical performance of the MOS device.

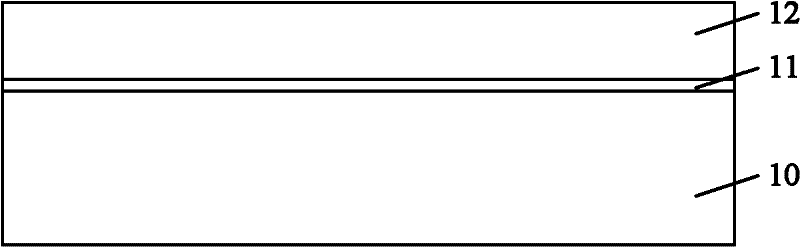

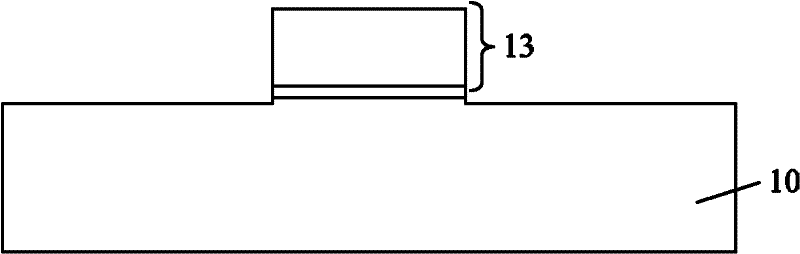

[0031] In view of the above problems, the inventors of the present invention provide a method for fabricating a MOS device. When forming the gate, the bottom of the gate is lower than the surface of the semiconductor substrate, so as to compensate for the semiconductor substrate being damaged in the gate etching process and thermal oxidation process. The thickness lost in the middle, thereby eliminating the gap between the bottom of the gate and...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More