Low power-consumption implementation method for CSA3 (Common Scrambling Algorithm 3) descrambling algorithm modules in DVB (Digital Video Broadcasting) system

A technology of an algorithm module and an implementation method, which is applied in image communication, selective content distribution, electrical components, etc., can solve problems such as doubling of peak power consumption, poor wiring, and increased difficulty in solving problems, so as to reduce peak power consumption , solve timing and wiring, and alleviate the effect of power consumption problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

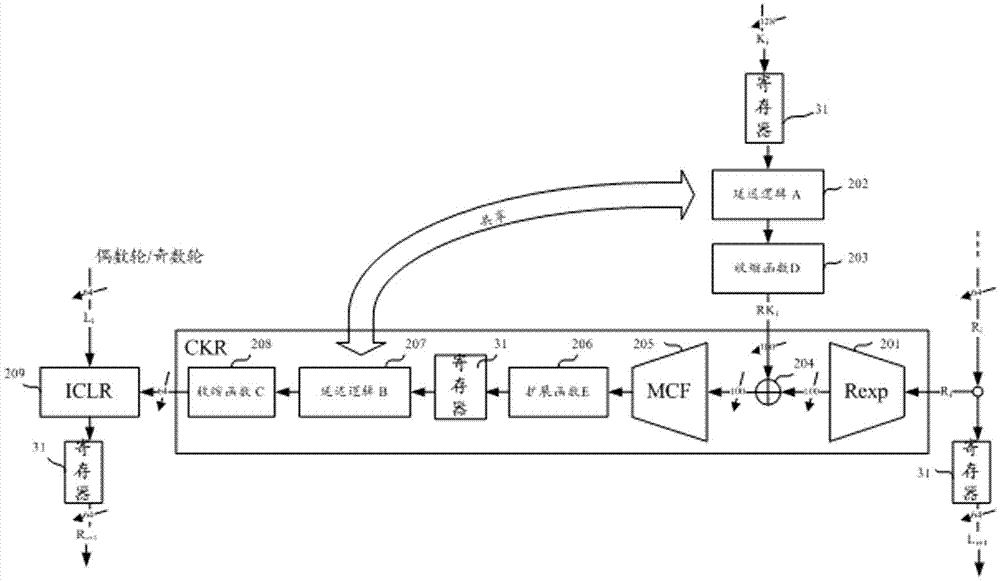

[0041] On the premise of not changing the CSA3 algorithm, the following image 3 The low-power implementation structure diagram of the single CSA3 descrambling algorithm module shown. A register 31 is inserted at the input ends of two delay logics (deceleration logic) A and B; the computation path of the two isolated delay logics A and B is set as a multi-cycle path.

[0042] Consider inserting register 31 at the input ends of two delay logics A and B, on the one hand, the even-numbered round path "delay logic Aà contraction function Dà expansion function Eà delay logic Bà contraction function C" and the odd-numbered round path "delay logic Bà contraction function DàExpansion function EàDelay logic AàContraction function C" is divided into two, which can effectively alleviate the problem of large delay of a single path, and can also break the timing loop and improve the test coverage of the circuit; on the other hand, it can also combine the two The power consumption of two d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More