Method for positioning fault testing vectors on basis of bisection method

A technology of test vector and fault test, which is applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc., can solve the problems of long test time and many test times, and achieve the effect of reducing test times, high efficiency, and fast and effective positioning

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

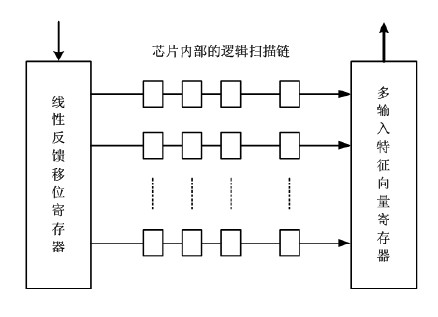

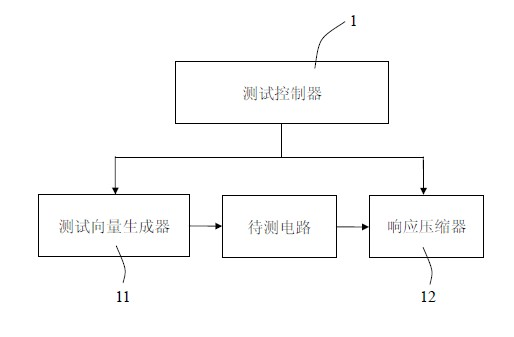

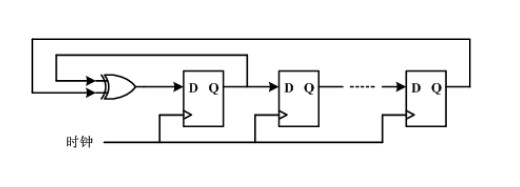

[0026] The location method of the fault test vector based on the dichotomy method of the present invention mainly uses the built-in self-test technology to test the chip-level logic fault, that is, the circuit to be tested is connected to the test bench, the test vector set is generated by the test bench, and the test The vector set is loaded on the circuit to be tested, and it is judged whether the circuit to be tested passes the test of the test vector set by comparing the test results. The test bench conforms to the basic architecture of the general built-in self-test. Please refer to figure 2 As shown, the test bench is provided with a test controller 1 including a test vector generator 11 and a response compressor 12 . Please refer to image 3 As shown, the test vector generator 11 includes a set of linear feedback shift registers (Linear Feedback Shift Register, LSFR). By configuring the number of seed sequences and test vectors of the test vector generator 11 and th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More