Stacked Chip Packaging Structure, Synchronous Rectifying Module And Converter Module

A chip packaging structure and synchronous rectification technology, applied in the direction of converting AC power input to DC power output, electric solid-state devices, semiconductor devices, etc., can solve the problems of high energy consumption, high impedance of bonding wires, and increased difficulty in making lead frame 10, etc. question

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

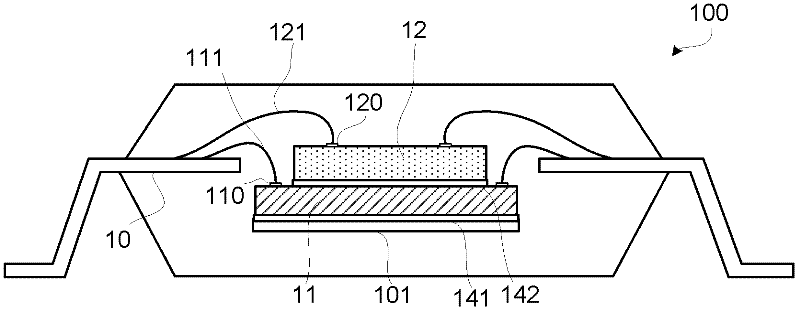

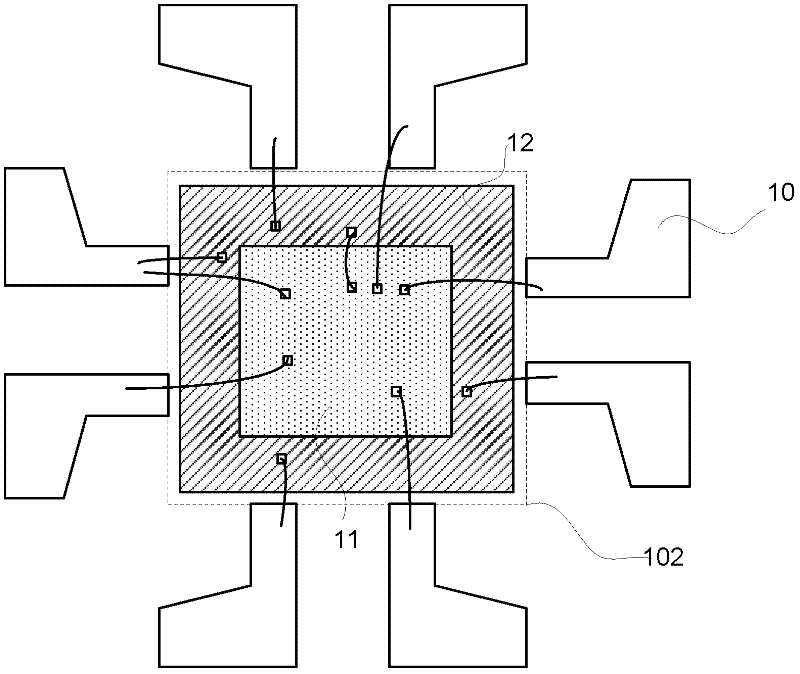

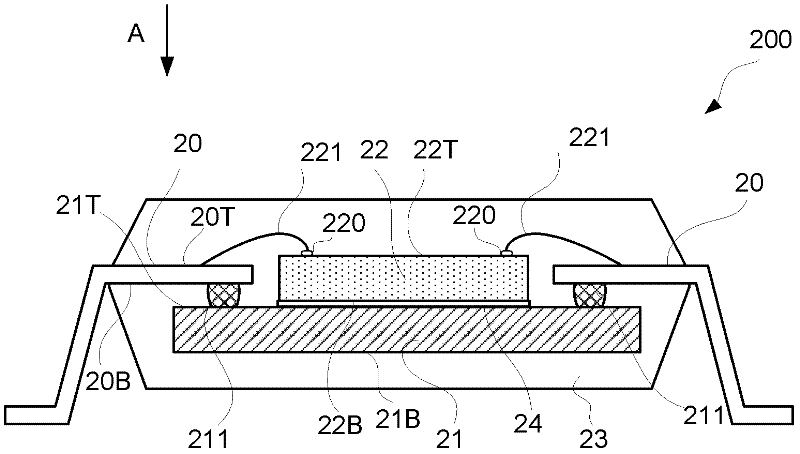

[0024] Exemplary embodiments of the present invention will be fully described below with reference to the accompanying drawings. These embodiments disclose a stacked die package structure that has both flip chip and wire bonded chips packaged therein. As used herein, "flip chip" refers to any packaged chip in which the contact areas of the chip are directly electrically coupled to the lead frame or substrate through solder bumps. The so-called "wire-bonded chip" refers to any packaged chip in which the electrical connection between the contact area and the lead frame is realized by bonding wires. The so-called "solder bump" refers to a spherical or columnar metal small piece used to directly electrically couple two contact areas, and the metal small piece is mostly filled with solder. The so-called "bonding wire" refers to a relatively small wire used to electrically couple two contact areas, and most of such wires are gold wires.

[0025] In the following detailed descripti...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com