Instantaneous harmonic estimation and compensation type single-phase inverter power supply and control method of single-phase inverter power supply

A technology of single-phase inverter and full-bridge inverter circuit, which is applied in the direction of electrical components, AC power input conversion to DC power output, output power conversion devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

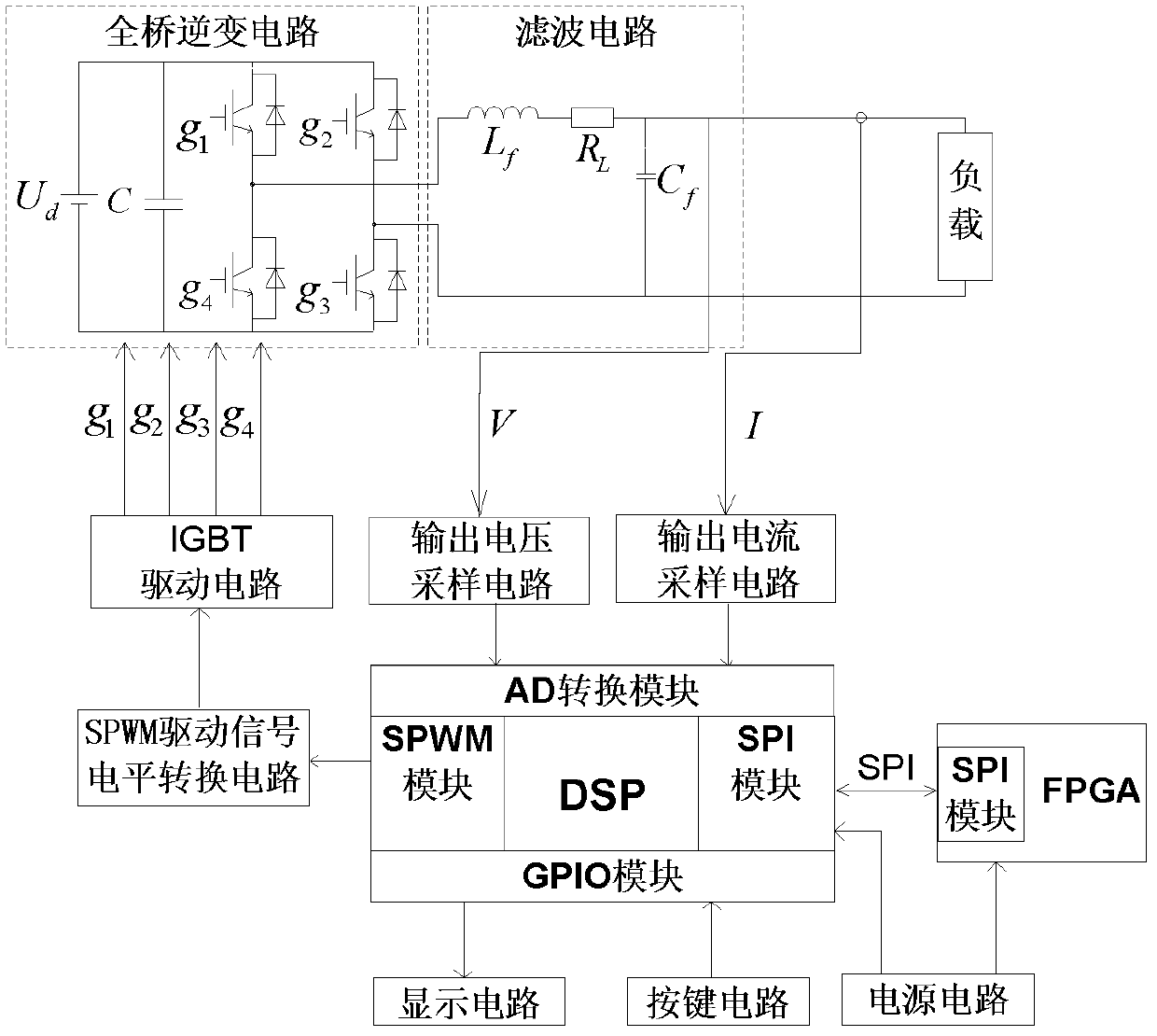

[0112] The specific implementation of the present invention will be further described below in conjunction with the accompanying drawings.

[0113] The instantaneous harmonic estimation and compensation type single-phase inverter power supply provided in this embodiment has a power of 3KW, an output voltage effective value of 220V, and a frequency of 50Hz. The instantaneous harmonic estimation and compensation type single-phase inverter power supply of the present invention, such as figure 1 As shown, it includes full-bridge inverter circuit, filter circuit, output voltage sampling circuit, output current sampling circuit, SPWM drive signal level conversion circuit, IGBT drive circuit, display circuit, button circuit, DSP, FPGA and power supply circuit.

[0114] The full-bridge inverter circuit includes a DC side filter capacitor and four fully-controlled switching devices IGBT, such as figure 1 shown, four IGBTg 1 , g 2 , g 3 , g 4 in, g 1 and g 4 form a bridge arm, g ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More