Router device suitable for globally asynchronous locally synchronous on-chip network

A local synchronization and on-chip interconnection technology, applied in data exchange networks, digital transmission systems, electrical components, etc., can solve problems such as speculation, increased cache costs, and inability to leave, and achieve the effect of saving storage resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

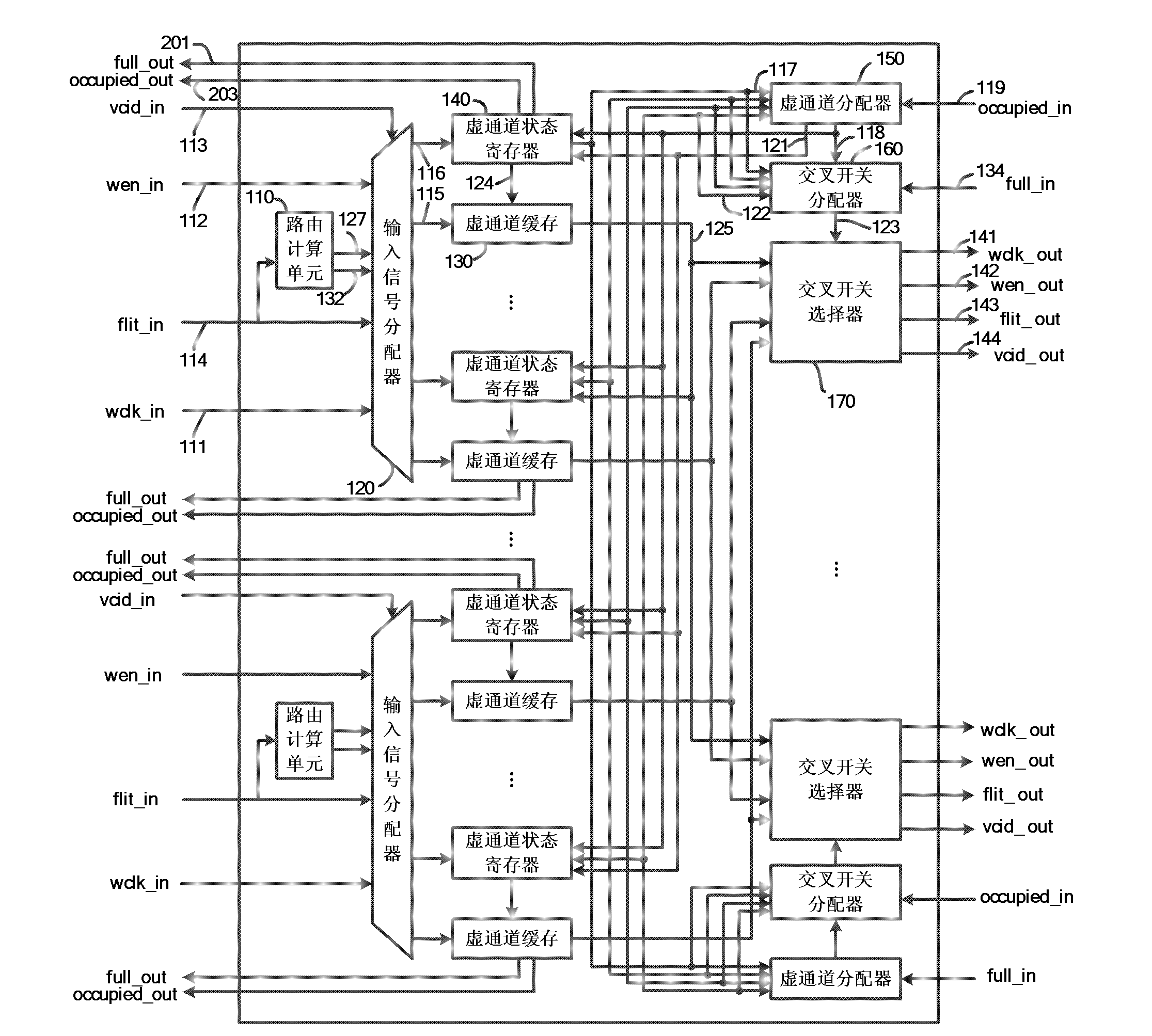

[0073] The minimum transmission unit of the router in the network of the present invention is a microchip, which is composed of a microchip header and a load. The flit header contains flit type, source address and destination address information, and the payload is valid data transmitted by the flit. After the router receives the microchip, it only performs routing calculation on the microchip header. The length of the microchip header is 22 bits, and its content is shown in Table 1. Table 1 uses a 10-bit address space to support an on-chip interconnection network of 1024 nodes, and extending the length of the address space can support an on-chip interconnection network of more nodes. Table 2 lists the codes for the flit types. The payload length can be configured as required.

[0074] Table 1

[0075] 22-20

19-10

9-0

microchip type

microchip source address

Chip Destination Address

[0076] Table 2

[0077]

[0078] The bloc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More