Method for finishing semiconductor-on-insulator type substrate

A semiconductor and insulator technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as incomplete packaging

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0059] The method according to the invention is a so-called "finishing" method for substrates of the SeOI-type semiconductor-on-insulator, since it involves steps followed by a detachment anneal leading to the transfer of layers and the steps performed in the formation of this substrate Step, the substrate includes an insulator layer buried between two semiconductor material layers.

[0060] will now refer to Figures 6A-6C The method according to the invention is described.

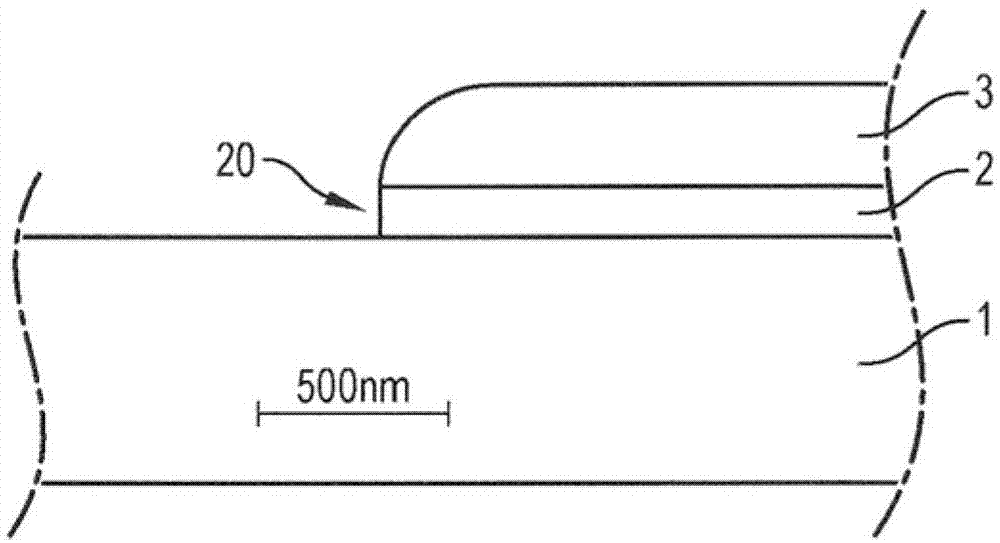

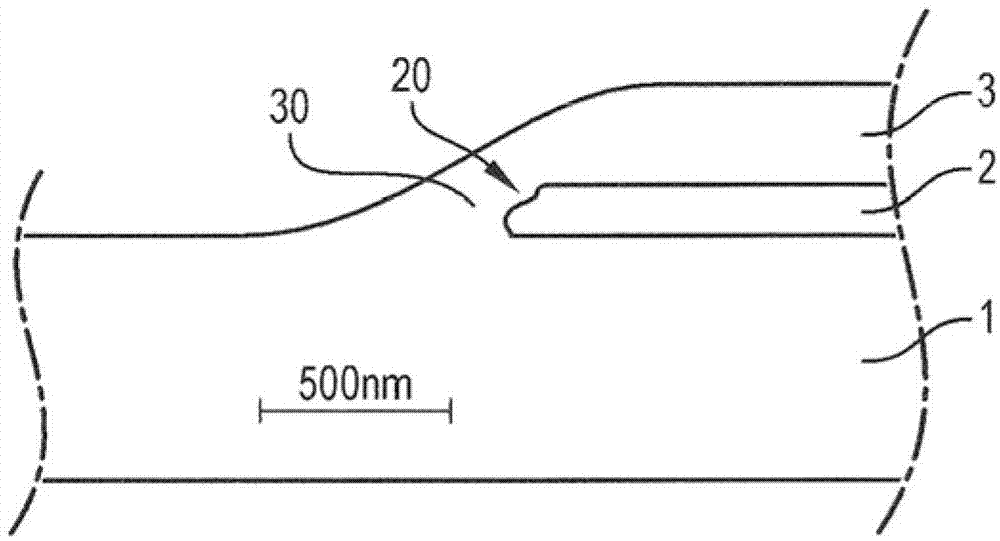

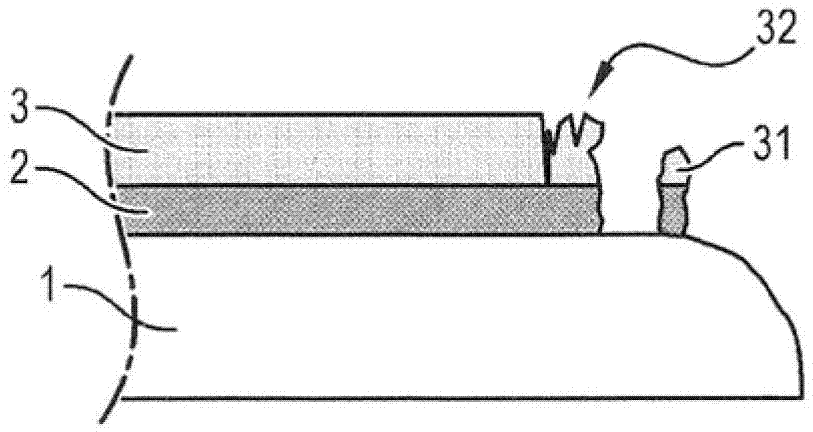

[0061] refer to Figure 6A , it can be seen that the substrate 4 of SeOI type comprises in sequence a surface layer 41 of semiconductor material, a buried insulator layer 42 and a support 43 also made of semiconductor material.

[0062] As shown in this figure, at the end of the layer transfer step, the obtained SeOI substrate 4 has defects of the aforementioned type, namely lamellae 44 (only one of which is shown in this figure) and peripheral annular jagged edges , labeled 45.

[0063] The first st...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More