Manpower cost management method for large-scale integrated circuit testing

A large-scale integrated circuit and labor cost technology, applied in the labor cost management of large-scale integrated circuit testing, indicating that a module and this RTL code modification field can solve the problem of inability to reasonably allocate testing labor costs, lack of quantitative indicators, and labor costs. Cost constraints, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

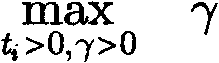

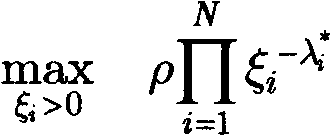

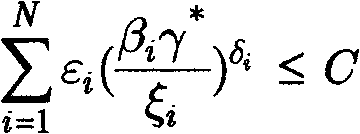

Method used

Image

Examples

Embodiment Construction

[0025] The following demonstrates the implementation process of the inventive method for an RTL design containing 5 modules, each of which corresponds to a regression test.

[0026] 1) Obviously N=5, the parameter c obtained by fitting the functional coverage data i , x i For: (10.3, 0.31), (922, 0.29), (9.65, 0.27), (9.03, 0.28), (10.1, 0.26).

[0027] 2) Also run each regression test, collect disk usage information, and obtain its fitting parameter s i ,y i They are: (15.2, 0.15), (14.3, 0.12), (14.8, 0.14), (14.6, 0.11), (15.5, 0.13).

[0028] 3) A small amount of changes are made to the RTL code, a set of weighting parameters β provided by the designer i It is: 0.95, 0.95, 0.9, 0.9, 1, indicating that the changes are mainly concentrated in module 5, which has a greater impact on module 1 and module 2 in terms of function, and a weaker impact on module 3 and module 4.

[0029] 4) The administrator gives the upper limit of the available total computing time T=16000s and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More