Low-temperature CMOS (Complementary Metal-Oxide-Semiconductor Transistor) modeling method

A modeling method, low temperature technology, applied in the field of CMOS modeling

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0038] The measurement methods of various parameters of the low temperature model are as follows:

[0039] In order to extract the model, the NMOS tube needs to be connected into a four-terminal device, SOURCE, DRAIN, GATE, SUBSTRATE, the substrate is grounded, the initial voltage of Vgs is 0.7 volts, the change step is 0.86 volts, and the initial voltage of Vds is 0 volts. The change step size is 0.05 volts, and the characteristic curve of Vds-Id can be drawn after the scanning is completed (the abscissa is Vds, the unit is volts; the ordinate is Id, the unit is Ampere).

[0040] When performing Vgs-Id scanning, the initial voltage of Vgs is 0 volts, the change step is 0.05 volts, and Vds is 0.1 volts and 5 volts.

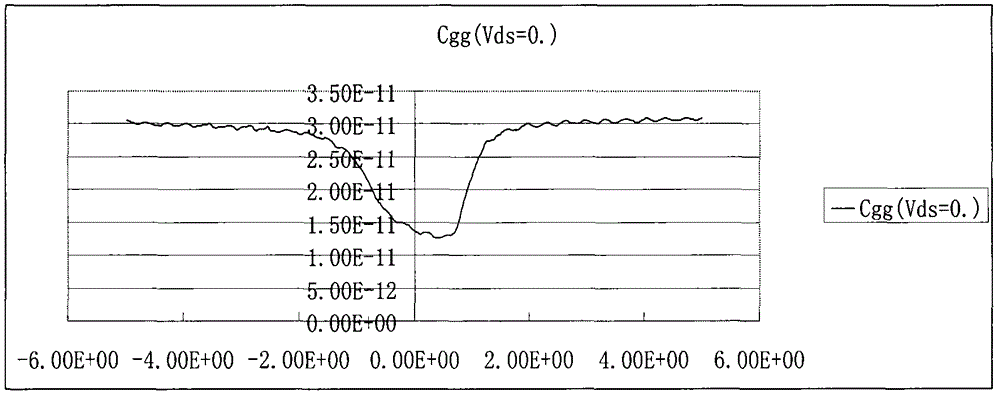

[0041] Test of junction capacitance Cgg: For NMOS four-terminal devices, connect SOURCE, DRAIN, and SUBSTRATE to the High end of CV590meter, and connect GATE to the Low end of CV590meter. The Vgs scanning range is -5 volts - 5 volts, the initial voltage is 5 volt...

Embodiment 2

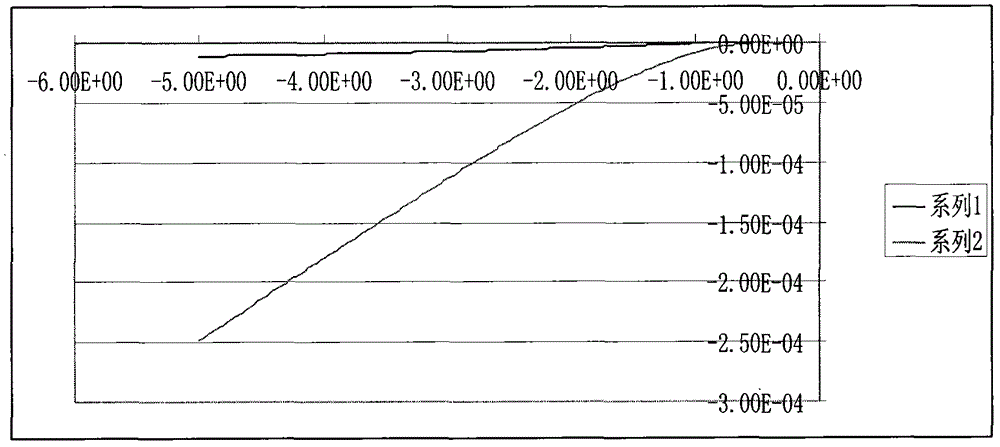

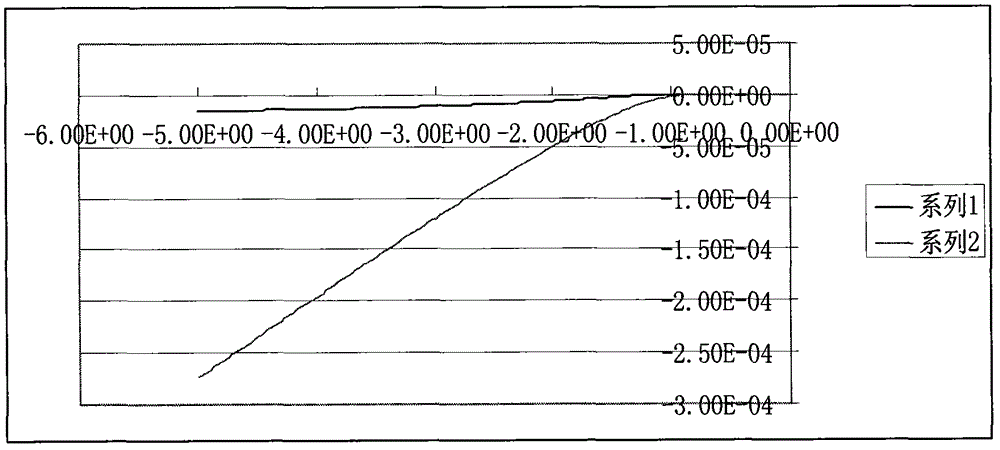

[0043] For threshold voltage changes, figure 1 and figure 2 It is the Vgs-Id characteristic curve of PMOS tube 0.6 / 0.55 at room temperature and low temperature 77K. Using the Vgs-Id characteristic curve, it can be concluded from the test results that as the temperature decreases, the threshold voltage V T Increase. The specific increase range is 1mV / 1°C.

Embodiment 3

[0045] For capacitance modification, image 3 and Figure 4 It is the Cgg-Vgs curve of NMOS tube 100 / 100 Dewar normal temperature 300K and Dewar low temperature 77K. It can be seen from the above two figures that the Cgg-Vgs curve has a small drop as the temperature decreases, but the change is not obvious. Its specific capacitance value variation is 5% smaller.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More