Control register mapping in heterogenous instruction set architecture processor

A technology of instruction set architecture and registers, which is applied in instruction analysis, program control design, operation instruction conversion, etc., and can solve problems such as authorized copyright infringement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

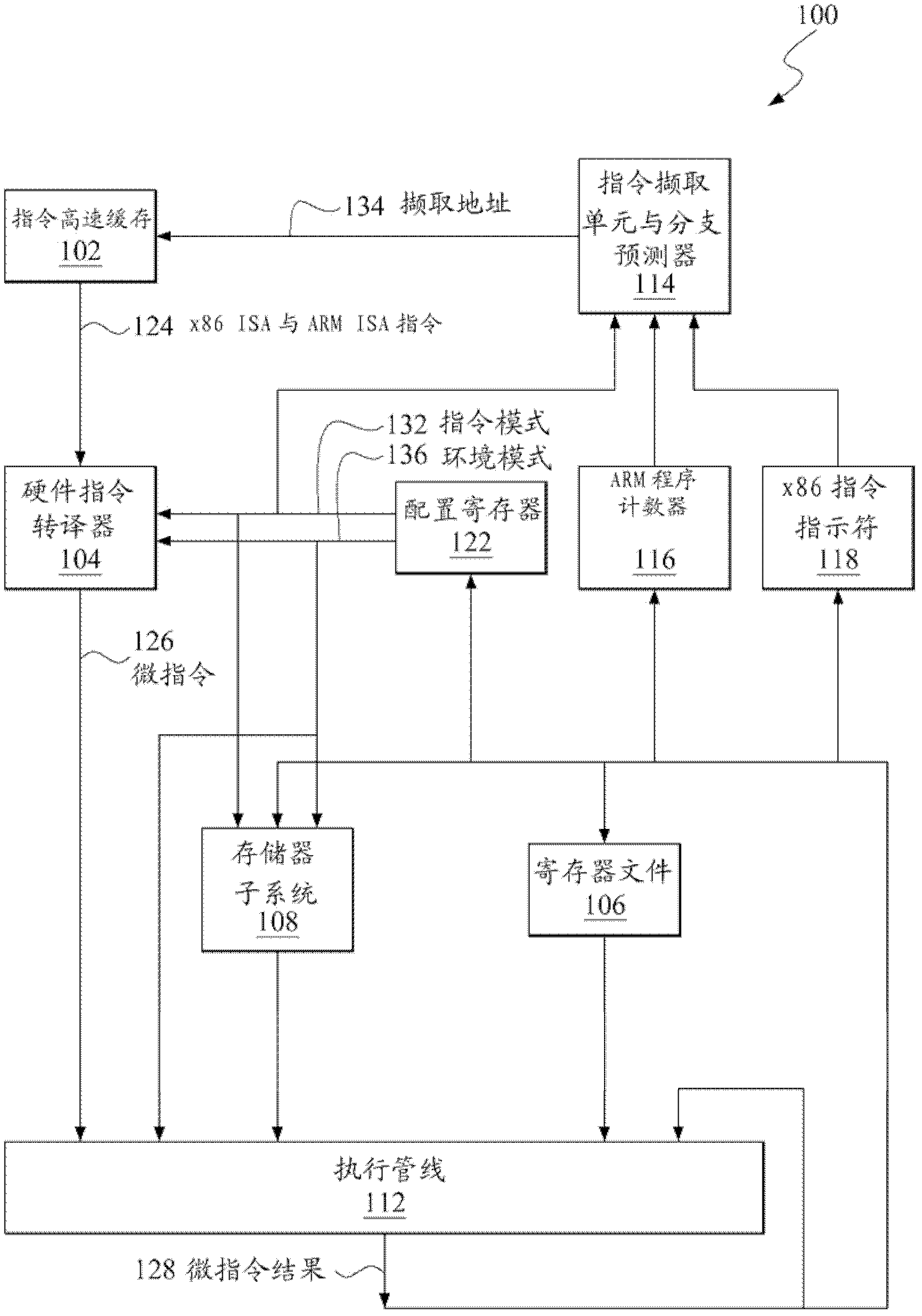

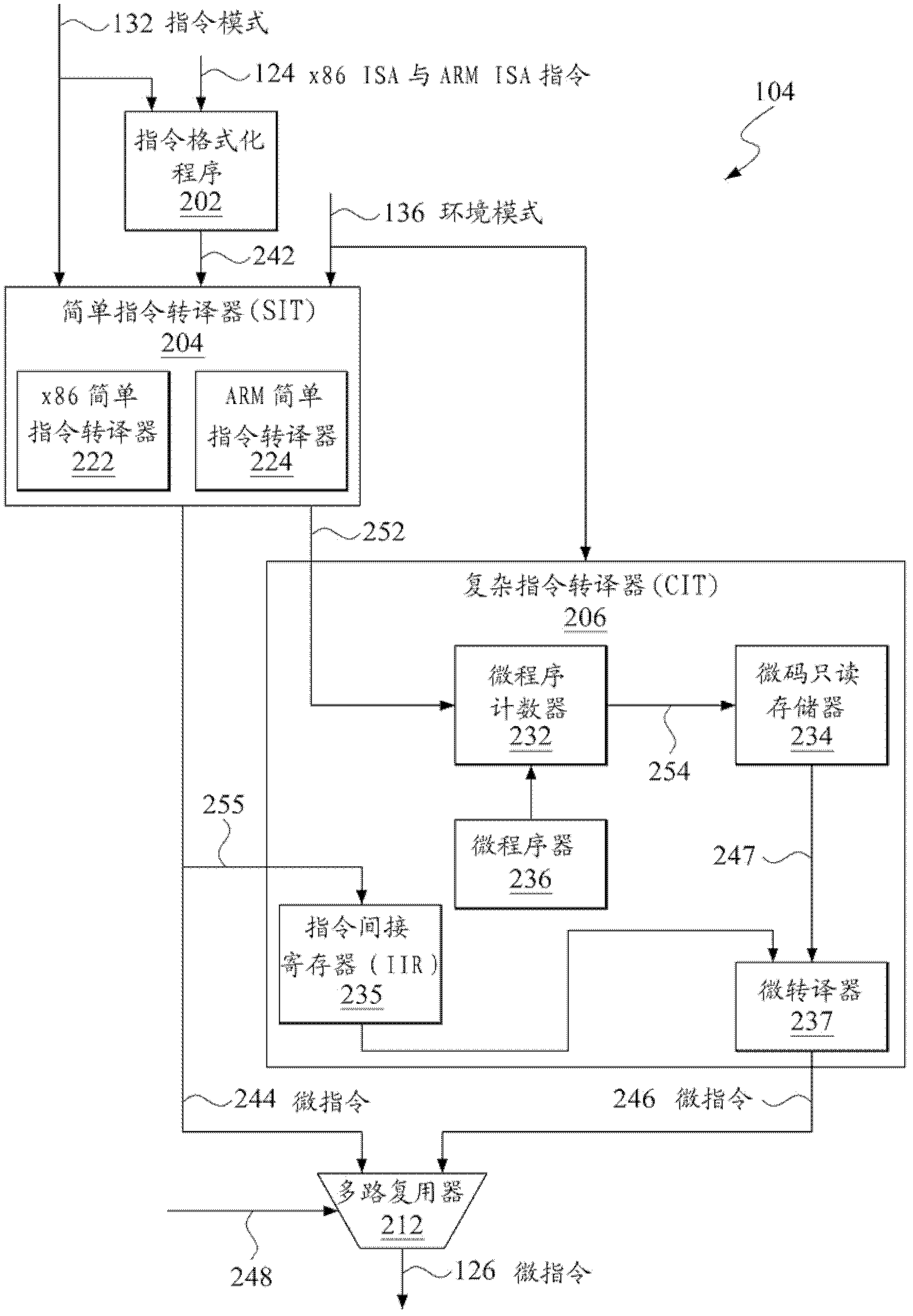

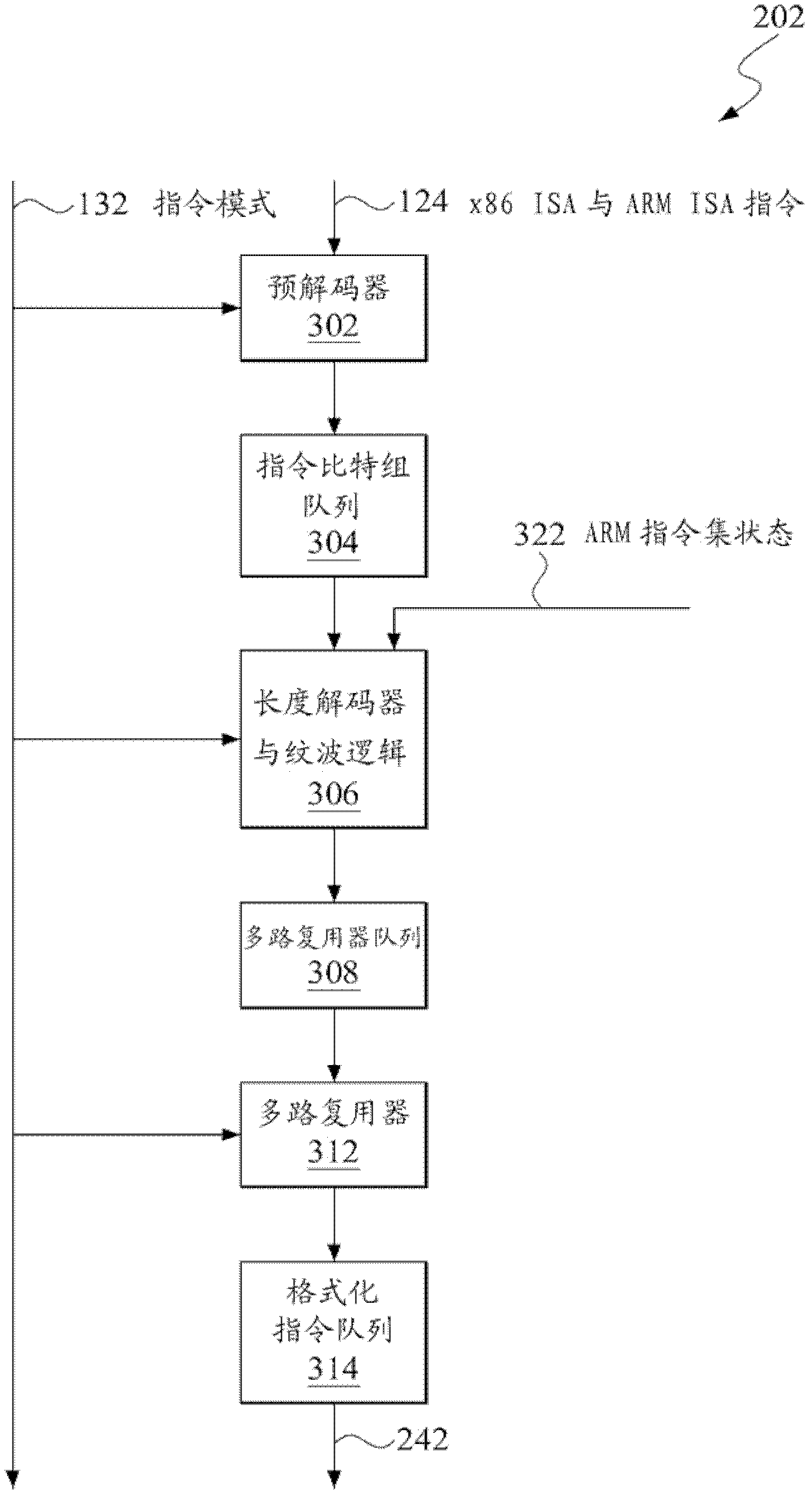

Embodiment Construction

[0089] noun definition

[0090] The instruction set defines the correspondence (mapping) between a set of binary encoded values (ie, machine language instructions) and operations performed by the microprocessor. Machine language programs are basically encoded in binary, but other binary systems can also be used, such as the machine language programs of some early IBM computers. Instead, it is encoded in decimal. Machine language instructions instruct the microprocessor to perform operations such as: add the operand in register 1 to the operand in register 2 and write the result to register 3, subtract the operand at memory address 0x12345678 The instruction is specific to immediate Operand (immediate operand) and write the result into register 5, move the value in register 6 according to the number of bits specified in register 7, if the zero flag is set, split 36 bit groups behind the instruction for this instruction, and set Register 8 is loaded with the value from Mem...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More