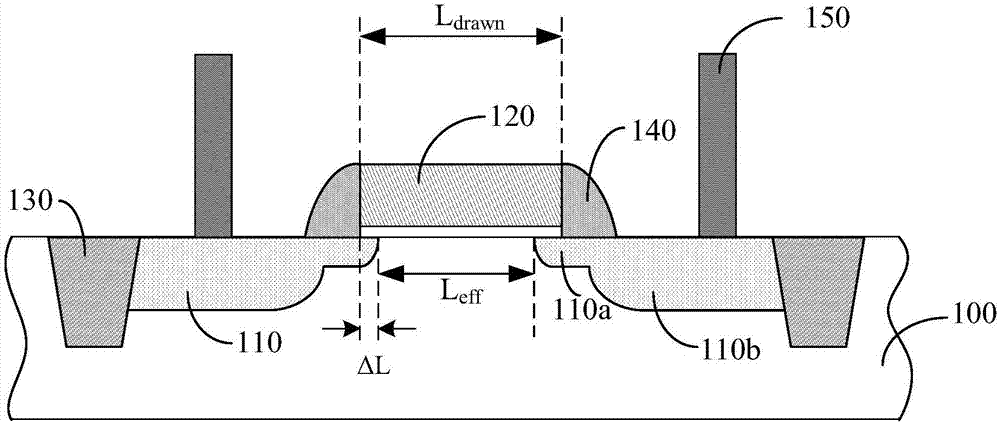

MOS transistor effective channel length test structure and test method

A MOS transistor and MOS structure technology, applied in the field of effective channel length testing, can solve the problem that gate-channel capacitance cannot be accurately calculated, and achieve accurate measurement results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] In order to make the purpose, technical solution and advantages of the present invention clearer, the following will further describe the implementation of the present invention in detail in conjunction with the accompanying drawings. Those skilled in the art can easily understand other advantages and effects of the present invention from the contents disclosed in this specification. The present invention can also be implemented or applied through other different specific implementation modes, and various modifications or changes can be made to the details in this specification based on different viewpoints and applications without departing from the spirit of the present invention.

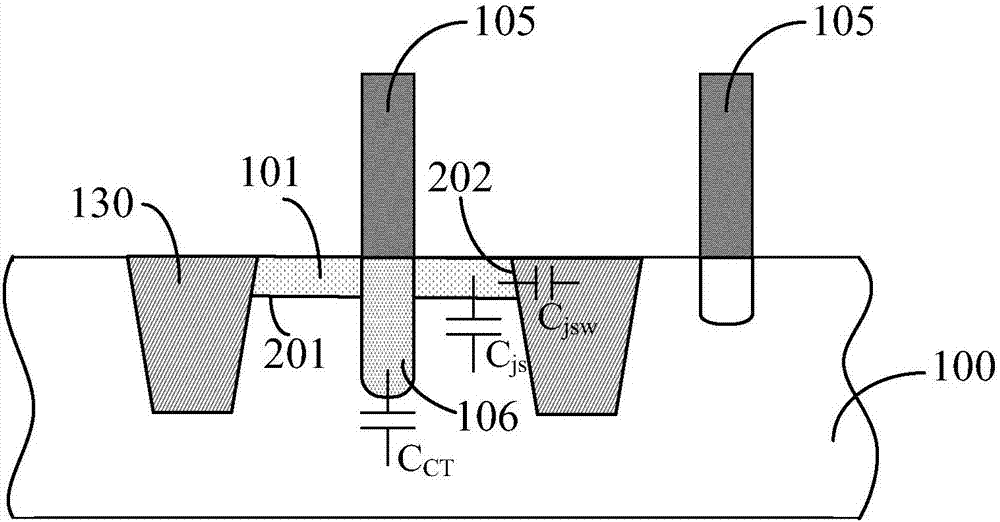

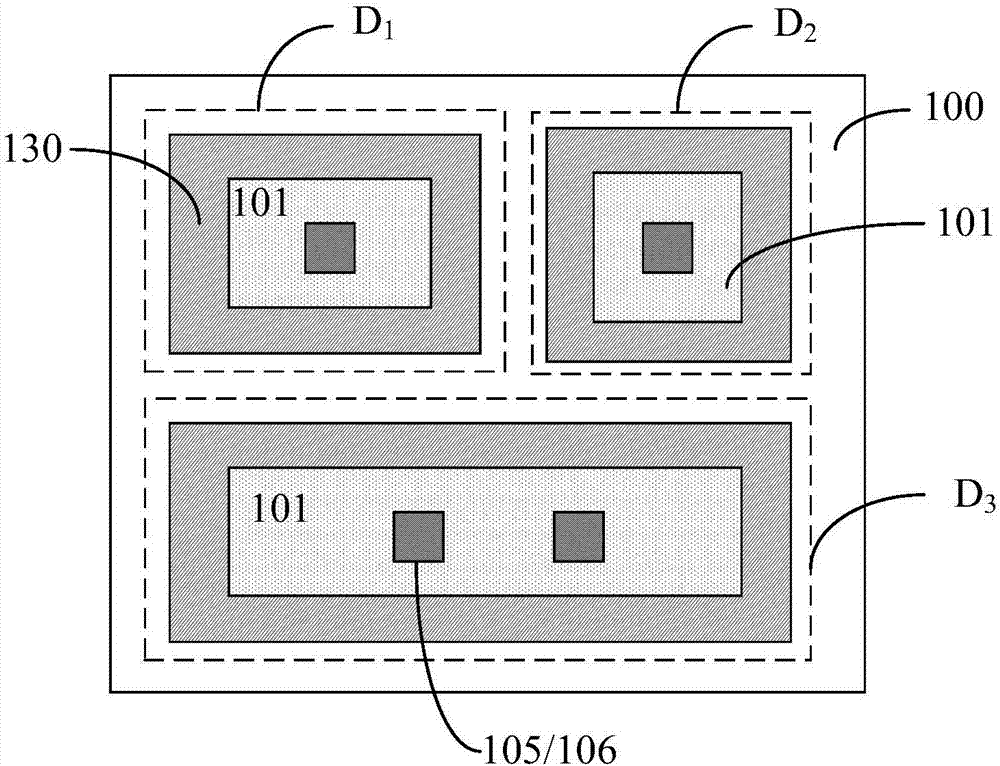

[0042] The first embodiment of the present invention provides a MOS transistor effective channel length testing structure.

[0043] The effective channel length test structure of the MOS transistor provided in this specific embodiment includes a first test unit and a second test unit.

[...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More