Frequency dividing circuit of I2S (inter-IC sound) interface clock circuit

A technology of clock circuit and frequency division circuit, which is applied in electrical components, counting chain pulse counters, pulse counters, etc. It can solve the problems of crystal oscillators that cannot meet the audio signal transmission of multiple sampling frequencies, high cost, cost reduction, and chip area. , to achieve the effect of reducing area, reducing use and reducing cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] In order to make the above objects, features and advantages of the present invention more comprehensible, the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

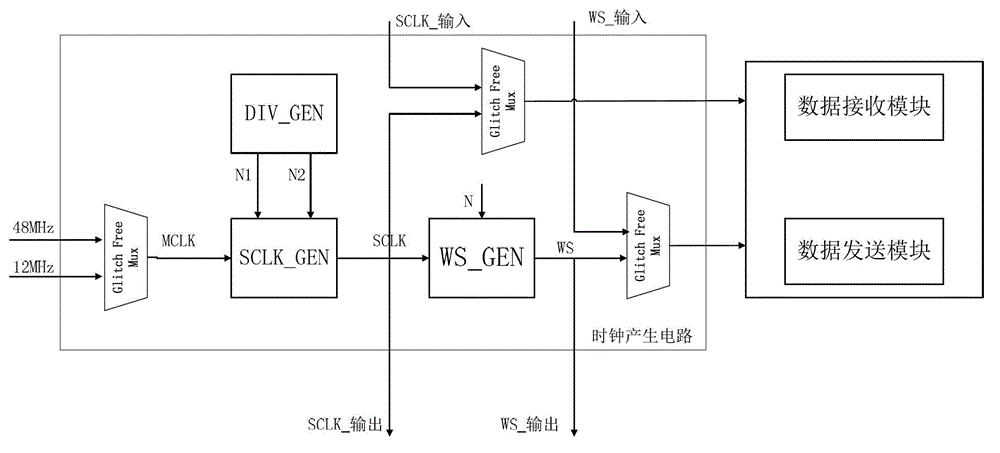

[0021] Aiming at the problems of increased cost and increased area caused by adding phase-locked loop circuits and additional crystal oscillators in the existing audio clock generation circuit technology, the present invention creatively proposes a method that utilizes the original 12MHz and 48MHz clocks of the chip system to generate and support all Sampling frequency of the serial bit clock SCLK mechanism.

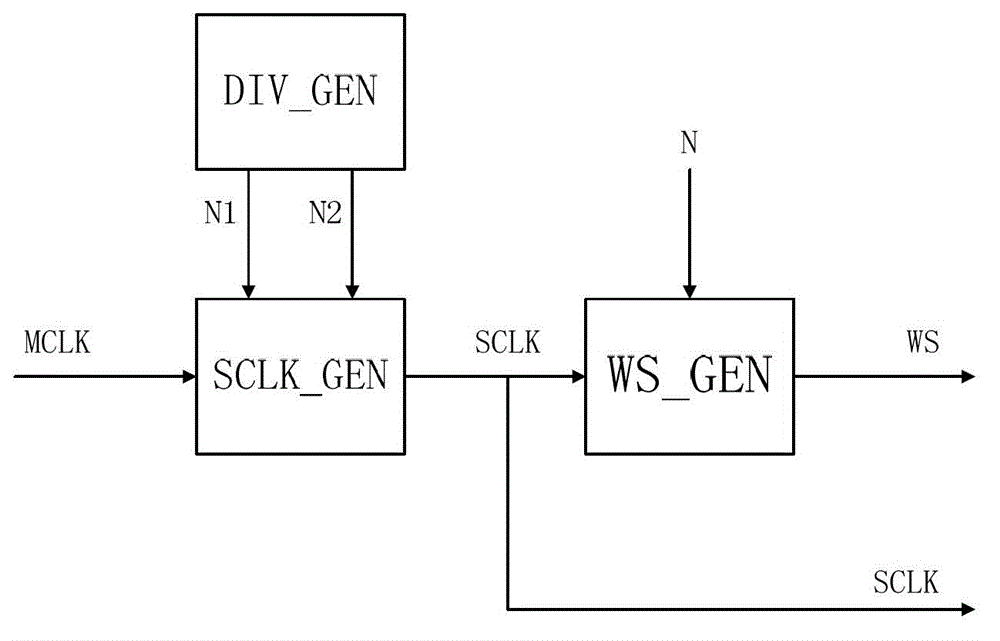

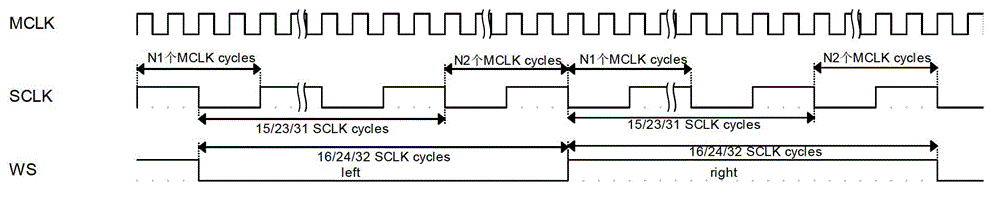

[0022] In the implementation example of the present invention, the frequency division factor generation module (DIV_GEN) calculates two values of the frequency division factors N1 and N2 according to the MCLK frequency, the required sampling frequency (the frequency of the WS signal), and ws_length, where N1 must be an even...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com