System, architecture and micro-architecture (sama) representation of an integrated circuit

An integrated circuit and processor architecture technology, applied in computer-aided design, software simulation/interpretation/simulation, special data processing applications, etc. The effect of mitigating the problem

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

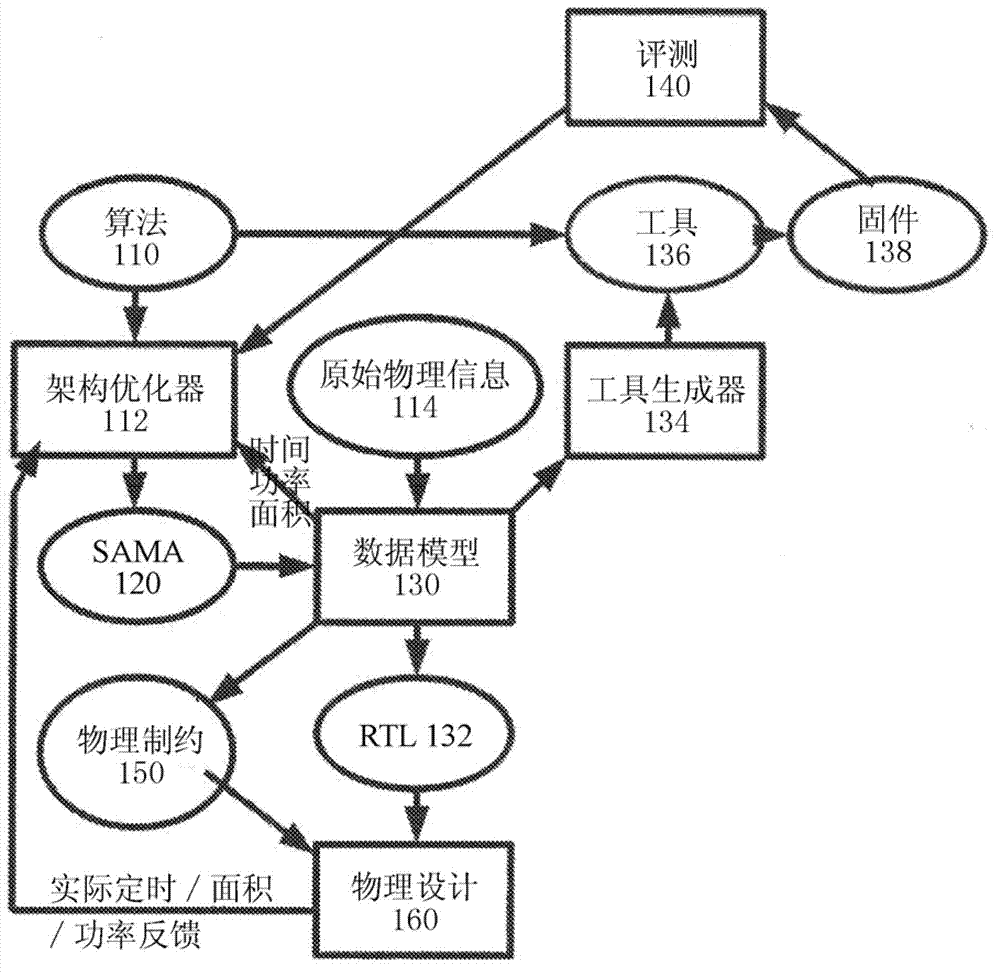

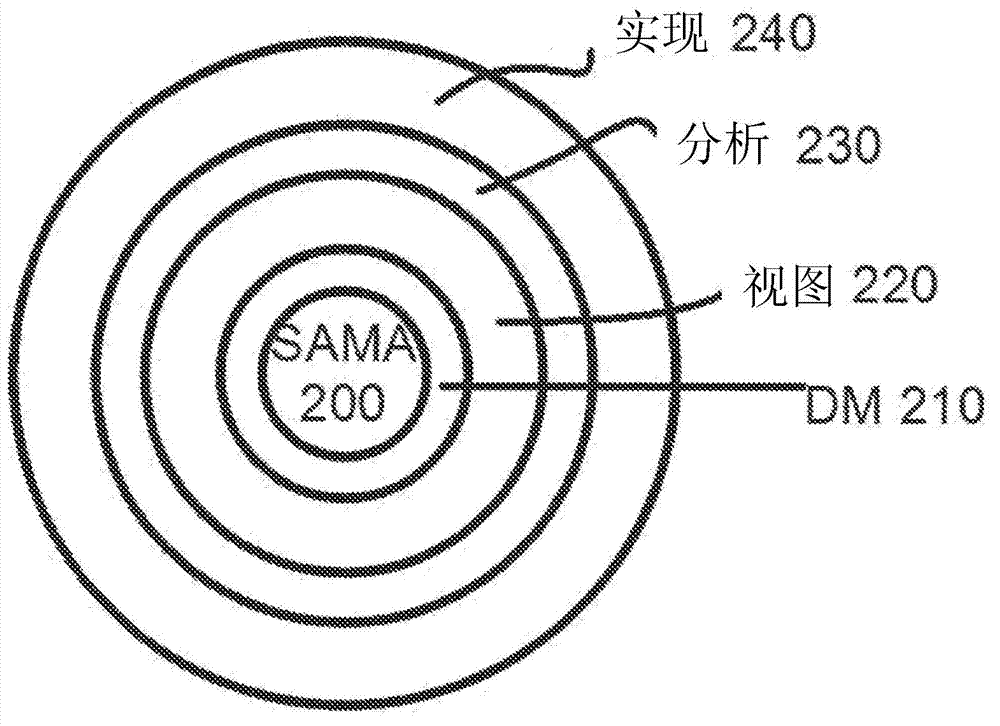

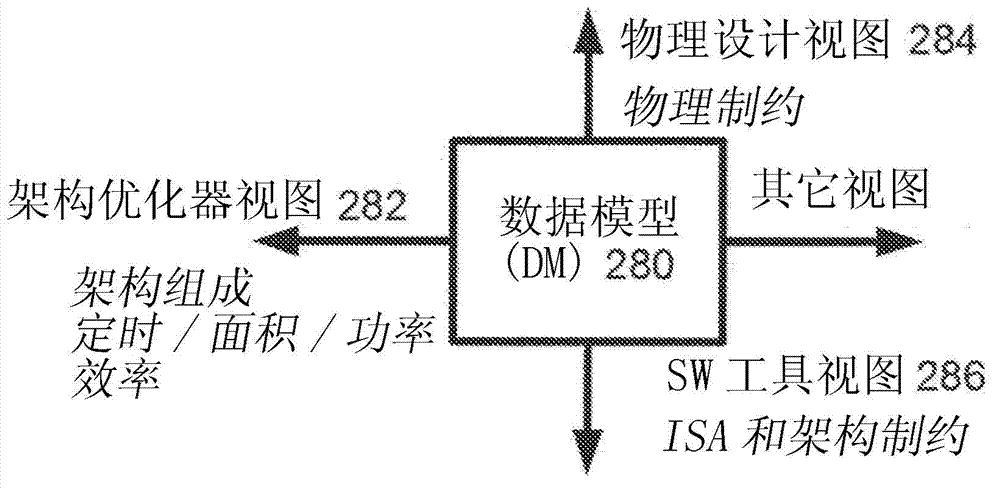

[0043] figure 1 An example workflow system for automated fabrication of ASICs from application code or algorithms is shown. First, the user generates application code or algorithms (110). This code is then provided to the architecture optimizer 112 . Architecture optimizer 112 generates an intermediate hardware representation tailored to the application code, referred to as the System, Architecture and Microarchitecture (SAMA) representation 120 which is an abstract unified representation of the ASIC. SAMA 120 is a high-level lightweight abstraction module that enables architecture optimizer 112 to optimize and generate new architectures described in SAMA 120 . SAMA 120 provides information to Data Model (DM) 130 which is an extended unified functional and physical model of the ASIC. The DM 130 receives, for example, physical raw information of ASICs such as adders and multipliers. DM 130 provides data to a tool generator 134 which drives a set of tools 136 such as compile...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More