Online upgrading structure and method for FPGA chip based on data frame asynchronous transmission protocol

An asynchronous transmission and data frame technology, applied in the direction of electrical digital data processing, instruments, program control devices, etc., can solve the problems that software and hardware cannot be upgraded, and the program of updating chips is complicated and difficult to implement, so as to achieve stable and reliable working performance and wide application range Wide, fast-running effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0081] In order to understand the technical content of the present invention more clearly, the following examples are given in detail.

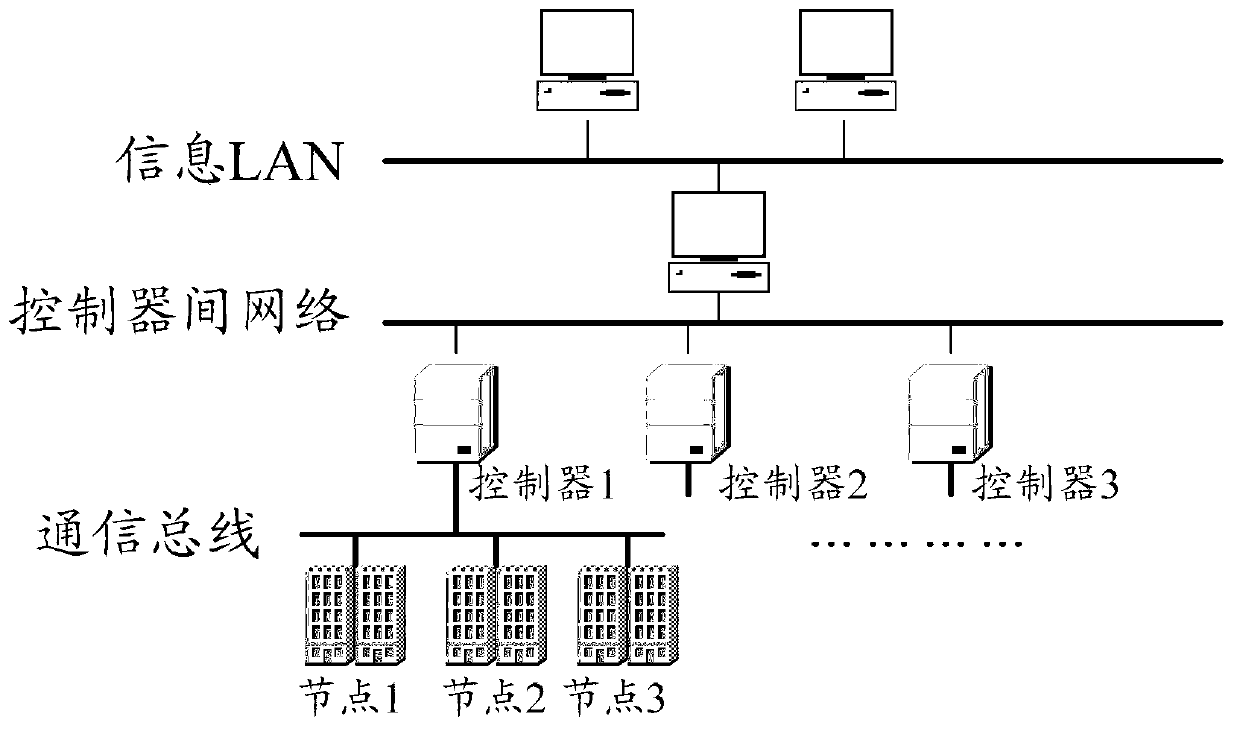

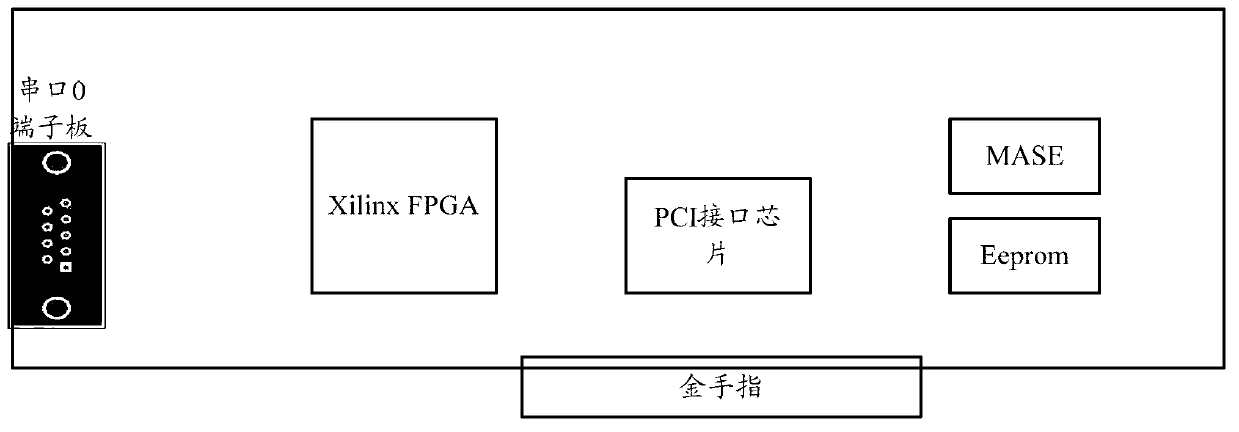

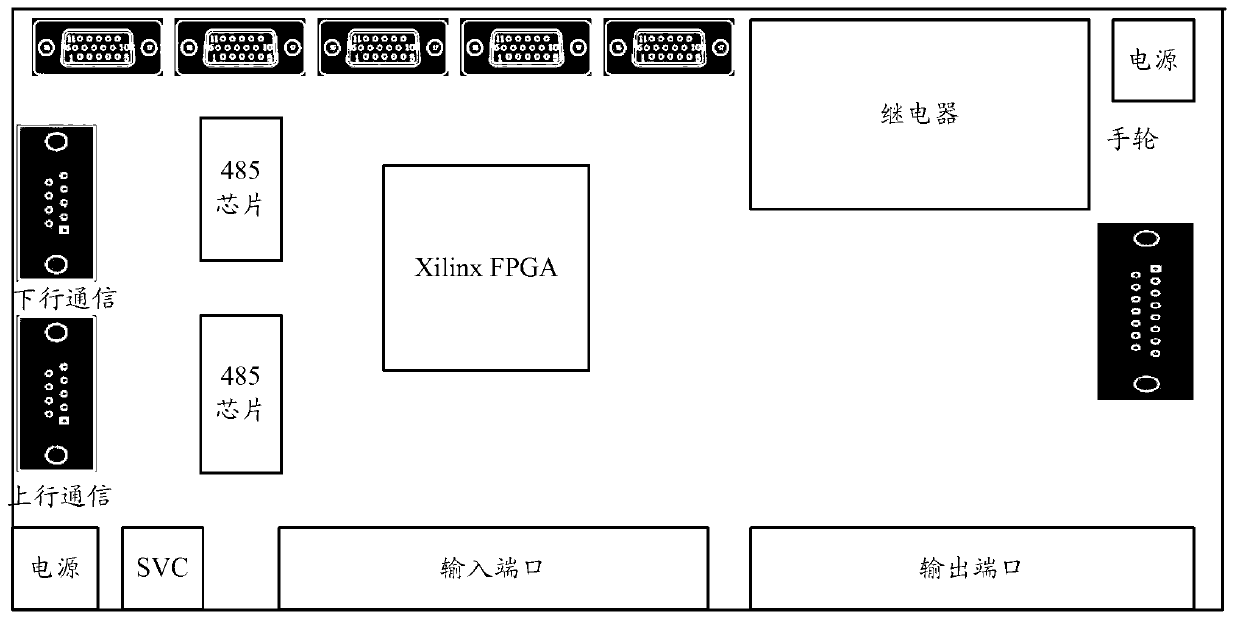

[0082] see Figure 1 to Figure 7 As shown, the circuit structure based on the data frame asynchronous transmission protocol to realize the online upgrade of the FPGA chip includes a control card, a main terminal board and several slave terminal boards, and the control card, the main terminal board and each slave terminal board all carry FPGA chip and corresponding Flash memory are arranged, and described control card is connected with external computer, and described control card, master terminal board and several slave terminal boards are serially connected successively, wherein, described control card carries The host interface and the slave interface, the main terminal board carries the main terminal board host interface and the main terminal board slave interface, and each of the slave terminal boards carries its own slave terminal board ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More