Field programmable gate array (FPGA) power-on reset system

A technology of electrical reset and reset signal, which is applied in the field of microelectronics, can solve the problems of dynamic switching power consumption and large short-circuit power, and achieve the effects of reducing dynamic switching power consumption and short-circuit power, reducing power dissipation, and improving safety

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings.

[0023] Such as figure 1 As shown, the FPGA power-on reset system disclosed by the present invention includes a power-on reset circuit for generating a POR pulse signal for power-on reset, a reset signal detection circuit for ensuring the reset validity of the POR signal, and the power-on reset The circuit is connected with the reset signal detection circuit, and the power-on reset circuit sends a POR pulse signal for power-on reset when the first power supply VDD of the chip rises to 1.6V, and the POR pulse signal is used to control the reset of the FPGA chip. The power-on reset circuit includes a delay module and a delay protection module.

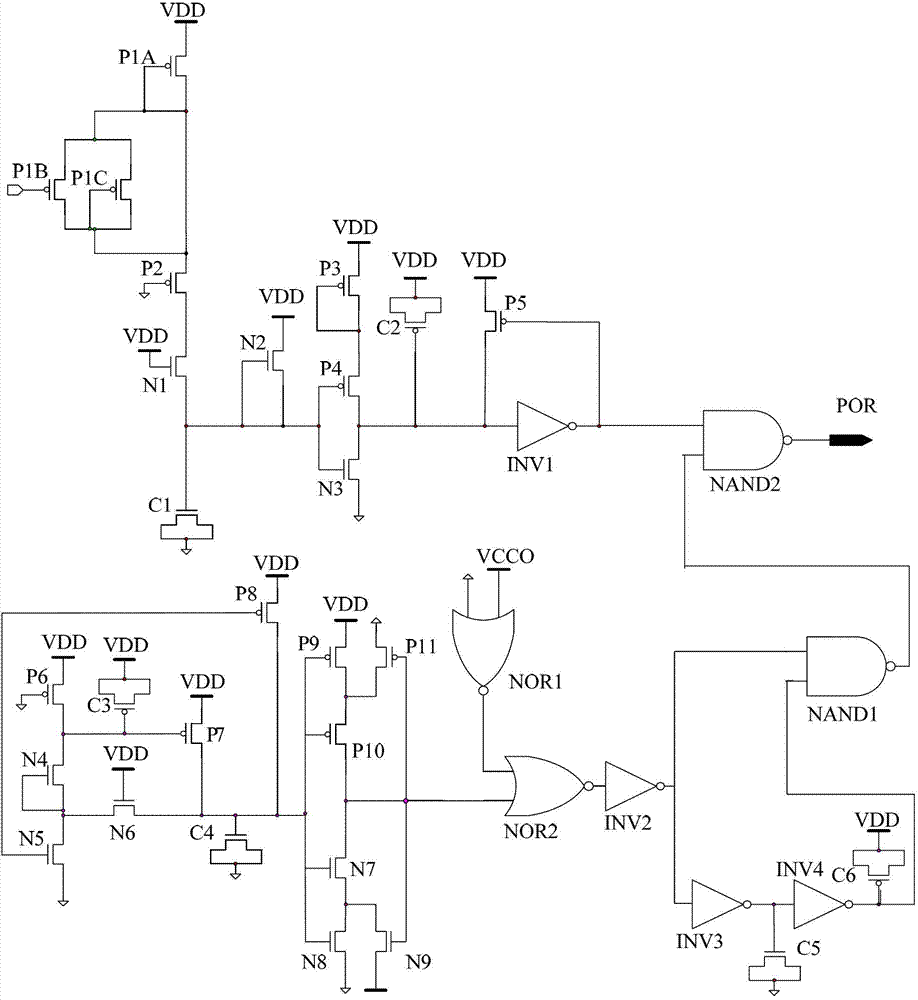

[0024] Such as figure 2As shown, the delay protection module includes PMOS transistors P1A, P1B, P1C, P2, P3, P4, P5, NM...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More