VS transient negative voltage endurance capacity testing device and method for high-voltage integrated circuit

A high-voltage integrated circuit and capability testing technology, which is applied in the field of high-voltage integrated circuits, can solve problems such as the inability to judge high-voltage integrated circuits, the inability to continuously adjust the amplitude and duration of VS transient negative pressure, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] In order to make the technical problems, technical solutions and beneficial effects solved by the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

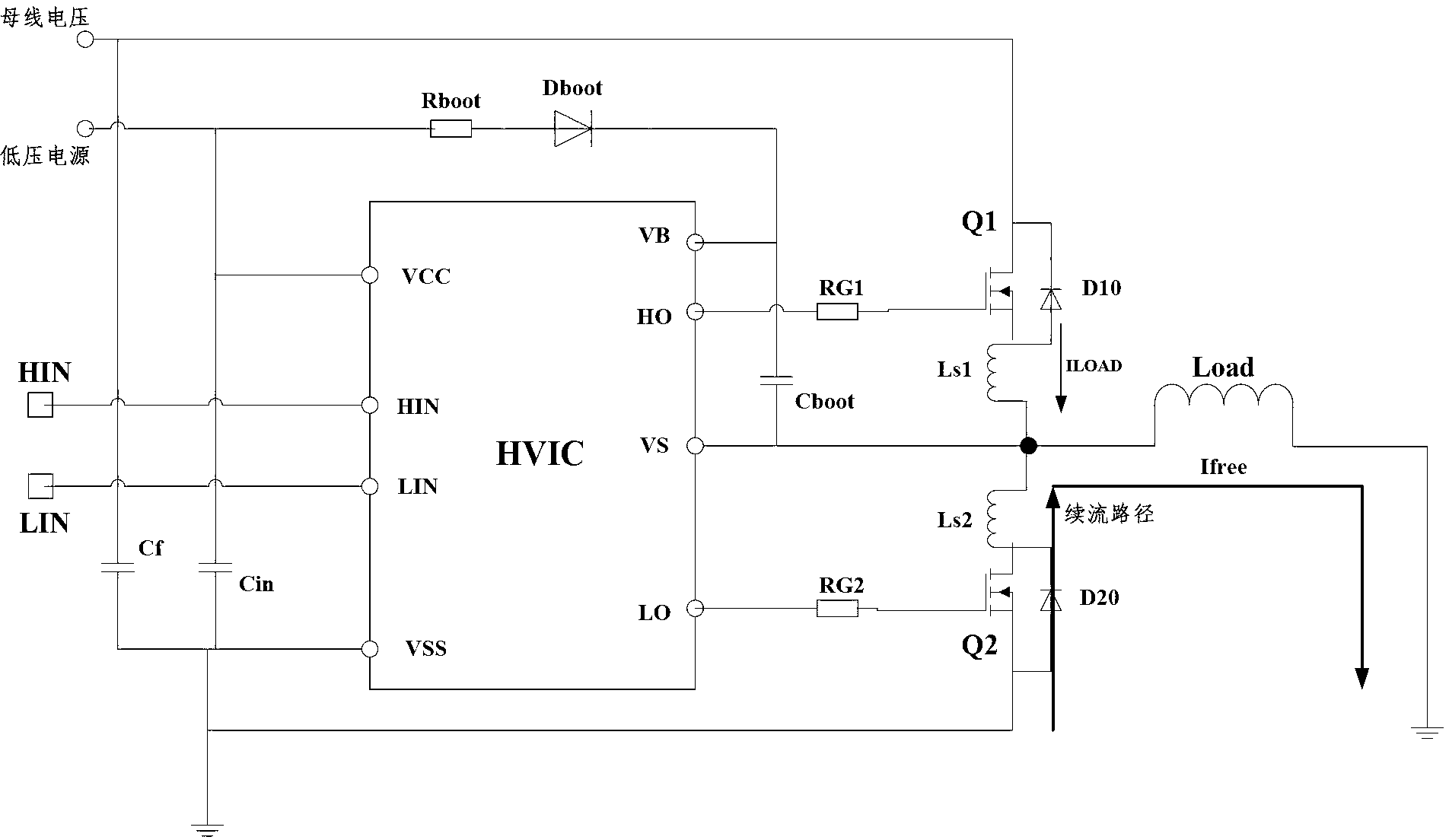

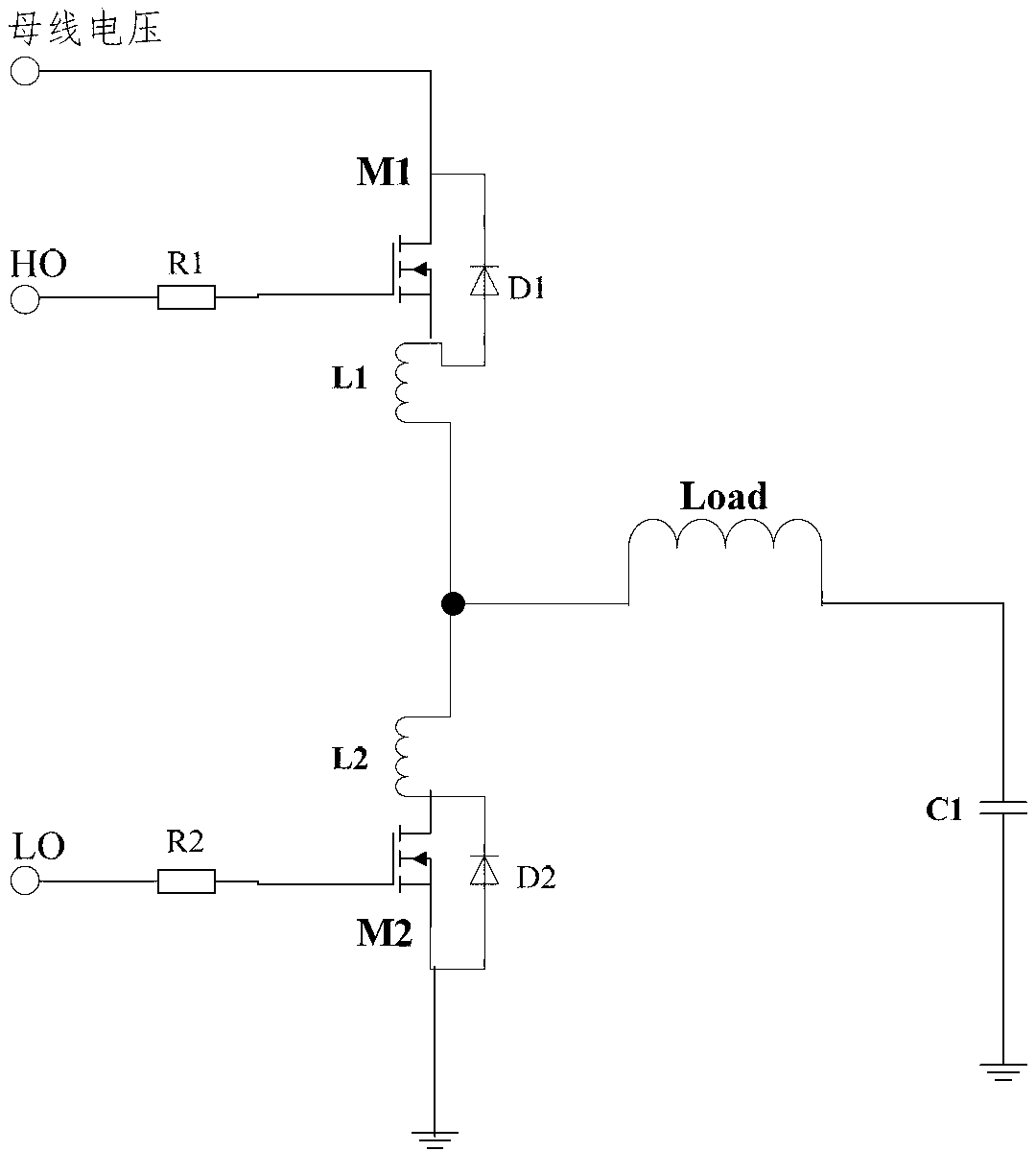

[0028] Please refer to Figure 4 As shown, a high-voltage integrated circuit VS transient negative voltage tolerance testing device includes a half-bridge drive circuit and a negative voltage generating circuit, and the negative voltage generating circuit includes a control circuit 2, a first switching device M3 and a negative voltage regulator Power supply VDC_VS; where,

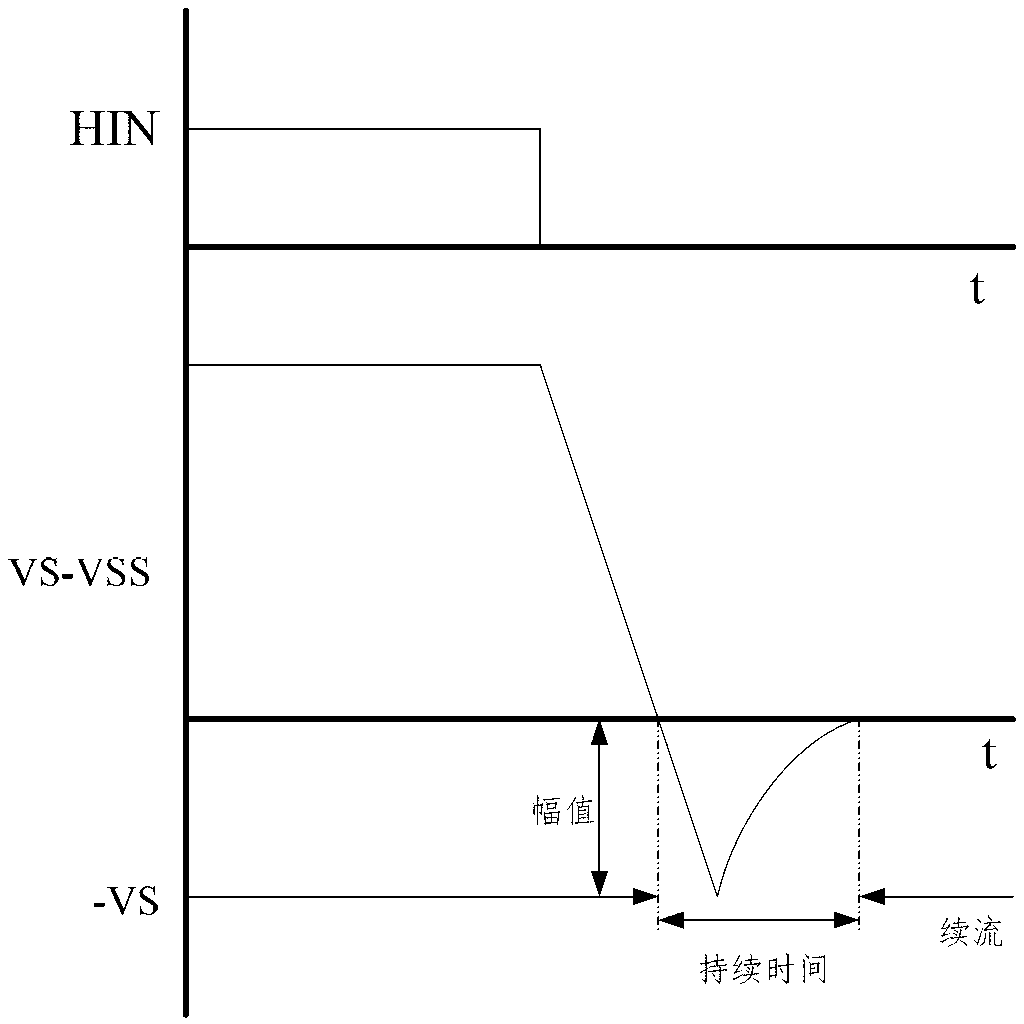

[0029] The control circuit 2 can be connected to the HIN signal input terminal (high-side input terminal) of the high-voltage integrated circuit 1, and is used to generate a pulse signal with a prede...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More