Method and device for testing trap density and position of gate oxide layer

A test method and trap density technology, applied in the direction of semiconductor/solid-state device test/measurement, etc., can solve the problems of not considering the trap density of pn junction and the lack of trap density test.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

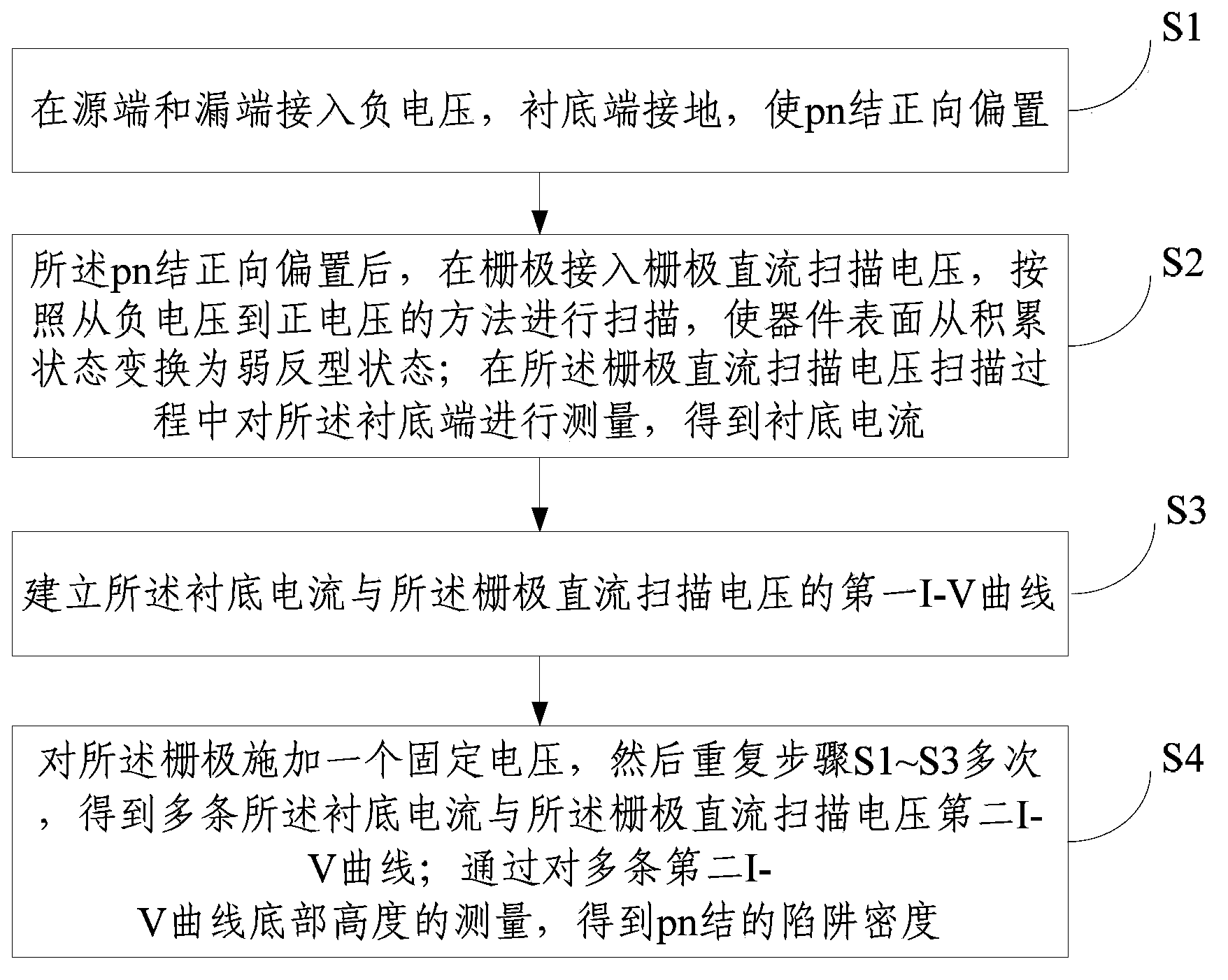

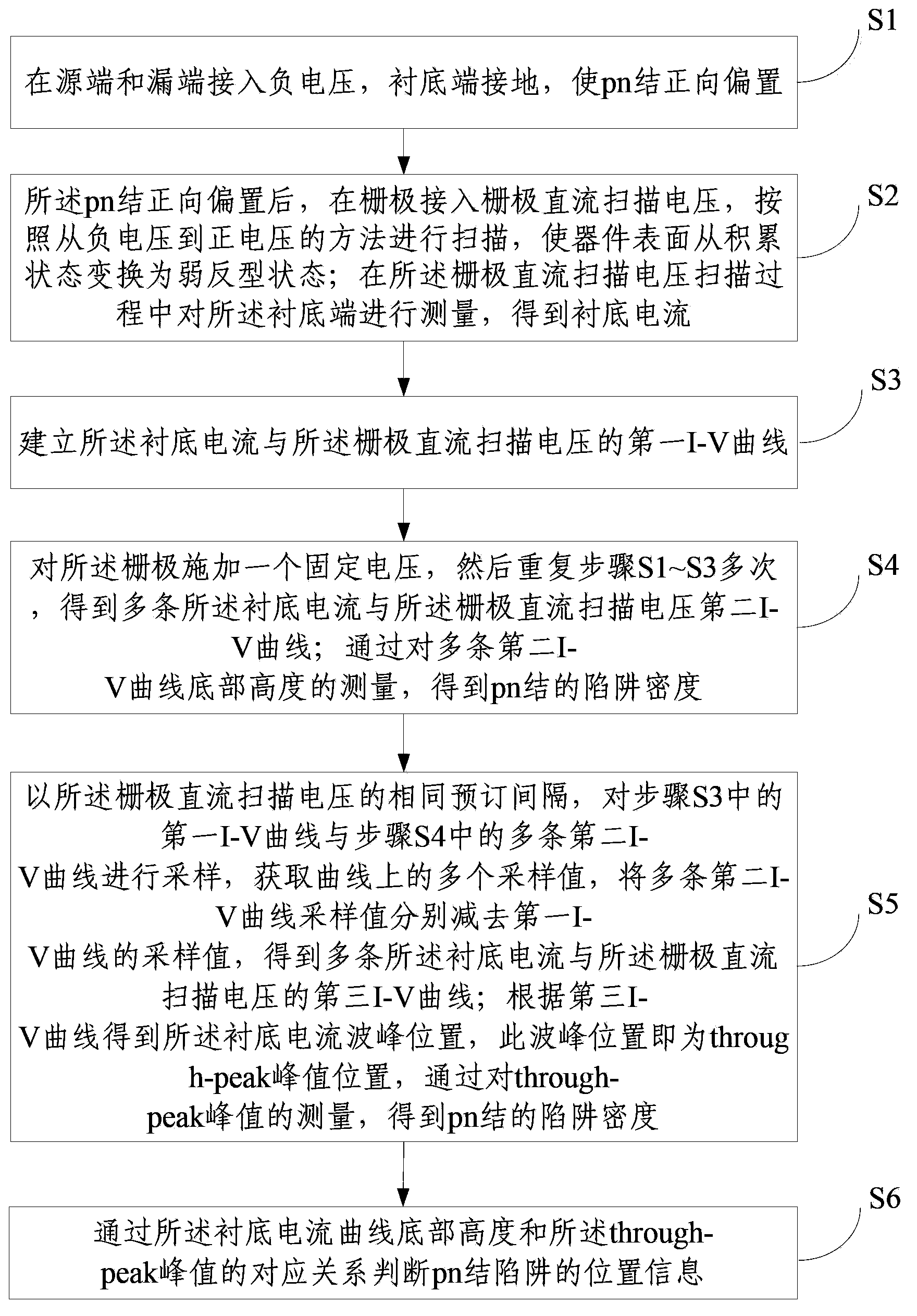

[0041] Such as figure 1 Shown, a kind of testing method of gate oxide layer trap density and position, comprises the following steps:

[0042] S1. A negative voltage is connected to the source terminal and the drain terminal, and the substrate terminal is grounded, so that the pn junction is forward biased;

[0043] S2. After the pn junction is forward-biased, connect the gate DC scanning voltage to the gate, and scan according to the method from negative voltage to positive voltage, so that the surface of the device is converted from an accumulation state to a weak inversion state; During the scanning process of the grid DC scanning voltage, the substrate end is measured to obtain the substrate current;

[0044] S3. Establishing a first I-V curve between the substrate current and the gate DC scanning voltage;

[0045]S4. Apply a fixed voltage to the gate, and then repeat steps S1 to S3 multiple times to obtain a plurality of second I-V curves of the substrate current and th...

Embodiment 2

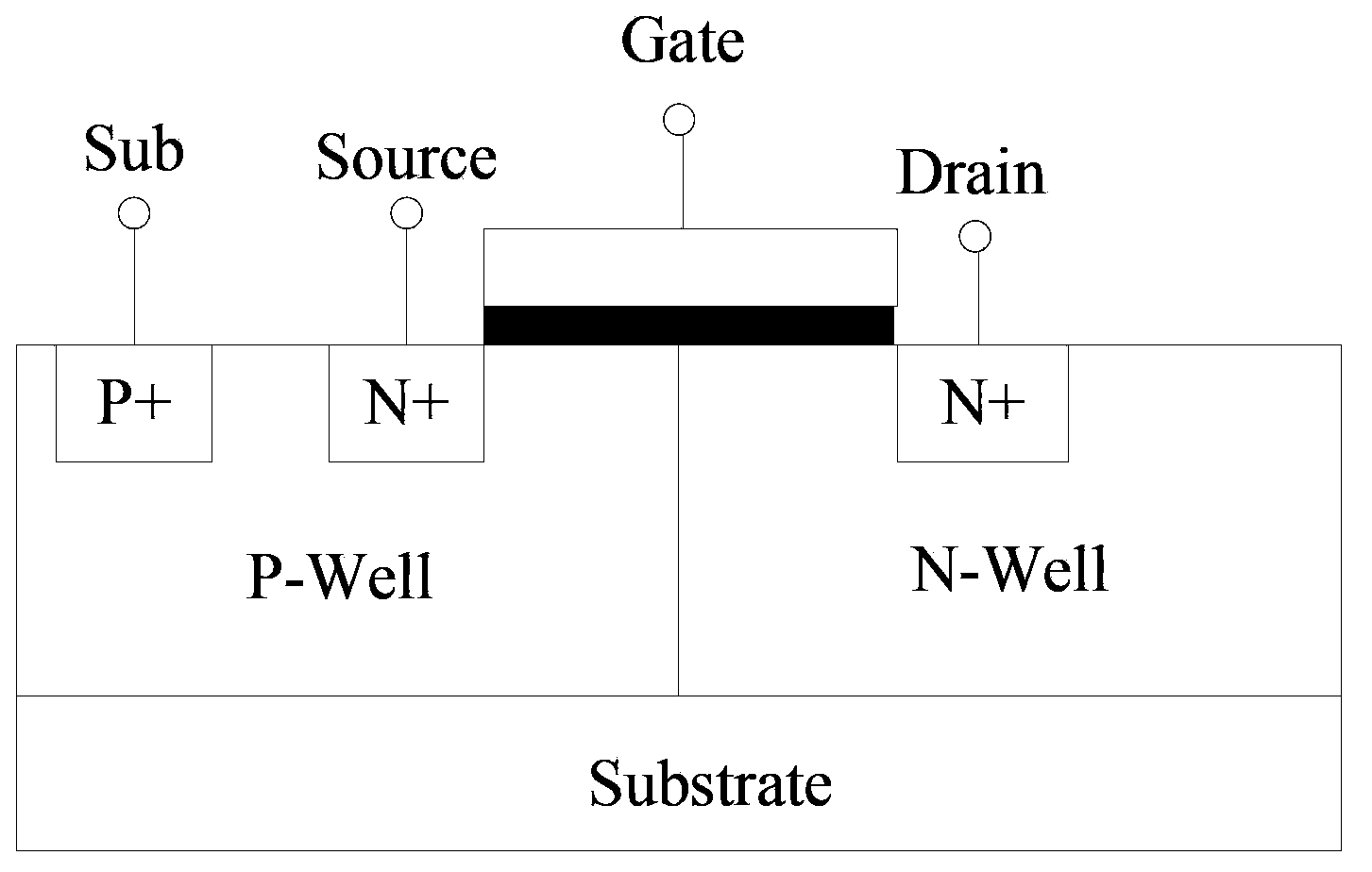

[0072] A gate oxide layer trap density and position testing device, characterized in that it includes an n-type MOSFET and a corresponding p-type gate oxide capacitor, or a p-type MOSFET and a corresponding n-type gate oxide capacitor; the n-type MOSFET and its corresponding The corresponding p-type gate oxide capacitor and the junction of the p-type MOSFET and its corresponding n-type gate oxide capacitor form a pn junction.

[0073] As shown in Figure 3(a), taking the n-type gate oxide layer interface trap density test device as an example, the left side of the n-type test device is the n-type MOSFET device part, which is composed of n + , p-well and gate constitute the source, substrate and gate of the test device of the present invention, and the right side of the test device is the p-type gate oxide capacitor part, which is composed of n + , n-well and gate constitute the drain, substrate and gate of the device of the present invention, wherein the gate is shared, so that...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More