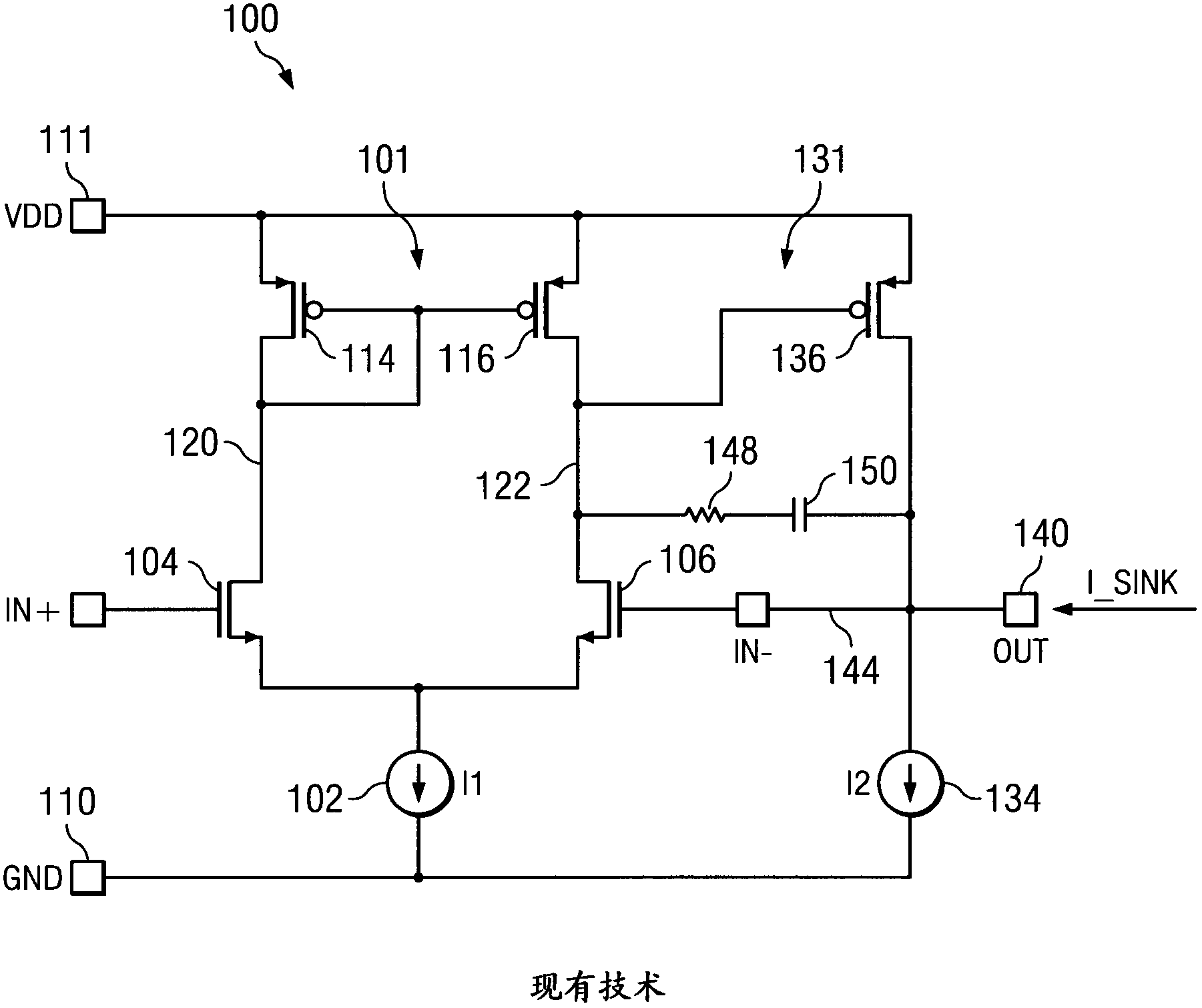

Operational transconductance amplifier with enhanced current sinking capacity

A current absorption and amplifier circuit technology, applied in the direction of DC coupled DC amplifiers, amplifiers with semiconductor devices/discharge tubes, amplifiers, etc., can solve the problems of insufficient absorption capacity of the current source 134, threat circuit, voltage rise, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

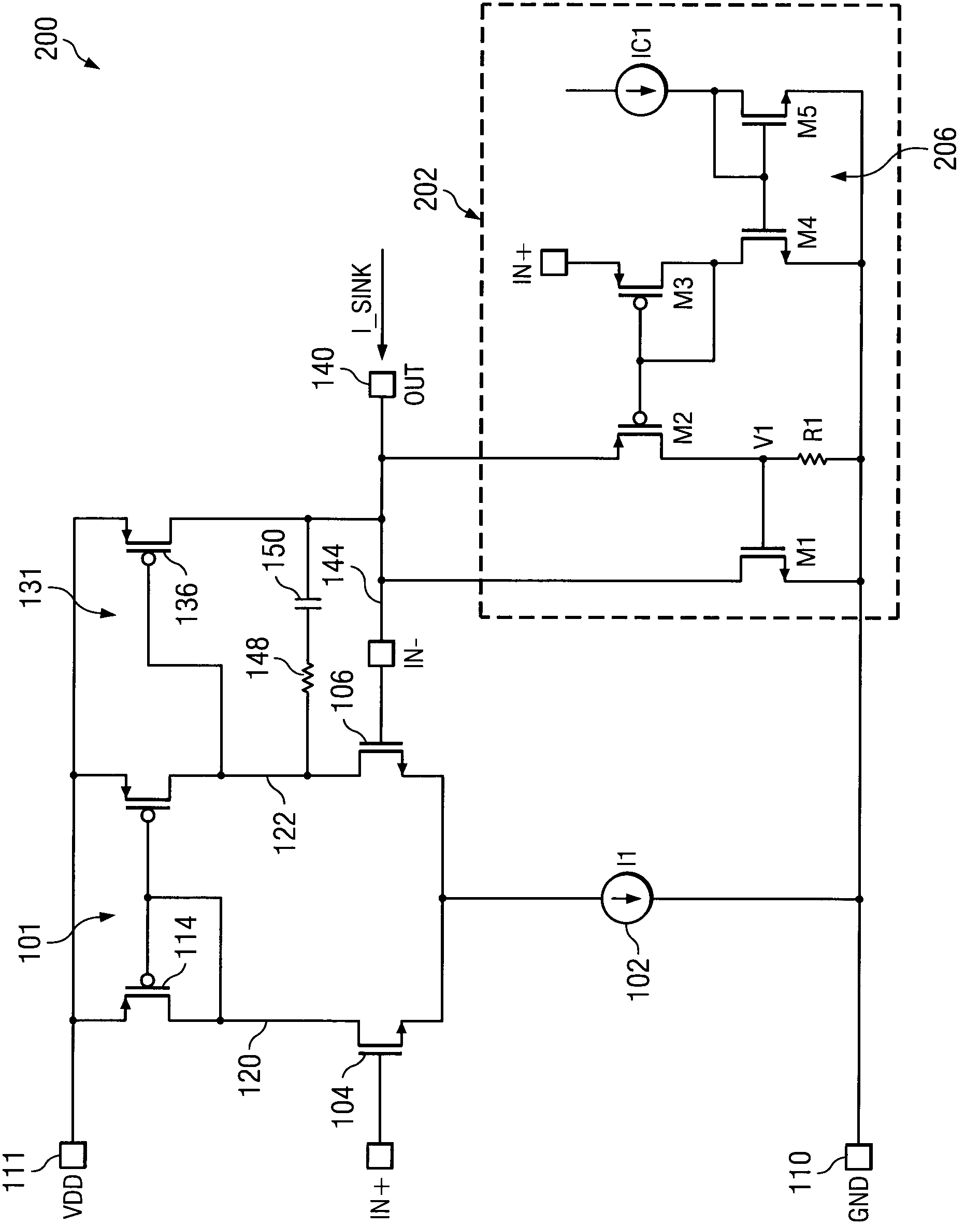

[0018] Now refer to figure 2 , which shows a circuit diagram of an operational transconductance amplifier 200 with enhanced current sinking capability.

[0019] figure 2 Like reference numerals refer to figure 1 Similar parts shown. I won't repeat it here figure 2 in such components, instead refer to the previously referenced figure 1 The description provided.

[0020] The difference between the amplifier 200 and the amplifier 100 is that the second current source 134 has been replaced by the current sink circuit 202 . The current sink circuit 202 includes a reference current source IC1 coupled to source current into a current mirror circuit 206 formed by transistors M4 and M5. Transistors M4 and M5 are n-channel type MOSFET transistors. The source terminals of transistors M4 and M5 are coupled to reference node 110 . The drain terminal of transistor M5 is coupled to receive the current sourced by reference current source IC1. The gate terminals of transistors M4 a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com