Chip physical integrity detecting device

A technology of integrity detection and detection devices, applied in the direction of platform integrity maintenance, etc., to achieve the effects of expanding coverage, reducing power consumption, and reducing area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

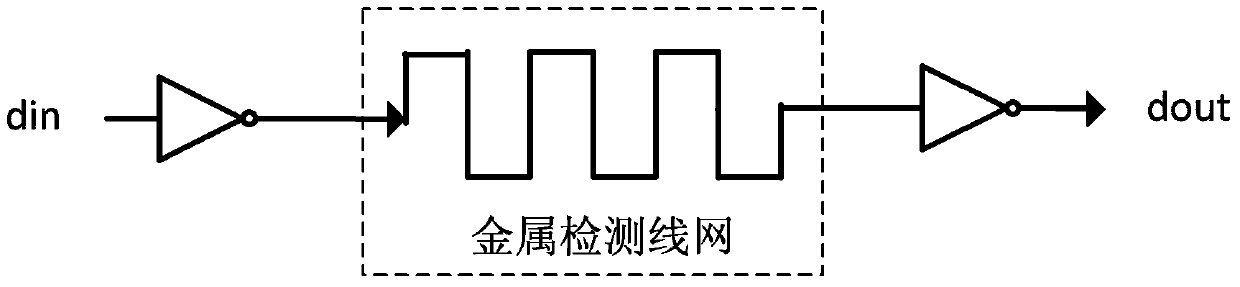

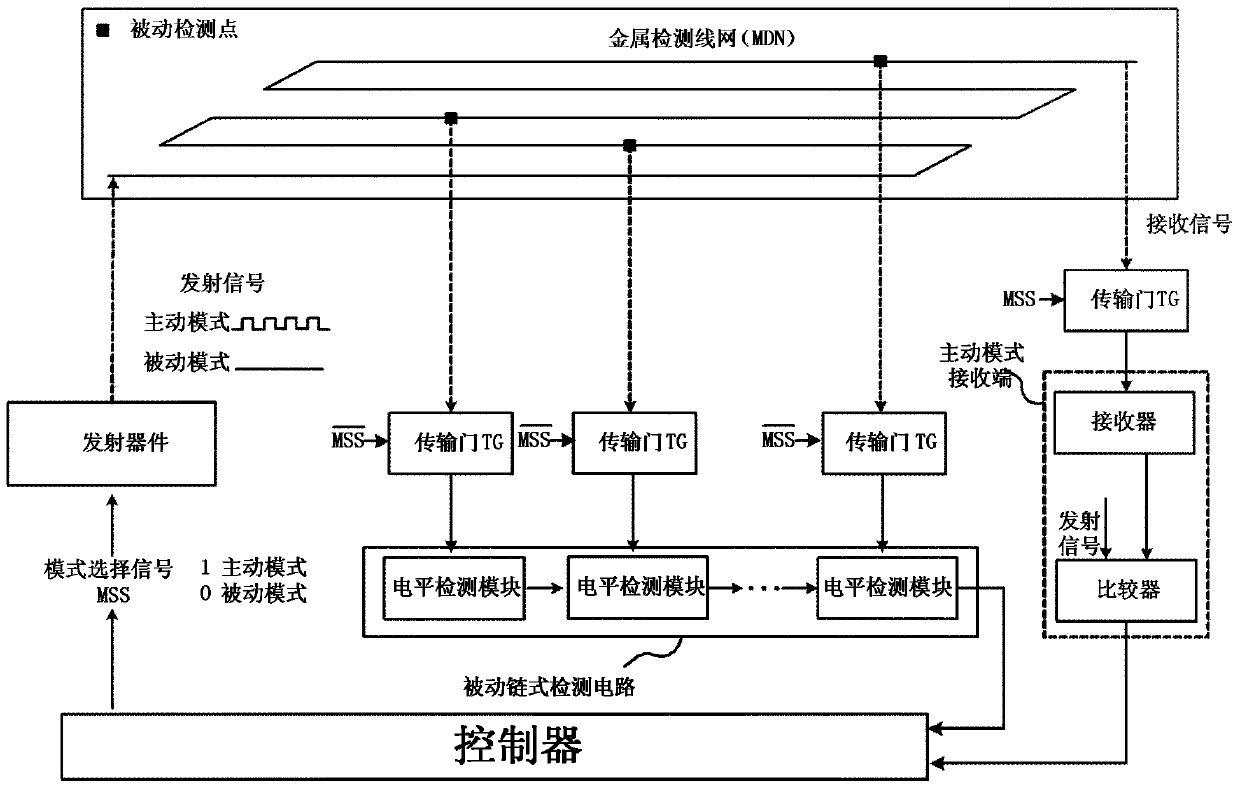

[0059] Active detection mode (Active Shield)

[0060] When the mode selection signal sent by the controller is 1, the active detection mode starts and the passive detection mode stops.

[0061] The transmission gate TG connected to the receiver is opened, and the transmission gate TG connected to the level detection module is closed.

[0062] Active detection mode includes the following 4 parts: transmitter, metal detection network, receiver, and comparator.

[0063] The emission signal generated by the transmitter when the active detection mode is valid is a square wave signal with an unfixed period. The emission signal corresponds to the metal detection network. For example, if the chip has 32 metal detection network, there are 32 detection signals. The waveform and phase of the signals are different.

[0064] The receiver receives the receiving signal from the metal detection network.

[0065] The comparator compares the transmitted signal and the received signal. If the two wavefor...

Embodiment 2

[0067] Passive detection mode (Passive Shield)

[0068] When the mode selection signal sent by the controller is 0, the passive detection mode starts and the active detection mode stops. The transmission gate circuit TG connected to the level detection module is opened, and the transmission gate circuit TG connected to the receiving device is closed.

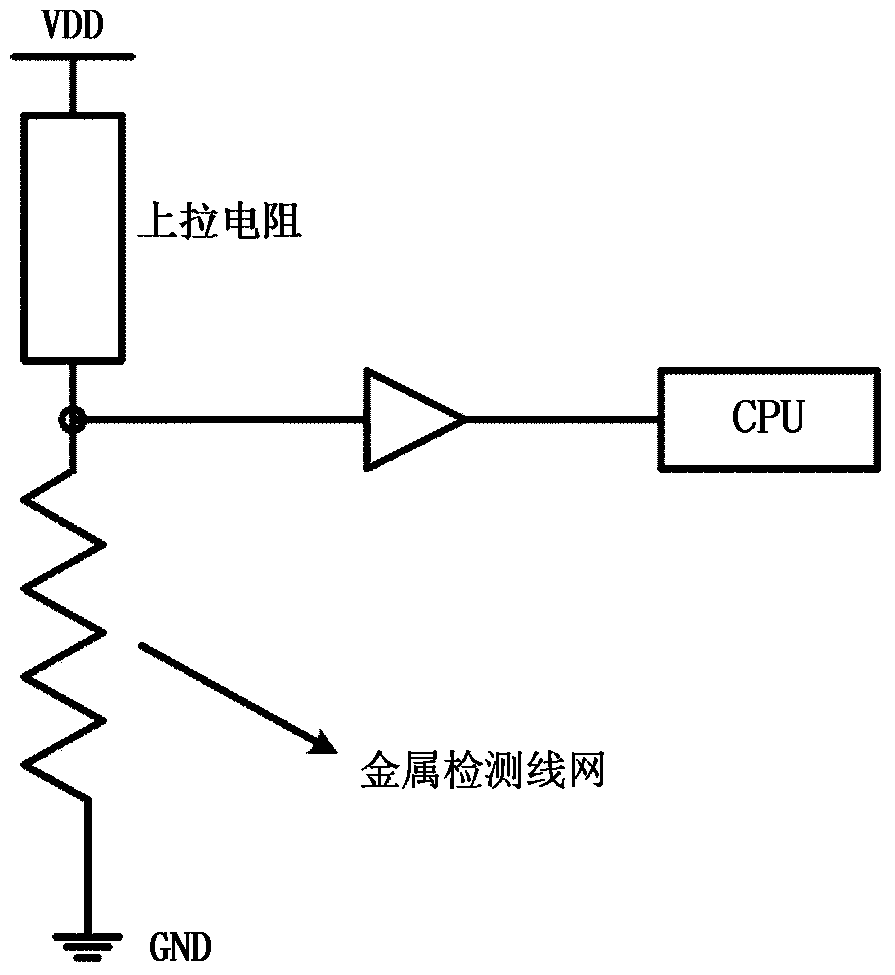

[0069] The detection input end of the level detection module is connected to the detection point of the metal detection wire net, and the level detection module can detect whether the potential of the detection point is normal or floating. If the potential of the detection point is floating, an abnormal value is output.

[0070] If the front-end input of the level detection module is an abnormal value, the abnormal value is output.

[0071] The level detection module is composed of digital standard units. The detection frequency of the level detection module is controlled by the detection frequency control signal.

[0072] Such as Fig...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More