Automatic hardware language transformation system

An automatic conversion, hardware language technology, applied in memory systems, program control design, instruments, etc., can solve the problems of complex use environment, high cost of commercial simulation software, unsuitable performance analysis and system evaluation, etc. The effect of reliability and convenient model checking

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0060] The present invention will be further described below in conjunction with the accompanying drawings.

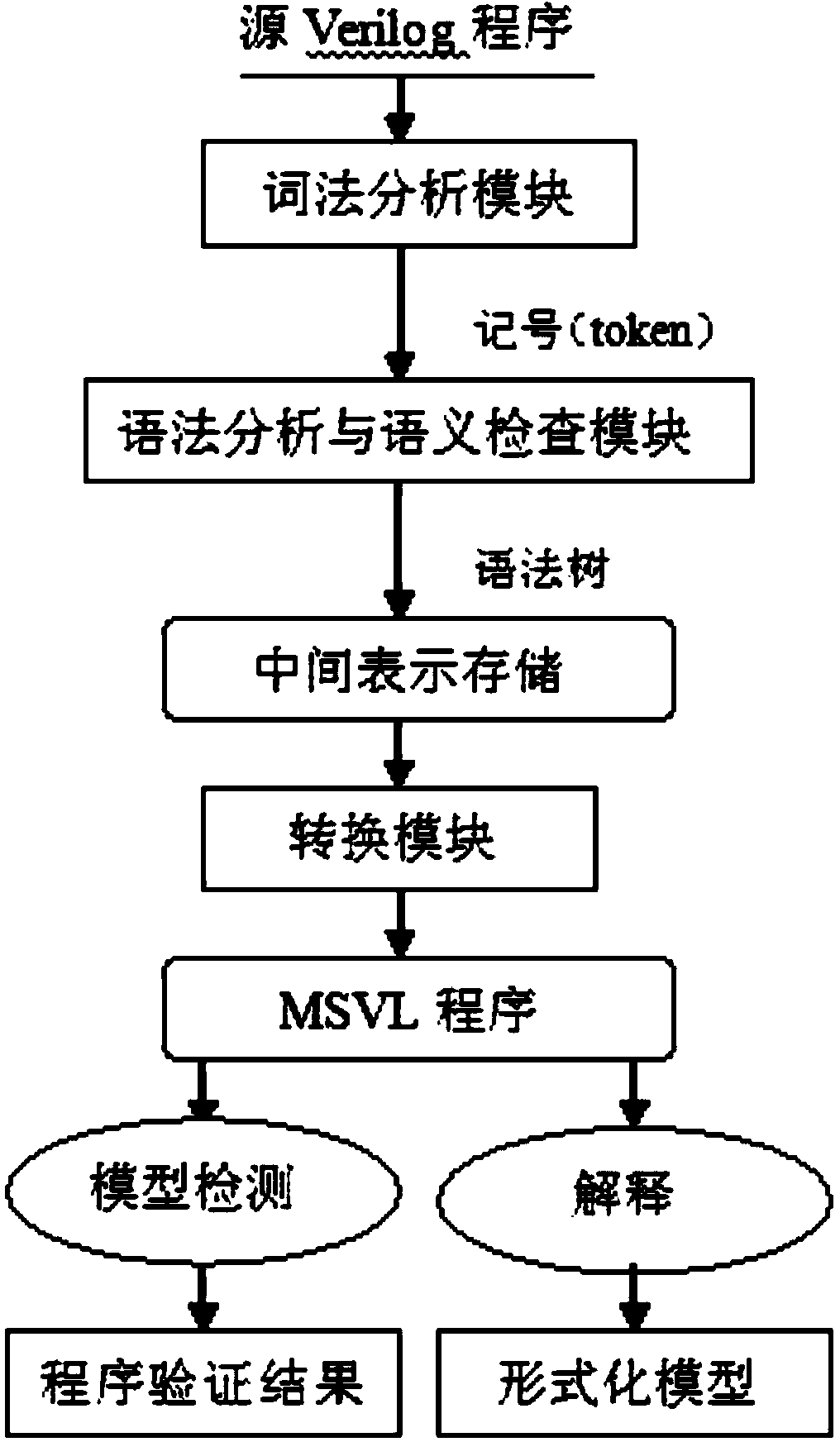

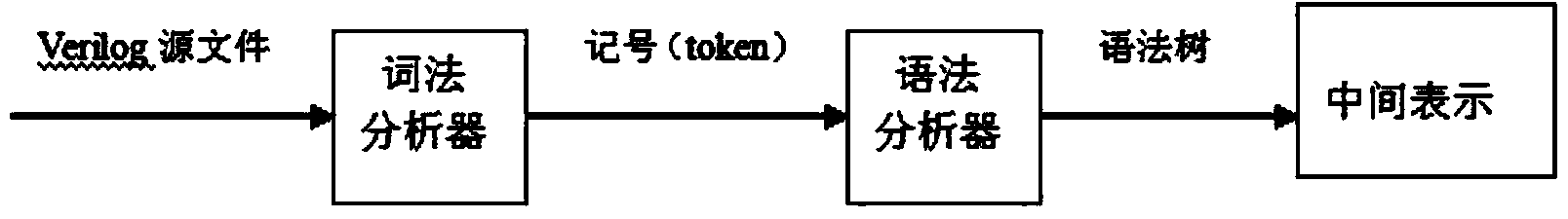

[0061] Such as figure 1 , figure 2 As shown, the present invention is a hardware language automatic conversion system, and the conversion system includes:

[0062] Lexical analysis module: there is a lexical analyzer for converting Verilog source files into tokens, including keywords, values, strings, identifiers, operators, spacers and comments in the Verilog language;

[0063] Grammatical analysis and semantic checking module: there is a grammatical analyzer for identifying the grammatical structure in the Verilog language; among them, semantic checking is performed while grammatical analysis;

[0064] Intermediate storage module: after lexical analysis, grammatical analysis, semantic inspection, and symbol processing, obtain an intermediate representation representing the Verilog source file, and store the intermediate file;

[0065] Conversion program module: u...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More