Device for verifying advanced microcontroller bus interface

A technology of micro-controller and bus interface, which is applied in the direction of instrumentation, electrical digital data processing, etc., can solve the problem of no mature VIP verification bus interface, etc., and achieve the effect of improving design verification efficiency and shortening the development cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

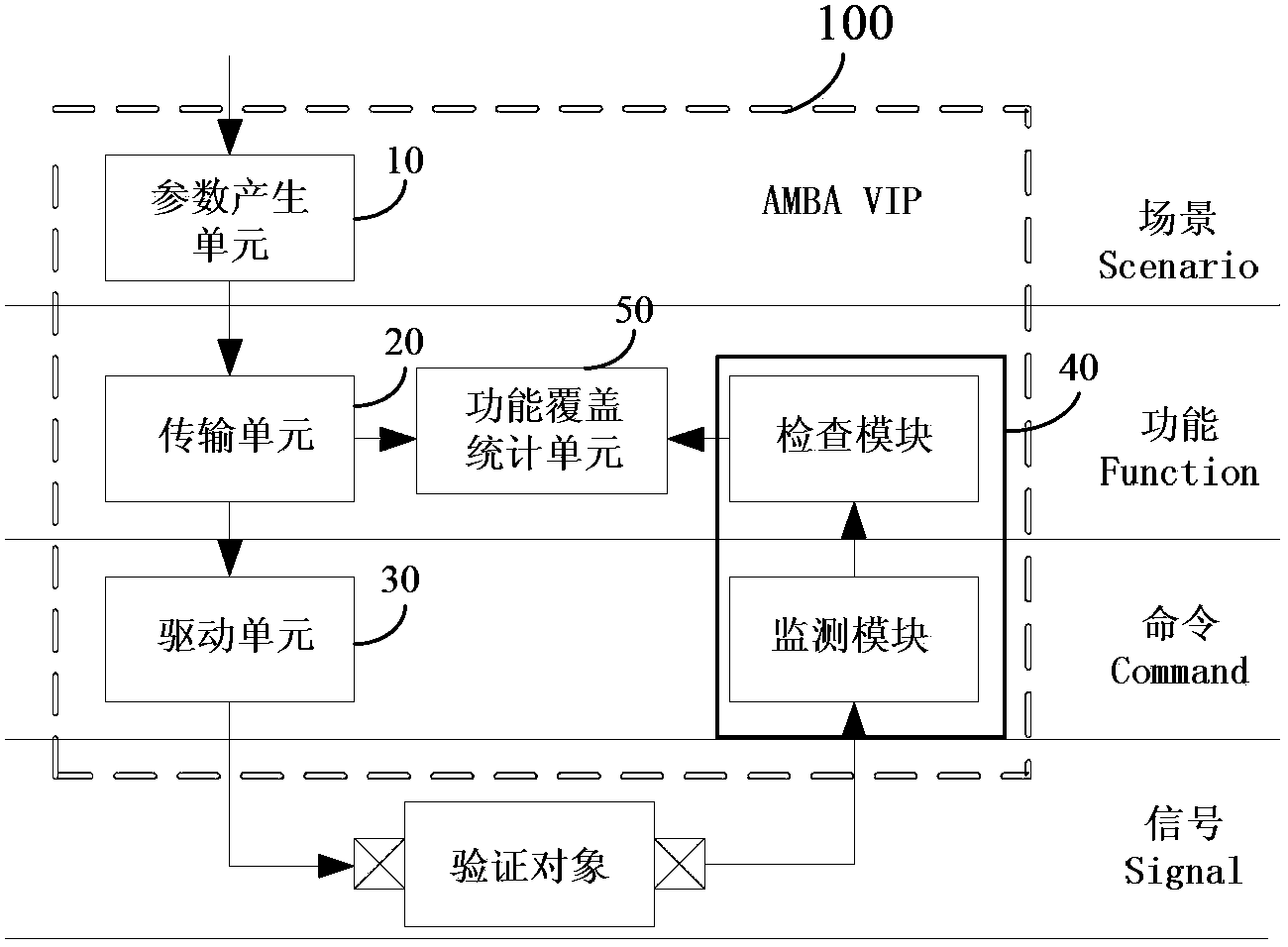

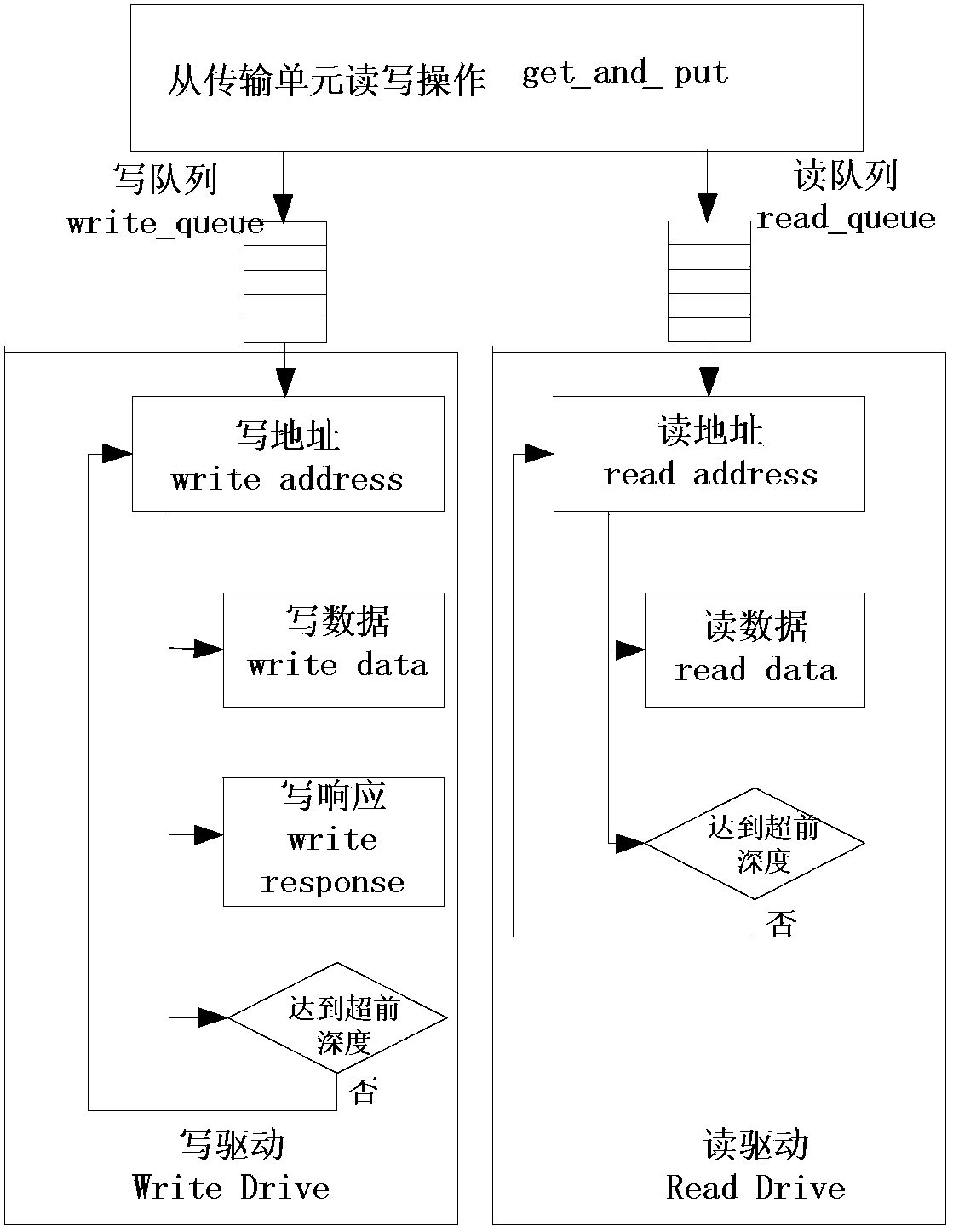

Method used

Image

Examples

test Embodiment T

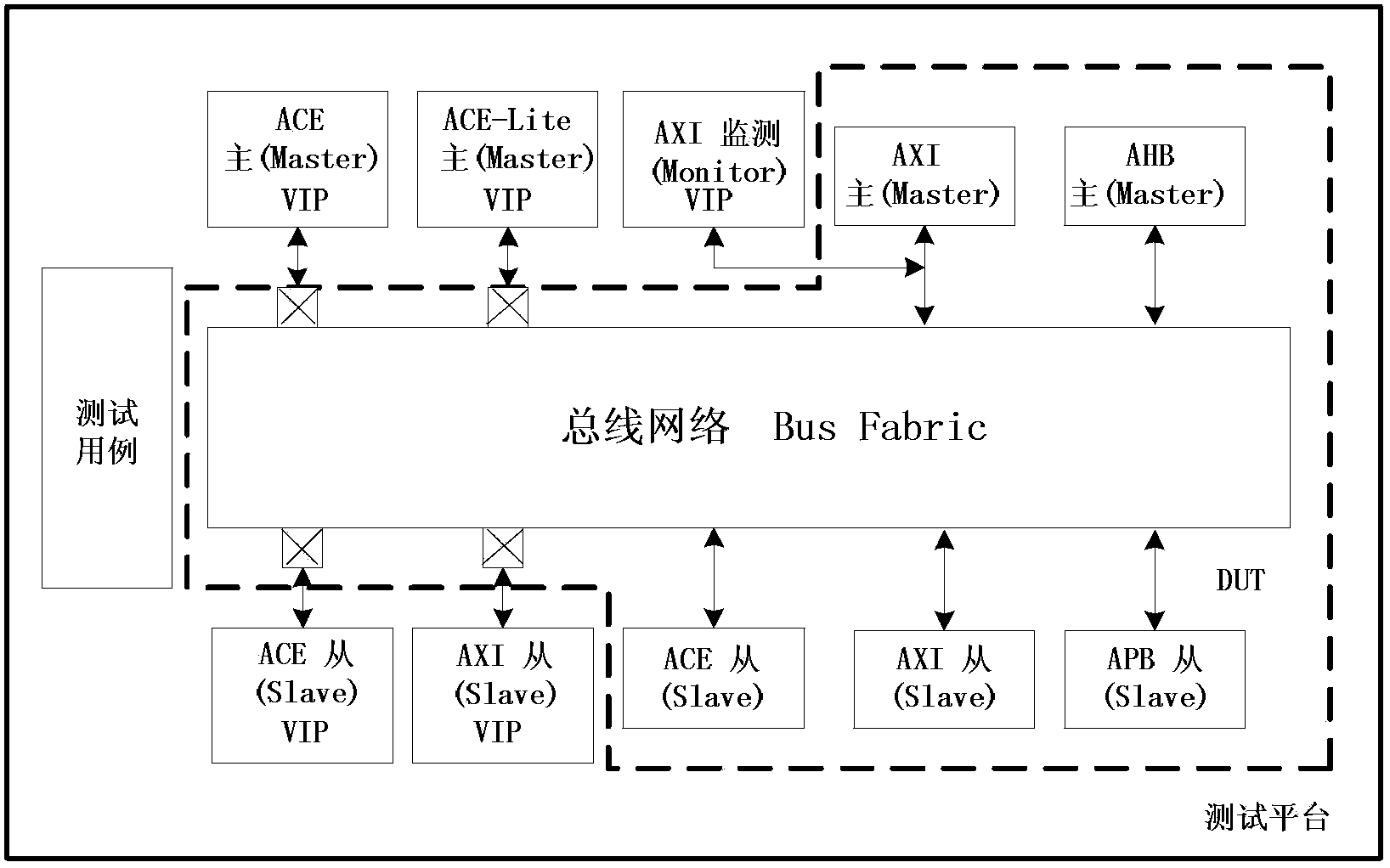

[0061] Such as image 3As shown in , it demonstrates a complete SoC verification environment integrating AMBA VIP. The white modules inside the dotted line can be regarded as components of DUT. VIP and Testcase are the verification parts related to VIP. In this example, ACE Master, ACE-Lite Master, AXI monitor, ACE slave and other VIPs are integrated, as well as advanced high-performance bus (AHB, Advanced High-performance Bus) and advanced peripheral bus (APB, Advanced Peripheral Bus). Communicate with the master through the interface. The test case Testcase is implemented by the system verilog program, and different random incentives can be generated by modifying the constraint of the transaction.

[0062] In summary, any AMBA-based system-level or module-level verification environment can directly reuse the device provided by the present invention. Before the development of the transmission module of the verification object DUT is completed, the VIP device provided by the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com