Signal processing system based on FPGA (Field Programmable Gate Array) of acoustic Doppler current profiler

An acoustic Doppler and signal processing technology, applied in the field of FPGA technology, can solve problems such as cache emptying, affecting system computing performance, and inability to obtain computing performance, achieving the effect of complete functions and strong scalability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The concrete implementation process of the present invention is described below in conjunction with accompanying drawing:

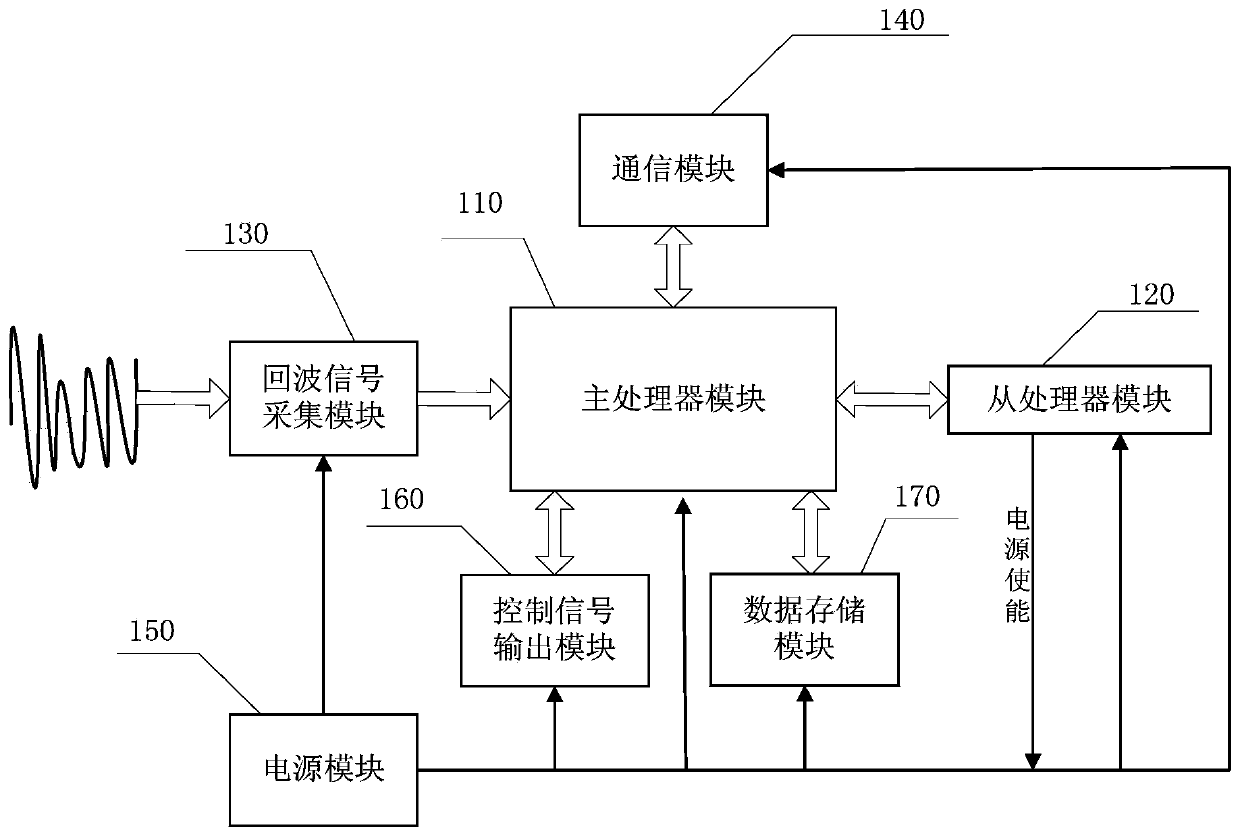

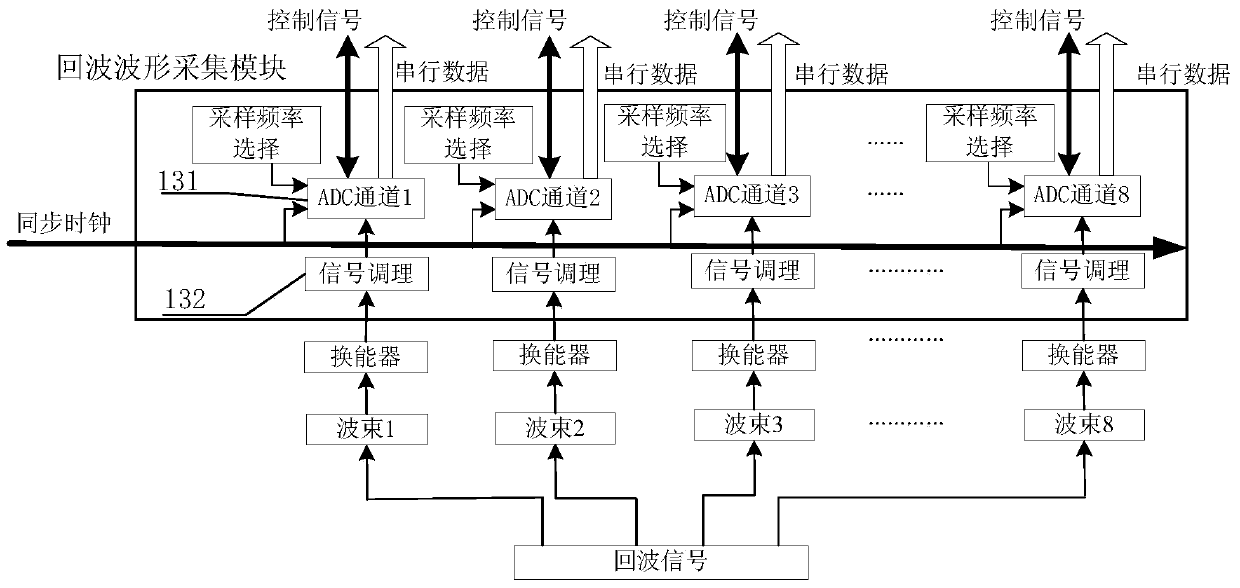

[0029] Such as figure 1 As shown, the structural block diagram of the FPGA-based acoustic Doppler current profiler signal processing system. The system consists of a main processor module (110), a slave processor module (120), an echo signal acquisition module (130), a communication module (140), a power supply module (150), a control signal output module (160), a data storage Module (170) is composed.

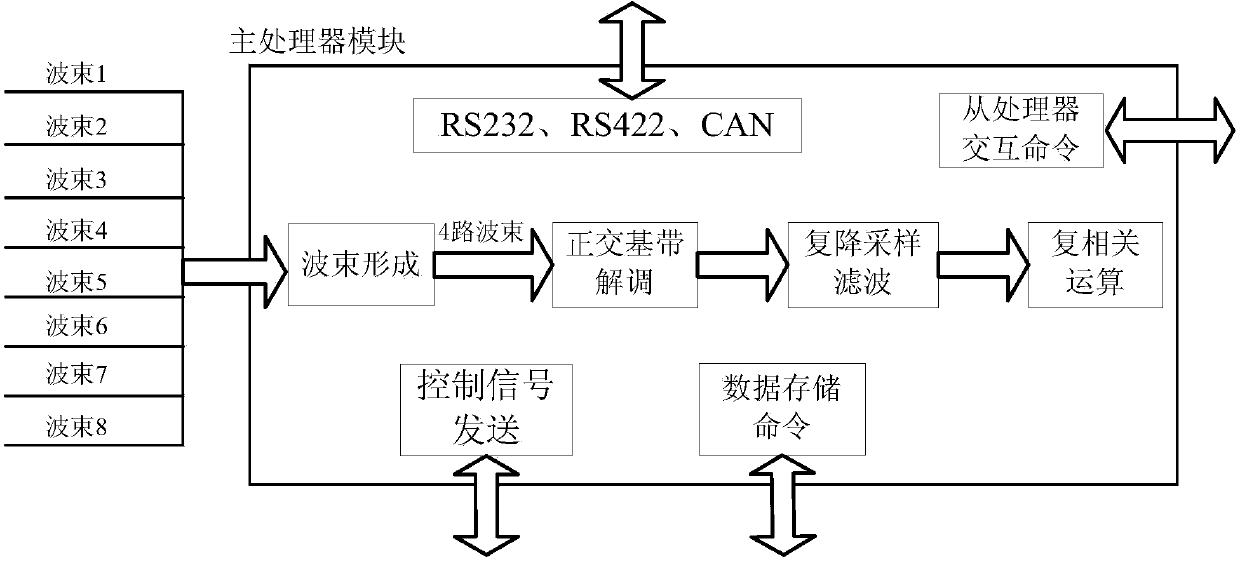

[0030] Wherein, the main processor module (110) adopts the FPGA processor of Xilinx Company as the core, cooperates with the DDR2 circuit and the Flash storage circuit, and is composed of the slave processor module (120), the echo signal acquisition signal module (130), The communication module (140) and the control signal output module (160) are connected to manage the working process of the above modules. Moreover, the main processor module (1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More