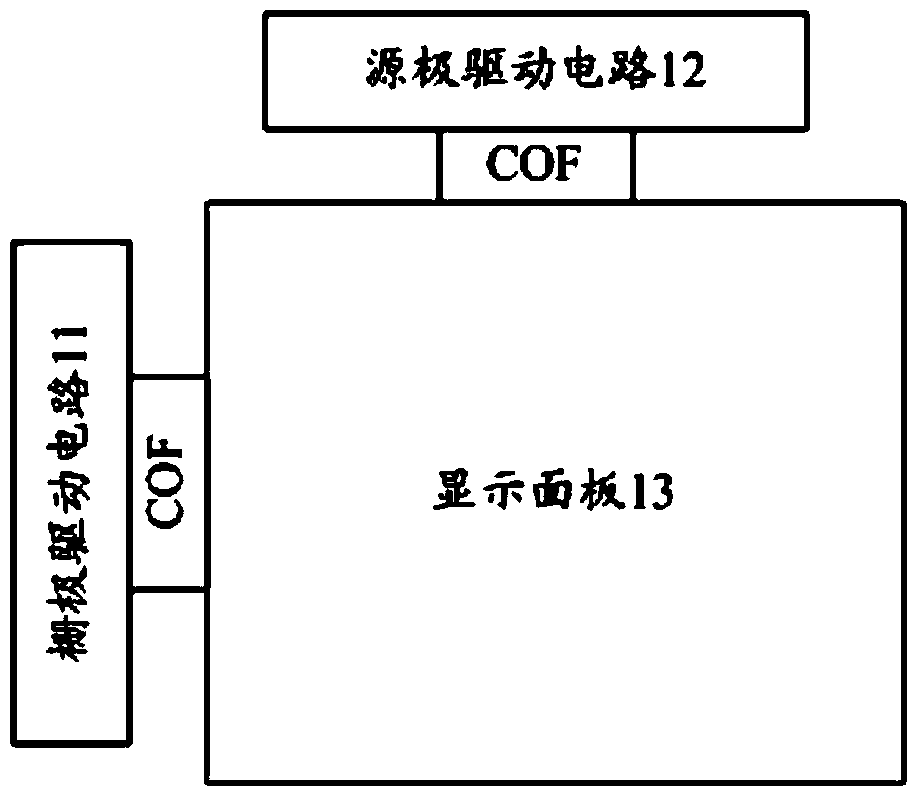

Grid driving circuit, array substrate, display device and driving method

A technology for a gate drive circuit and a display device, which is applied in the fields of gate drive circuits and array substrates, can solve the problems of high overall power consumption of the display device, and achieve the effects of ensuring display quality and reducing overall power consumption.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

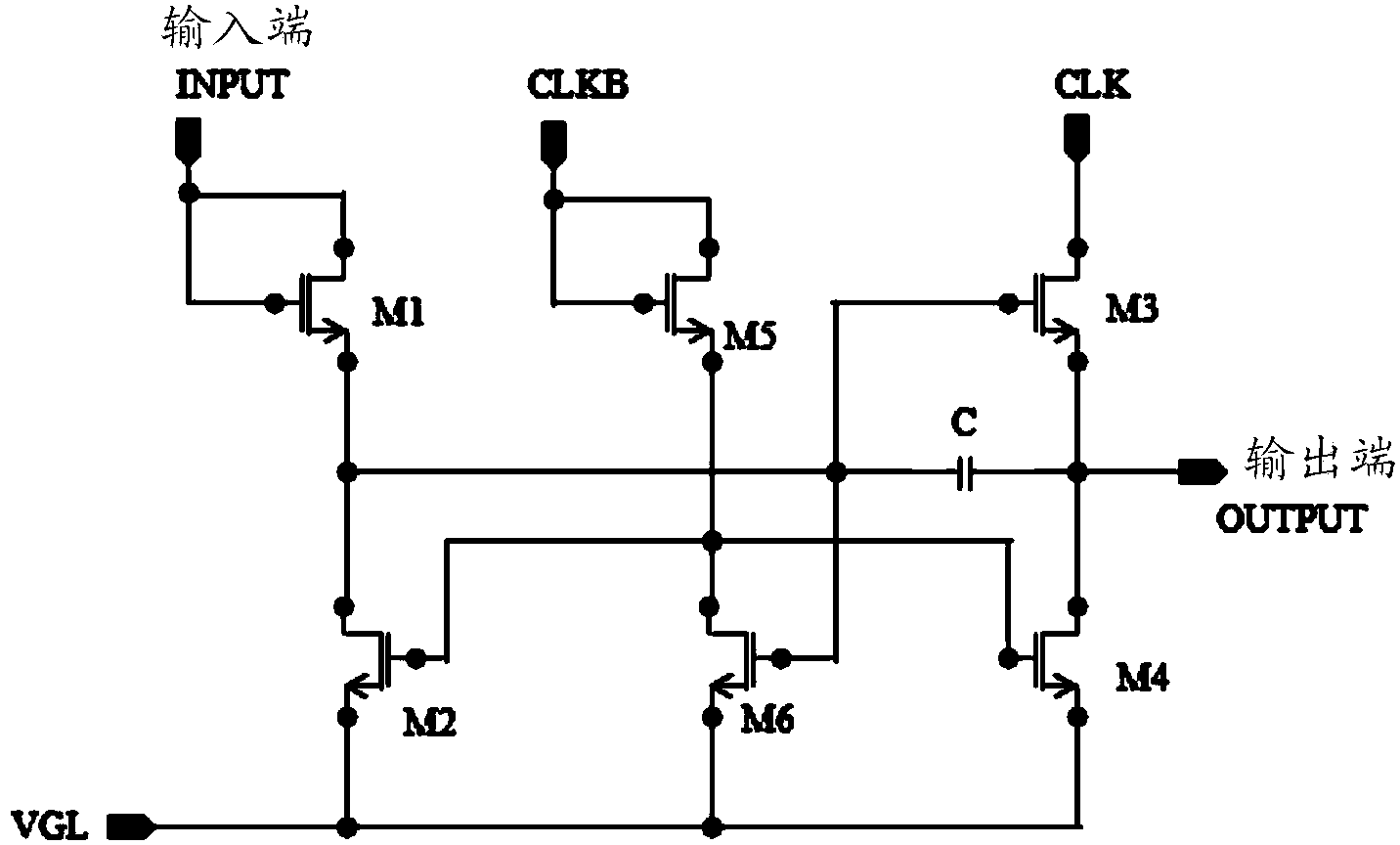

Embodiment 1

[0112] The driving method provided by the embodiment of the present invention will be described below in combination with the first embodiment.

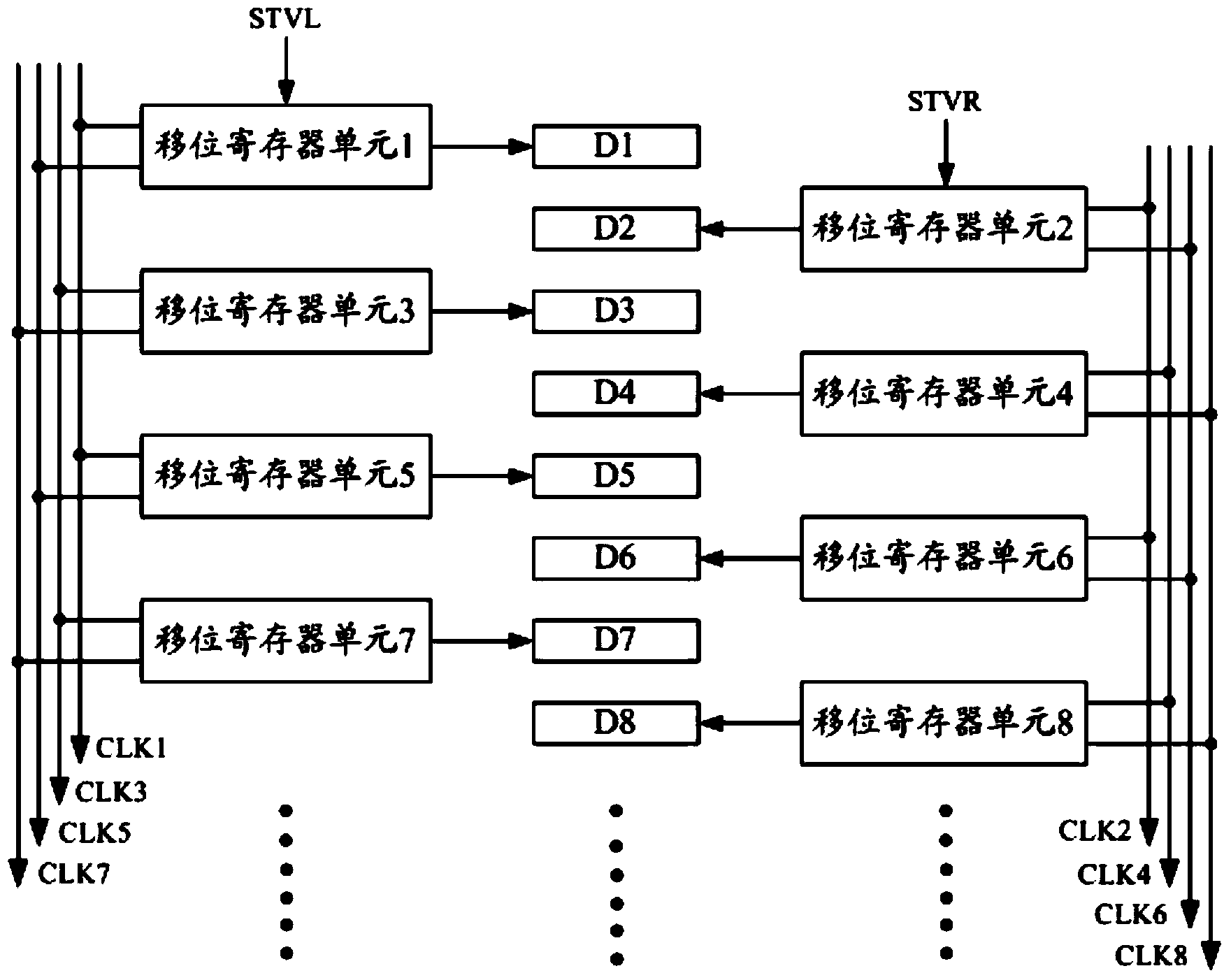

[0113] Embodiment 1, this embodiment is still based on figure 2 The structure diagram of the gate driving circuit shown is taken as an example to illustrate the first driving method, and other situations are similar, and will not be listed here.

[0114] Figure 4 Shown is the input timing diagram of the first sub-circuit of the gate driving circuit of this embodiment, and the input timing diagrams of other sub-circuits are similar, and will not be listed here. Figure 4 Including the frame start signal (STVL signal and STVR signal), where the high-level pulse of the STVL signal is output, and the high-level pulse of the CLK1 / CLK3 / CLK5 / CLK7 signal is output in sequence, so that the shift register 1 / 3 / 5 / 7 generates the gate scanning signal for driving the gate signal lines of the 1 / 3 / 5 / 7 row (that is, the gate scanning signal of t...

Embodiment 2

[0122] Embodiment two, this embodiment is still based on figure 2 The structure diagram of the gate driving circuit shown is taken as an example to illustrate the first driving method, and other situations are similar, and will not be listed here.

[0123] In this embodiment, on the basis of the first embodiment, the pixel pre-charging process is added. For the input timing diagram of the first sub-circuit of the gate drive circuit, refer to Figure 8 As shown, the input timing diagrams of other sub-circuits are similar to this, and will not be listed here. Figure 8The pulse duration of the high-level pulse of the STVL signal is still H1, and the pulse duration of the high-level pulse of the generated clock control signal CLK1 / CLK3 / CLK5 / CLK7 signal is H1+H2, and the high-level pulse of the STVR signal The pulse duration of the pulse is still H1, and the pulse duration of the high-level pulse of the generated CLK2 / CLK4 / CLK6 / CLK8 signal is H1+H2, that is, the adjacent two clo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More