Non-volatile memory device with clustered memory cells

A memory cell, non-volatile technology, used in static memory, read-only memory, digital memory information, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

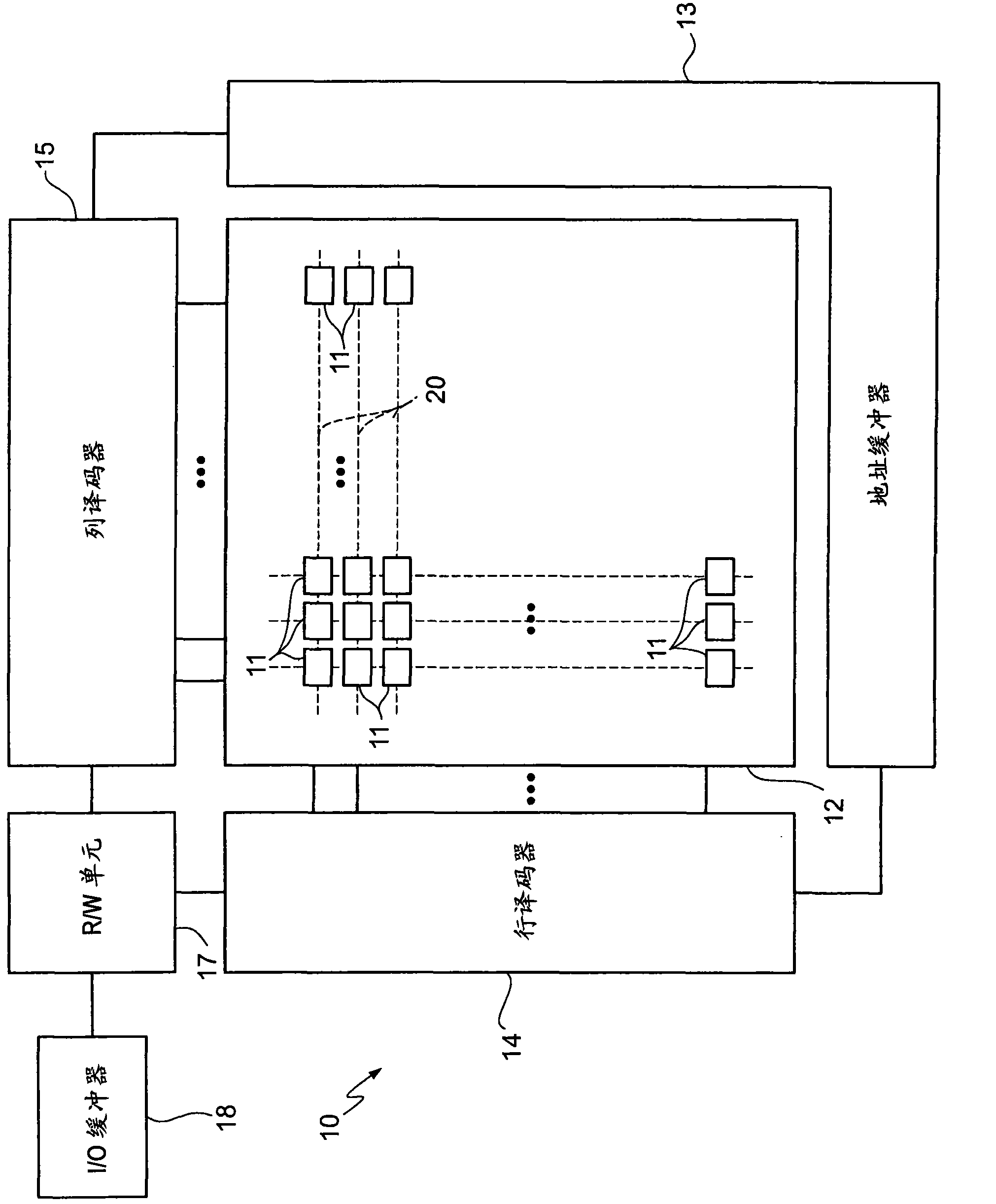

[0021] refer to figure 2 , the differential nonvolatile memory device is labeled with reference numeral 10 and includes a plurality of nonvolatile logical memory cells 11 organized in logical rows 20 and logical columns 21 to form Array 12 (eg, 128-512 rows and 512-1024 columns).

[0022] The memory device 10 further includes an address buffer 13, a row decoder 14, a column decoder 15, a read / write unit 17, and an input / output buffer 18 (hereinafter, the term "write" is used to neutrally refer to a logical memory unit 11 program and erase operations).

[0023] Address buffer 13 receives addresses of cells selected from pages of array 12 . The row and column portions of the address are provided to row decoder 14 and column decoder 15 , which select corresponding rows and columns of array 12 .

[0024] The read / write unit 17 controls the row decoder 14 and the column decoder 15, and has components required for programming, erasing and reading operations of memory cells (incl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More