High-speed seamless capture pulse power statistics measuring method

A technology of statistical measurement and pulse power, applied in the field of measurement, can solve the problems of low data extraction rate, inability to achieve long-term data sampling and analysis without data loss, and limited data volume, and achieve the effect of fast sampling rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

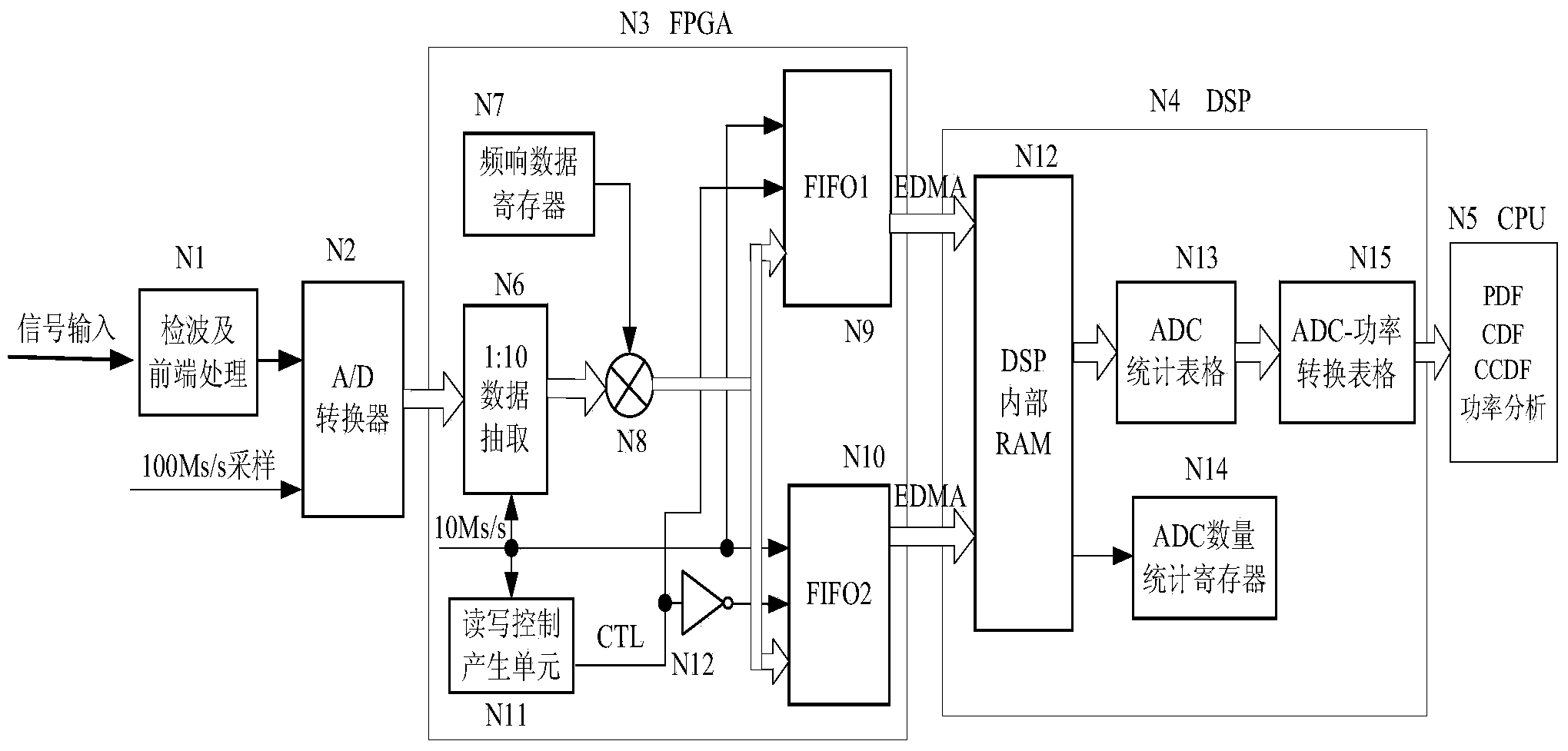

[0029] The circuit of the present invention mainly includes wave detection and front-end processing unit N1, A / D (analog / digital) converter N2, FPGA (programmable logic device) N3, DSP (digital signal processor) N4, CPU (central processing unit) N5 .

[0030] In the detection and front-end processing unit N1, the microwave signal is detected to obtain the envelope signal of the microwave signal. After the detected envelope signal is logarithmically amplified and linearly adjusted, the detection voltage is adjusted to meet the requirements of the A / D converter N2 input range. N2 is a 14-bit, 100Ms / s A / D converter, which converts the detection voltage into ADC data, and sends the ADC data to FPGA N3.

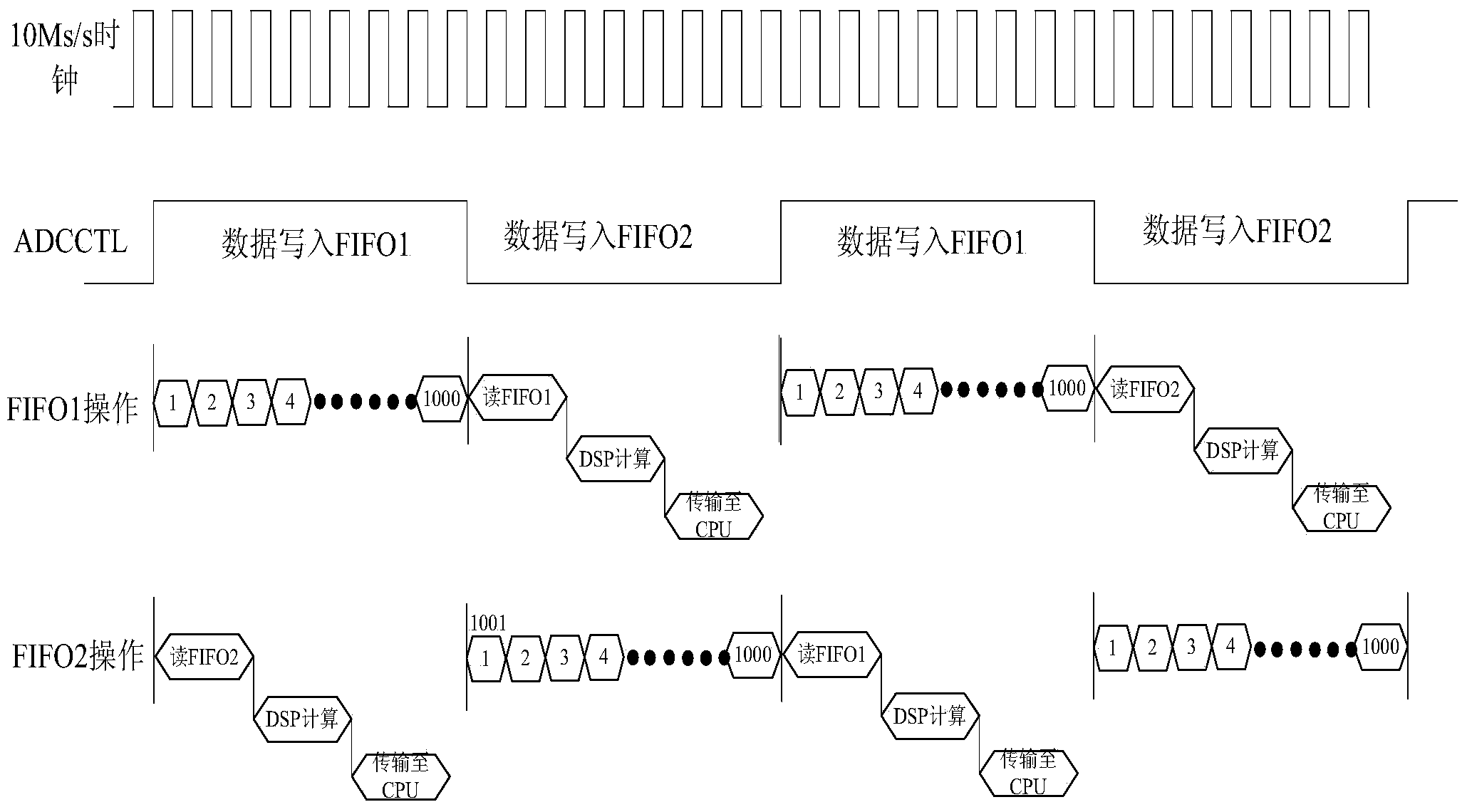

[0031] Due to the influence of DSP and CPU processing speed, statistical measurement without data loss cannot be completed at a rate of 100Ms / s, so the present invention performs slow-down processing on seamlessly captured statistical measurement. The speed reduction process is ...

Embodiment 2

[0047] On the basis of the foregoing embodiments, further, as Figure 1-Figure 2 As shown, a high-speed seamless capture pulse power statistical measurement method, which includes the following steps:

[0048] Step 1: In the detection and front-end processing unit, the microwave signal is detected to obtain the envelope signal of the microwave signal. After the envelope signal is logarithmically amplified and linearly adjusted, the detection voltage is adjusted to meet the requirements of the A / D converter. The input range, and then convert the detection voltage to ADC data, and send the ADC data to the FPGA;

[0049] Step 2: Perform speed reduction processing, which is completed by the 1:10 data extraction unit inside the FPGA. The extraction rate is 10Ms / s, and the ADC rate after extraction is 10Ms / s;

[0050] Step 3: The frequency response compensation of the power measurement is completed in the FPGA. The DSP first writes the frequency response data into the frequency res...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More