Cache Fault Tolerance Mechanism of Embedded Processor

An embedded processor, cache technology, applied in the direction of response error generation, redundant code error detection, etc., can solve problems such as increasing cache access time, reducing processor performance, increasing access time, etc., to improve flexibility performance, increased time, the effect of circuit simplicity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

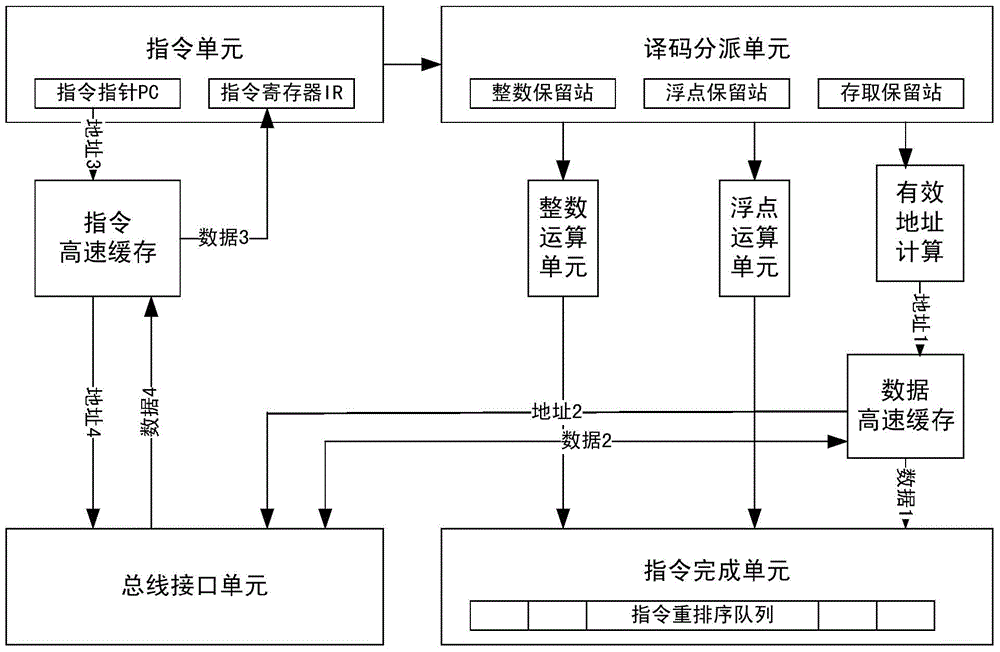

[0031] The preferred embodiments of the present invention are given below in conjunction with the accompanying drawings to describe the technical solution of the present invention in detail.

[0032] Such as Figure 5 Shown, the cache fault-tolerant mechanism of embedded processor of the present invention comprises the following steps:

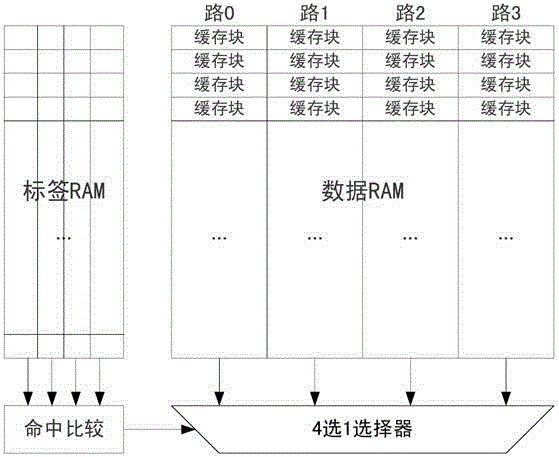

[0033] In step 1, there are instruction cache and data cache in the embedded processor; the instruction cache has a read port and a write port. The read port of the instruction cache is connected to the instruction unit. The data cache has a readable and writable port and a write-only port; when writing the cache, the write port generates a parity code according to the data on the write data bus; when generating the parity code, it is in bytes, that is One byte generates one bit of parity, two bytes generates two bits of parity, and so on. The generated parity code and the data written on the data bus are simultaneously written to the data ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com