A jtag emulator automatically closes the monitoring timer circuit

A monitoring timer and automatic shutdown technology, applied in the direction of instruments, simulators, program control, etc., can solve problems such as debugging failure, system reset, and increased debugging complexity, so as to ensure reliability, simplify operation, and simplify debugging steps Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0013] The present invention will be described in detail below in conjunction with the accompanying drawings.

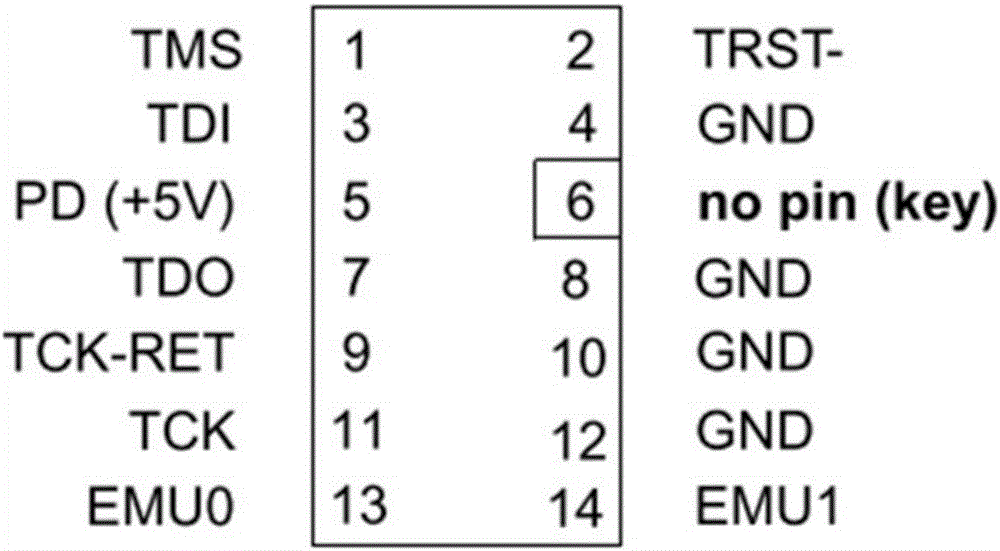

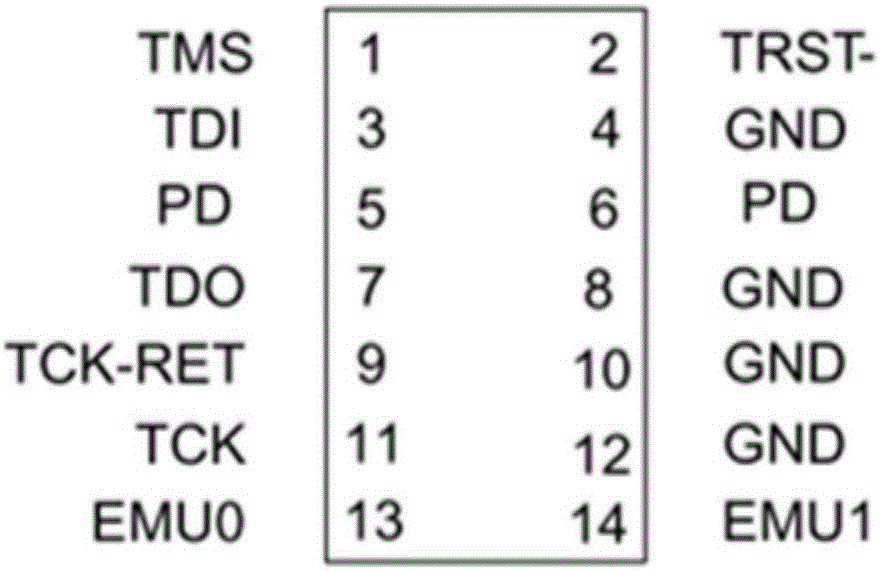

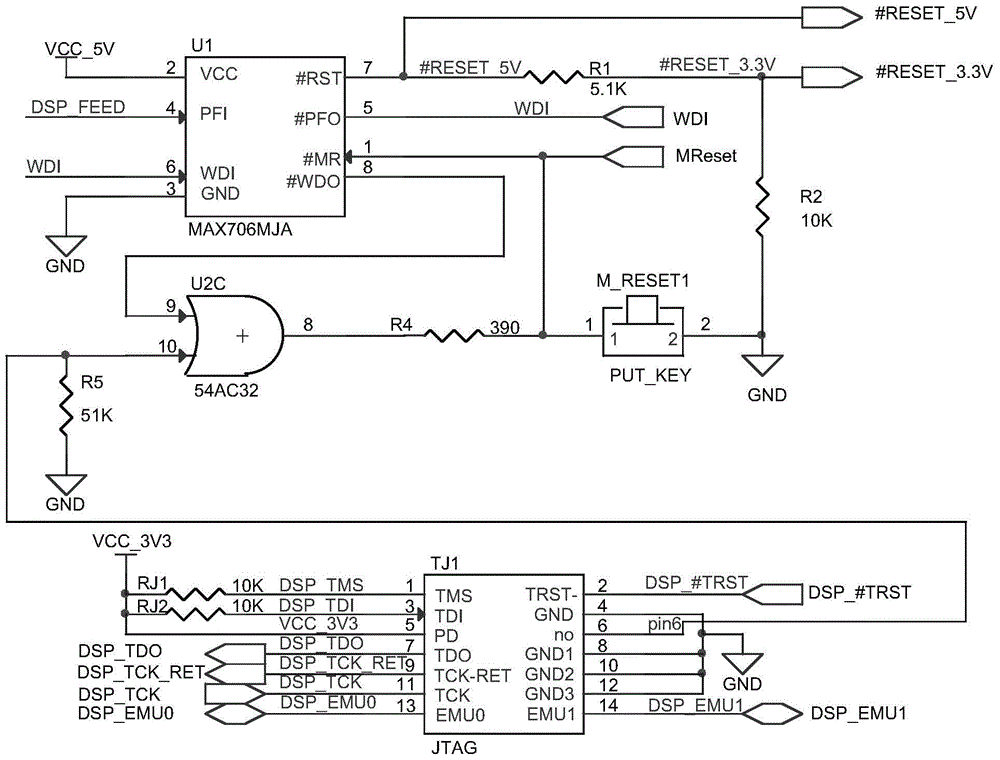

[0014] The present invention provides a kind of JTAG emulator automatic shutdown monitoring timer circuit, comprising monitoring timer U1, OR gate U2C and JTAG connector slot TJ1; Watchdog output pin #WDO of monitoring timer U1 is connected to OR gate U2 One input terminal 9 of the OR gate U2, the other input terminal 10 of the OR gate U2 is connected to the pin 6 of TJ1, and at the same time connected to one end of the resistor R5, the other end of the resistor R5 is grounded, and the output terminal 8 of the OR gate U2 is connected to one end of the resistor R4 , the other end of the resistor R4 is connected to the manual reset pin #MR of the watchdog timer U1, such as figure 1 shown.

[0015] The specific working mode of the circuit is as follows:

[0016] (1) In the normal working stage of the system, there is no need to debug, and the emulator is not connecte...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More