Chip testing data transmission method based on dual-run-length alternative coding

A data transmission method and chip testing technology, applied in the field of system chip test data processing, can solve the problems of high test cost, small decoding circuit overhead, long decoding time, etc., achieve the effect of wide program adaptability and reduce chip overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] The present invention will be further described below in conjunction with the accompanying drawings.

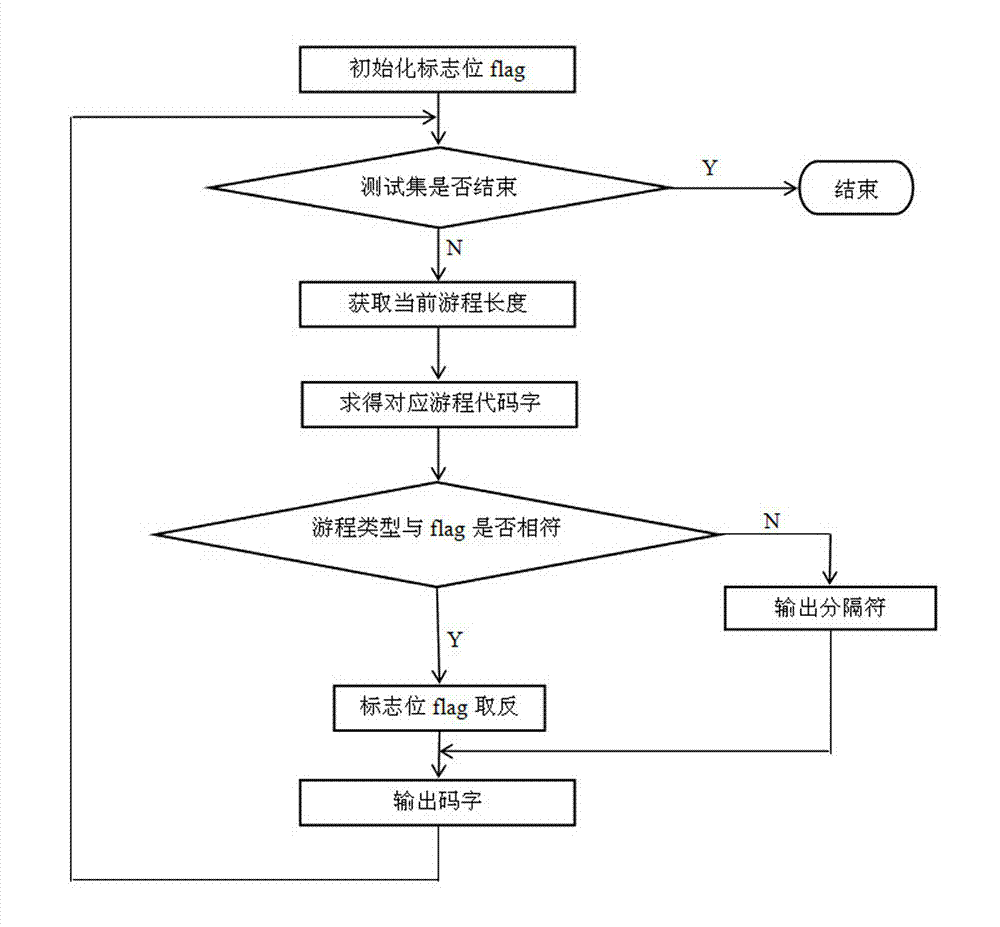

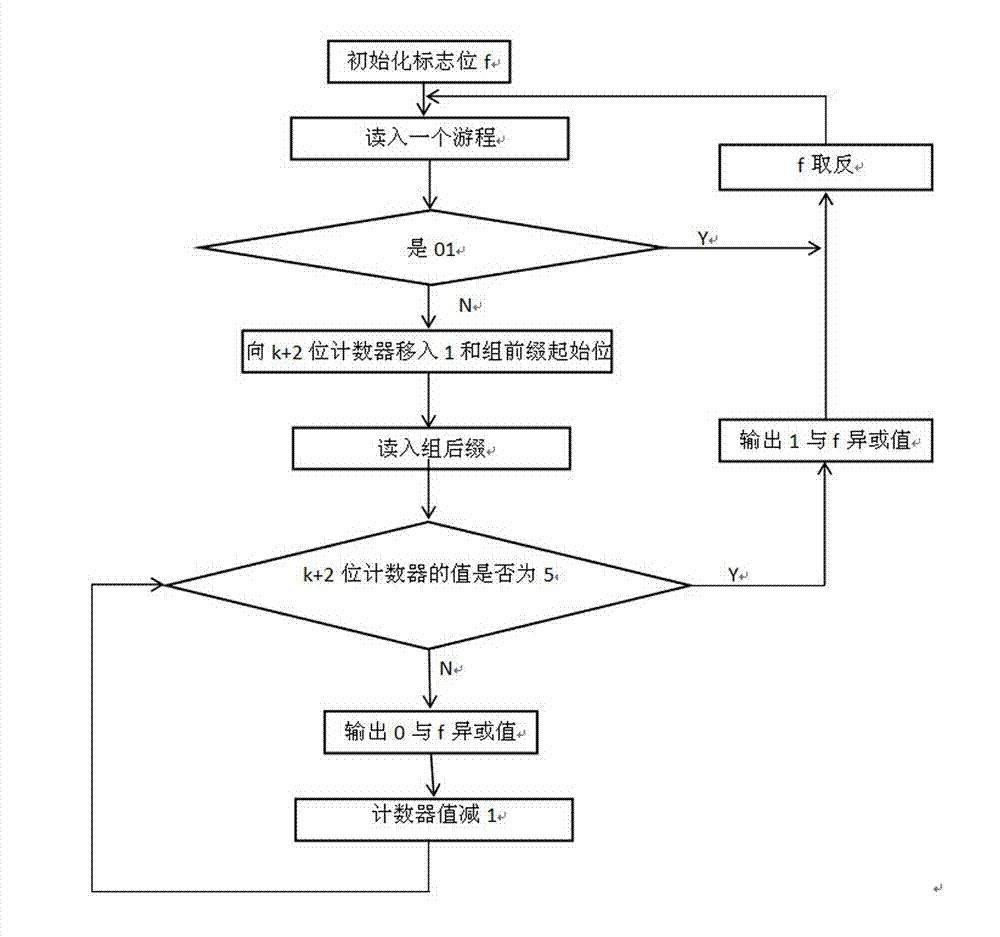

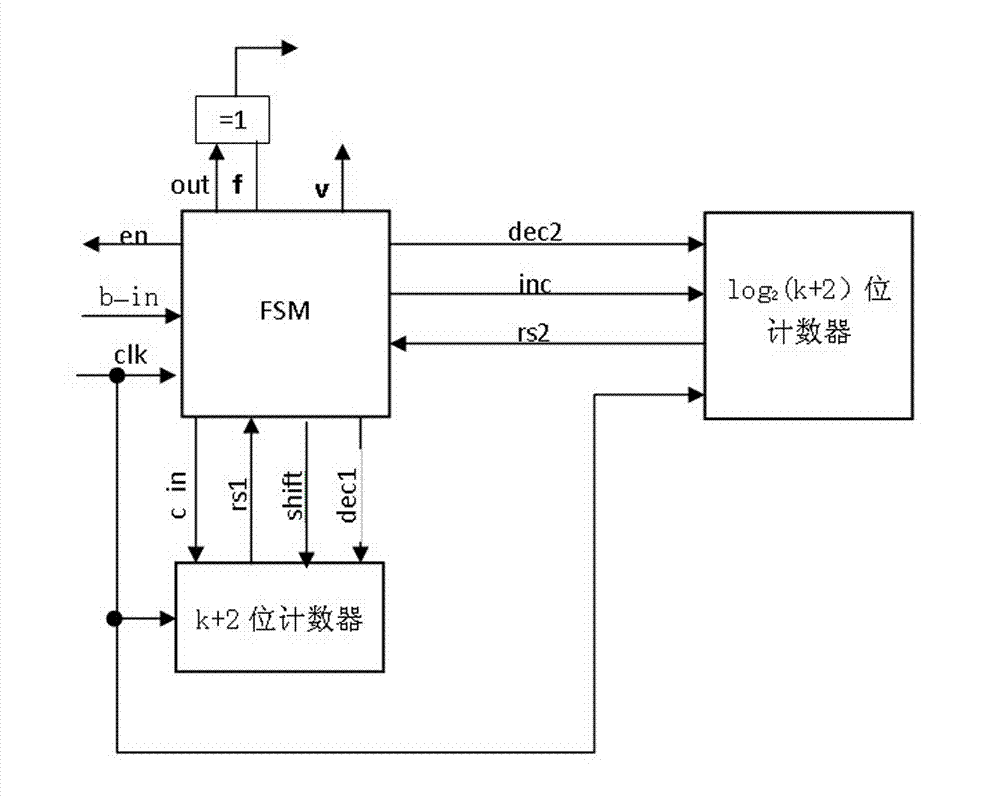

[0040] Such as figure 1 , figure 2 , image 3 It can be seen that the chip test data transmission method based on double-run alternate coding of the present invention comprises the following steps:

[0041] A. If figure 1 It can be seen that the encoding steps include:

[0042] (1) Initialize the flag bit flag, which corresponds to an expected run length type; and record the initial value of the flag as f; the purpose of recording the initial value of the flag as f is to provide the first run length type reference for the subsequent decoding process.

[0043] (2) read the test data coding set bit by bit, obtain the current run length, and obtain the corresponding run length code word, the described run length code word is made up of the group prefix and the group suffix corresponding to each other; the described group prefix is a 0 run or 1 run determined by th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More