Chip packaging method and structure

A chip packaging structure and chip packaging technology, applied in the direction of semiconductor/solid-state device parts, semiconductor devices, electrical components, etc., can solve the problems of poor reliability of chip packaging methods, and achieve the effect of simplifying the process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

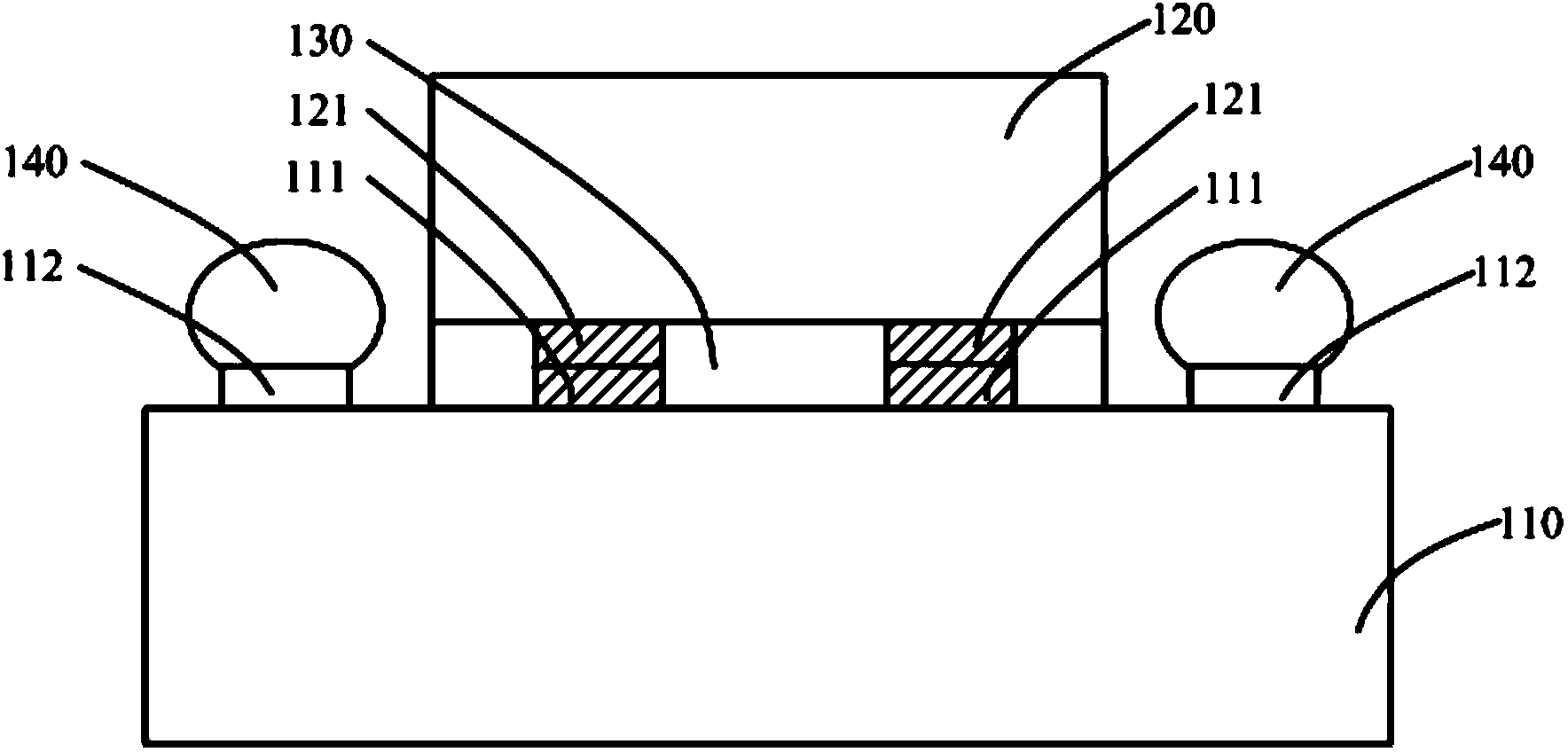

[0035] Usually, when two chips of different sizes are packaged in a system-in-package, the connection area between the big chip and the small chip is only the size of the small chip. Please refer to figure 1 , figure 1 It is a schematic cross-sectional structure schematic diagram of system-in-package for two chips with different sizes in the prior art, including: a first chip 110, the surface of the first chip 110 has a first pad 111 and a third pad 112; Chip 120, the area of the second chip 120 is smaller than the first chip 110, the surface of the second chip 120 has a second pad 121, the second pad 121 on the surface of the second chip 120 is connected to the The first pads 111 on the surface of the first chip 110 are correspondingly bonded together; the insulating glue 130 is located in the gap between the surface of the first chip 110 and the surface of the second chip 120, and is used to bond the first chip 110 and the second chip 120; solder balls 140, located on th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com