FPGA zero-dynamic power consumption design method

A design method and dynamic power consumption technology, applied in the direction of data processing power supply, etc., can solve problems such as invalid power consumption, and achieve the effect of reducing power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The technical solutions in the embodiments of the present invention will be clearly and completely described and discussed below in conjunction with the accompanying drawings of the present invention. Obviously, what is described here is only a part of the examples of the present invention, not all examples. Based on the present invention All other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

[0032] In order to facilitate the understanding of the embodiments of the present invention, specific embodiments will be taken as examples for further explanation below in conjunction with the accompanying drawings, and each embodiment does not constitute a limitation to the embodiments of the present invention.

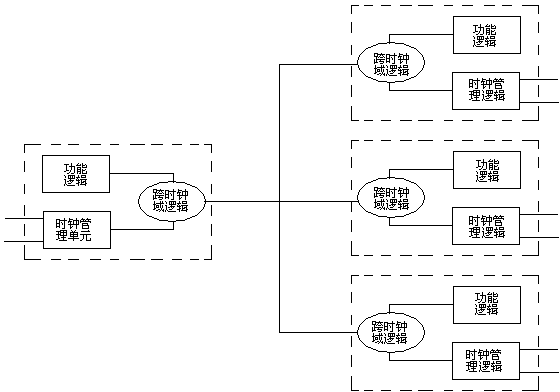

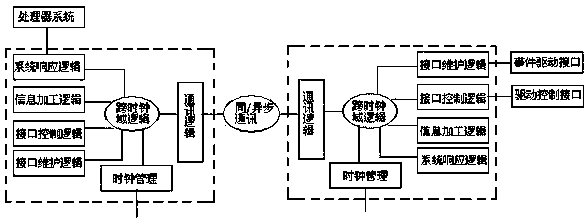

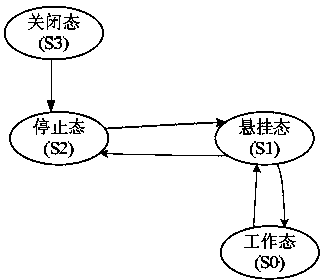

[0033] The invention provides an FPGA zero dynamic power consumption design method, which achieves the effect of zero dynamic power consumption by closing the working clo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More