Method and device for achieving SIMD structure floating point division in general-purpose digital signal processor (GPDSP)

An implementation method and a division technique, which can be applied to calculations using the number system and calculations using non-contact manufacturing equipment, which can solve the problems of increasing the hardware complexity of interrupt processing logic, limited arithmetic precision, and high hardware overhead.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0058] The present invention will be further described below in conjunction with the accompanying drawings and specific preferred embodiments, but the protection scope of the present invention is not limited thereby.

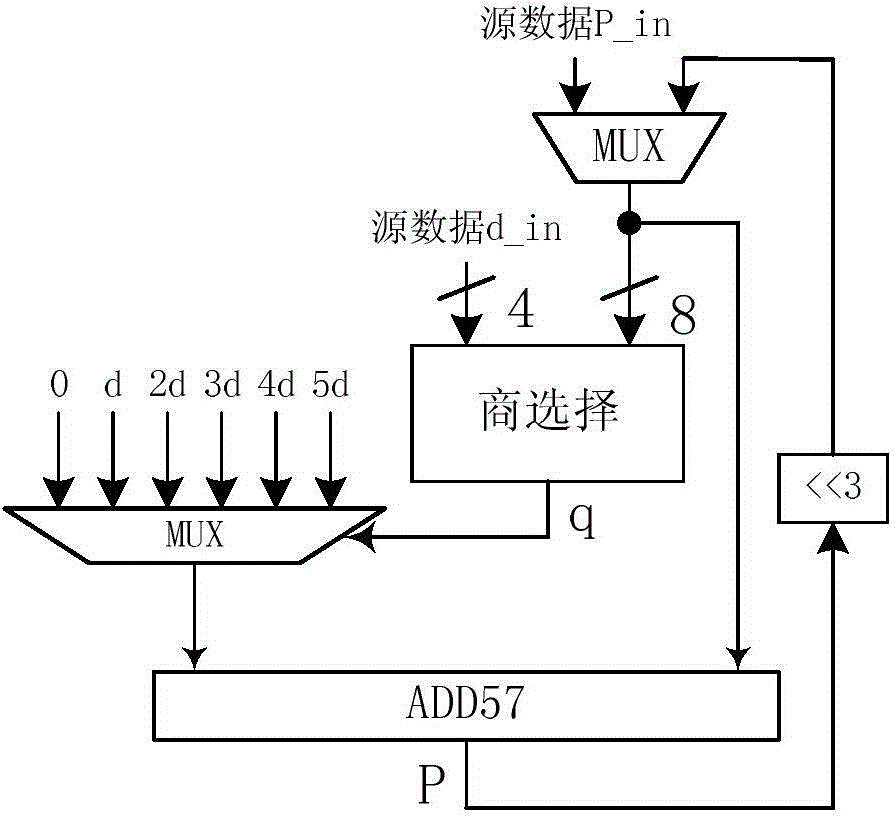

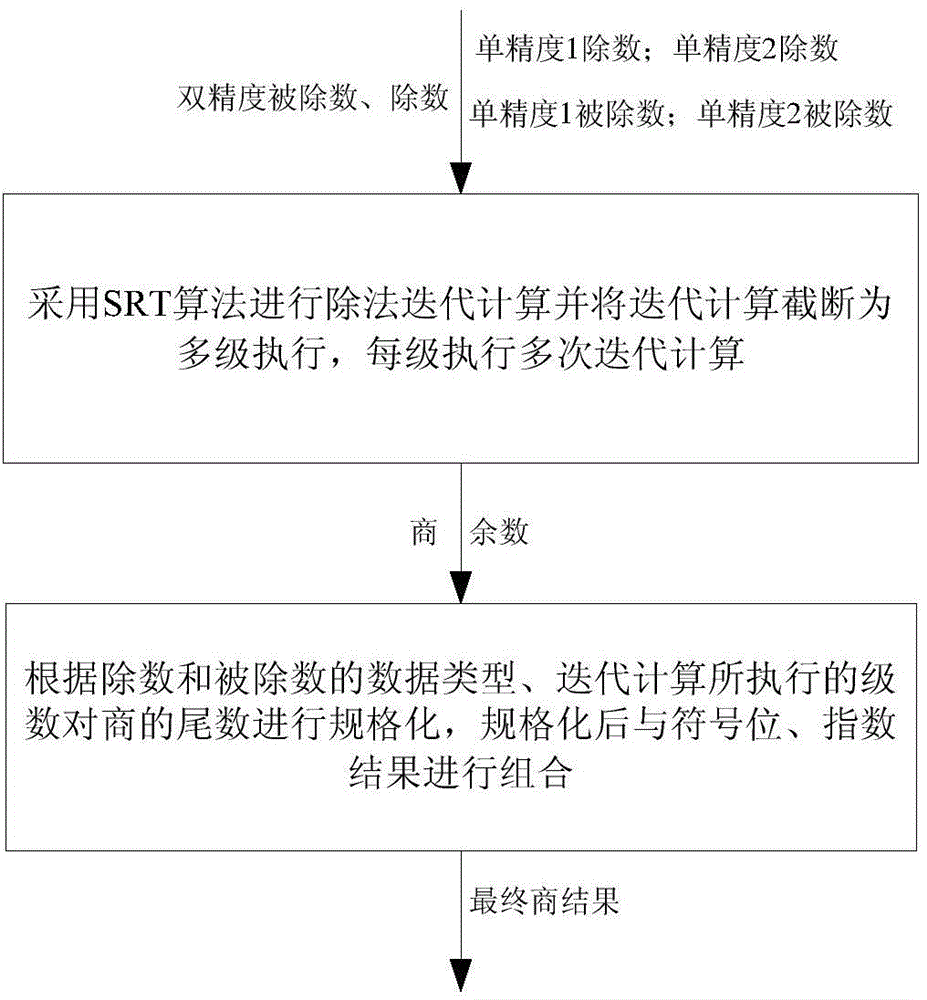

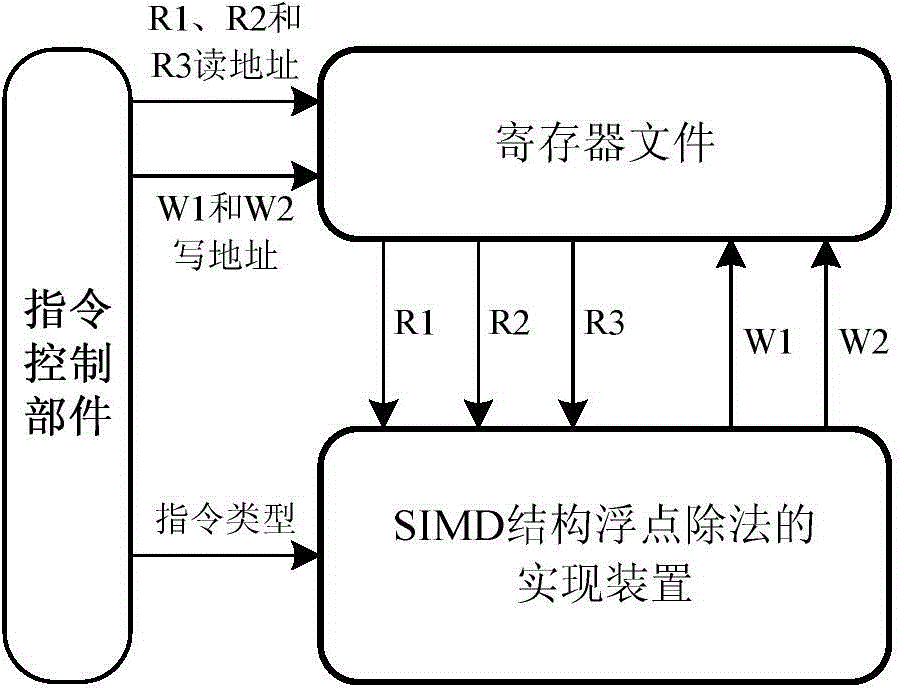

[0059] Such as figure 2 Shown, the realization method of SIMD structure floating-point division in the present embodiment GPDSP, the step is:

[0060] 1) Iterative calculation: Input two double-precision floating-point data as the divisor and dividend respectively, or input two sets of parallel SIMD double-single-precision floating-point data to form two sets of divisor and dividend. Or truncated to multi-level execution, each level performs multiple iterations of the SRT algorithm, and outputs the quotient and remainder obtained after the iterative calculations of all levels are completed, wherein the number of iterations of each level is less than or equal to the maximum instruction cycle of GPDSP;

[0061] 2) Normalization processing: receiving the quotient...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More