Patents

Literature

43 results about "Single-precision floating-point format" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

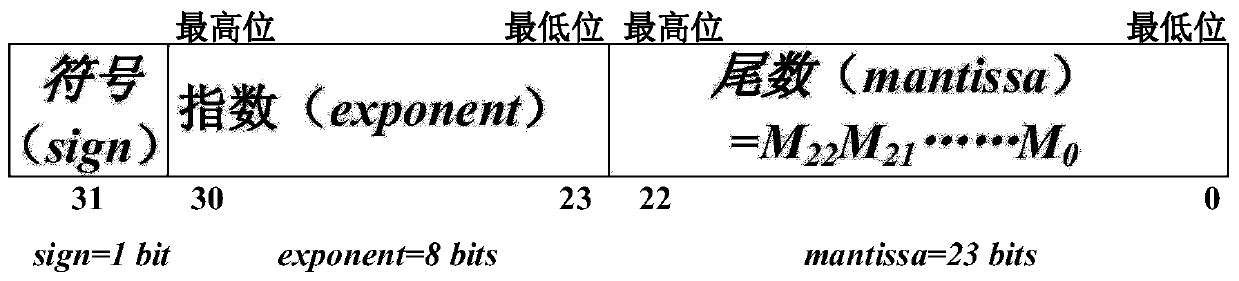

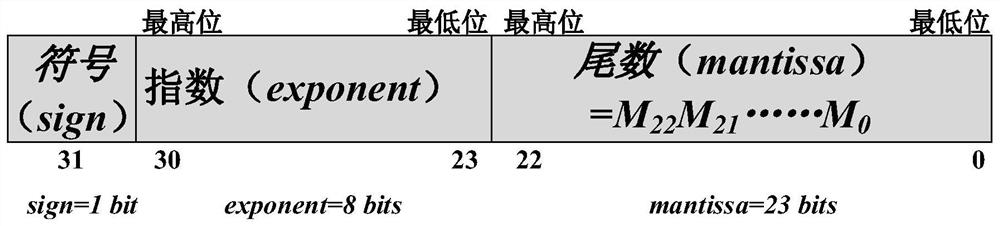

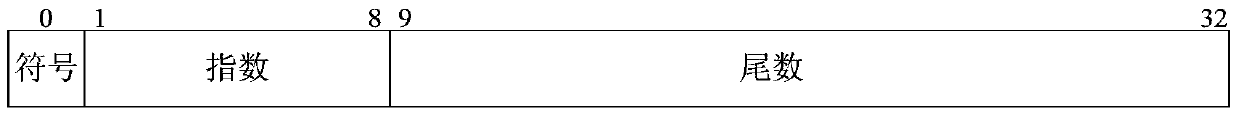

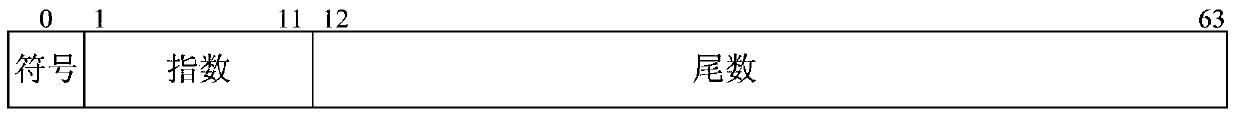

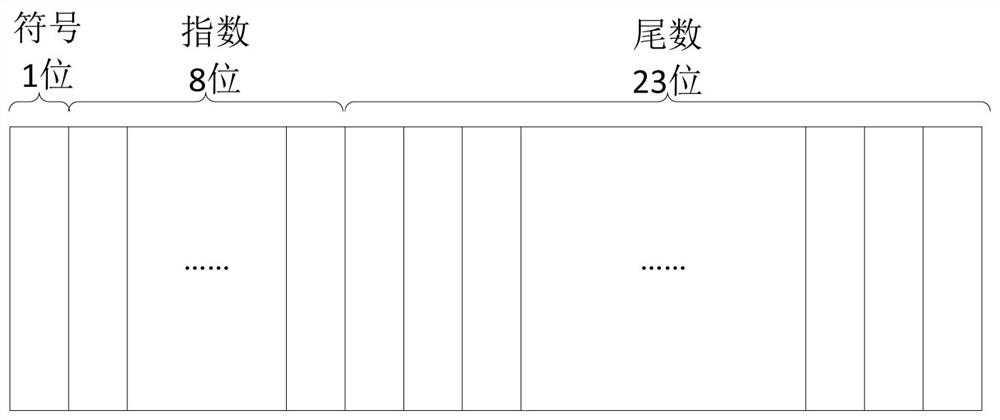

Single-precision floating-point format is a computer number format, usually occupying 32 bits in computer memory; it represents a wide dynamic range of numeric values by using a floating radix point. A floating-point variable can represent a wider range of numbers than a fixed-point variable of the same bit width at the cost of precision. A signed 32-bit integer variable has a maximum value of 2³¹ − 1 = 2,147,483,647, whereas an IEEE 754 32-bit base-2 floating-point variable has a maximum value of (2 − 2⁻²³) × 2¹²⁷ ≈ 3.4028235 × 10³⁸. All integers with 7 or fewer decimal digits, and any 2 for a whole number −149 ≤ n ≤ 127, can be converted exactly into an IEEE 754 single-precision floating-point value.

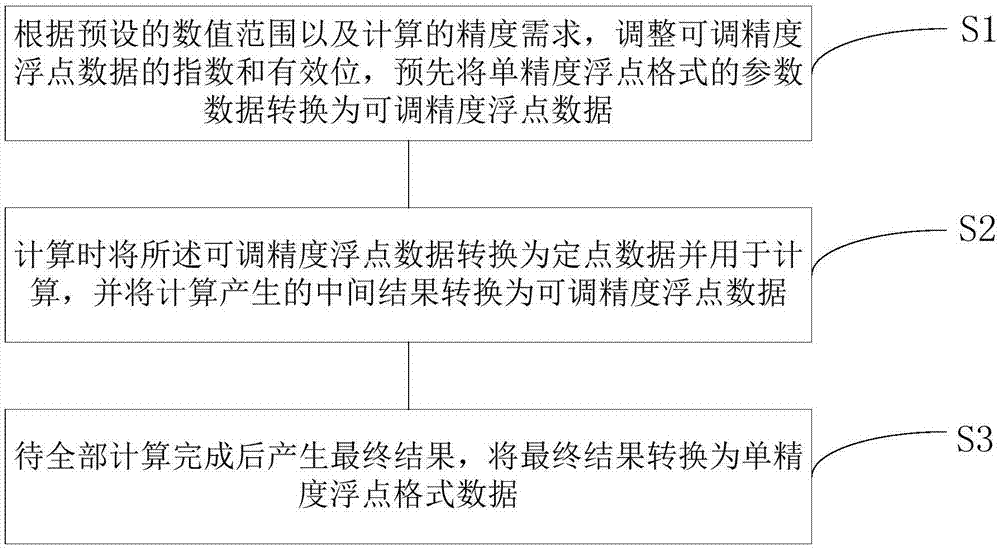

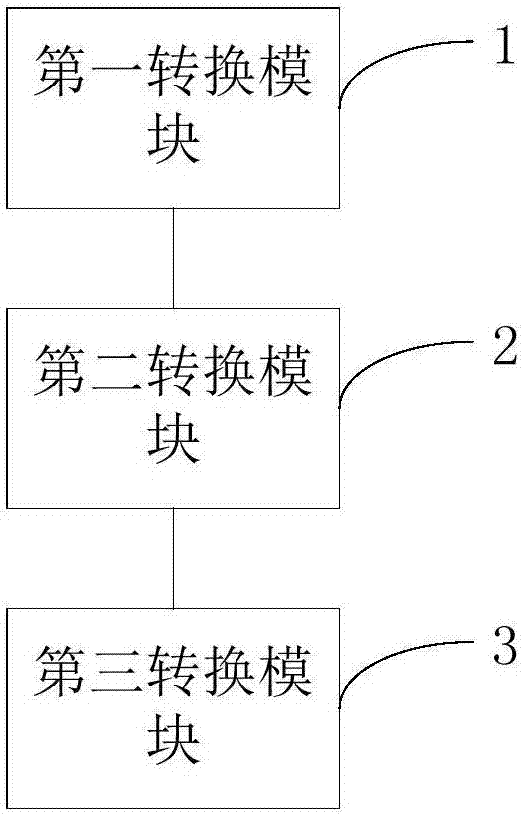

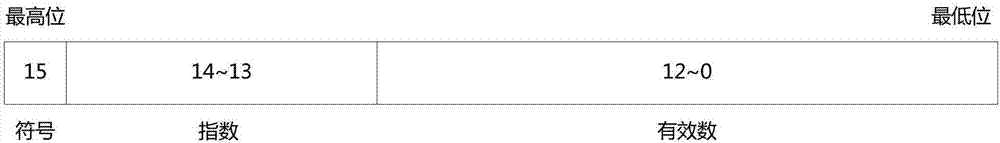

Fixed-point method and system for floating-point operation

ActiveCN107451658AReduce precision lossImprove efficiencyPhysical realisationNeural learning methodsNumerical rangeParallel computing

The invention discloses a fixed-point method for a floating-point operation. The method comprises the steps that according to a preset numerical range and the calculation precision requirement, the exponents and significant bits of adjustable-precision floating-point data are adjusted, and the parameter data in a single-precision floating-point format are converted into adjustable-precision floating-point data; when calculating is carried out, the adjustable-precision floating-point data are converted into fixed-point data and used for calculation, and an intermediate result generated by calculation is converted into adjustable-precision floating-point data; a final result is generated after all calculation; and the final result is converted to data in the single-precision floating-point format. According to the invention, standard floating-point data can be represented with a 16-bit bit width or a smaller bit width to realize fixed-point conversion of the floating-point operation; the storage space is saved; the operation performance is improved; and the calculation precision is not influenced.

Owner:HANGZHOU FEISHU TECH CO LTD

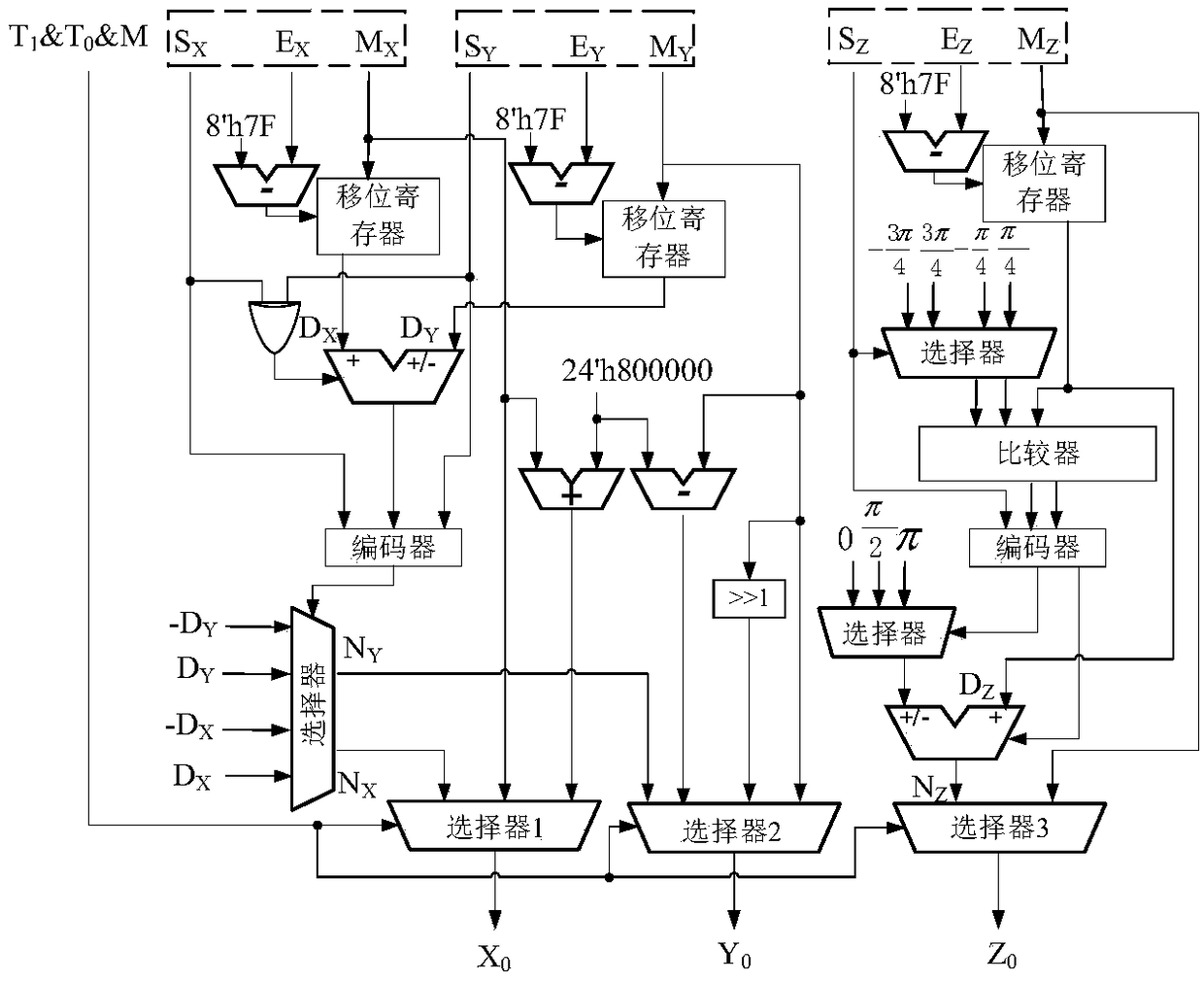

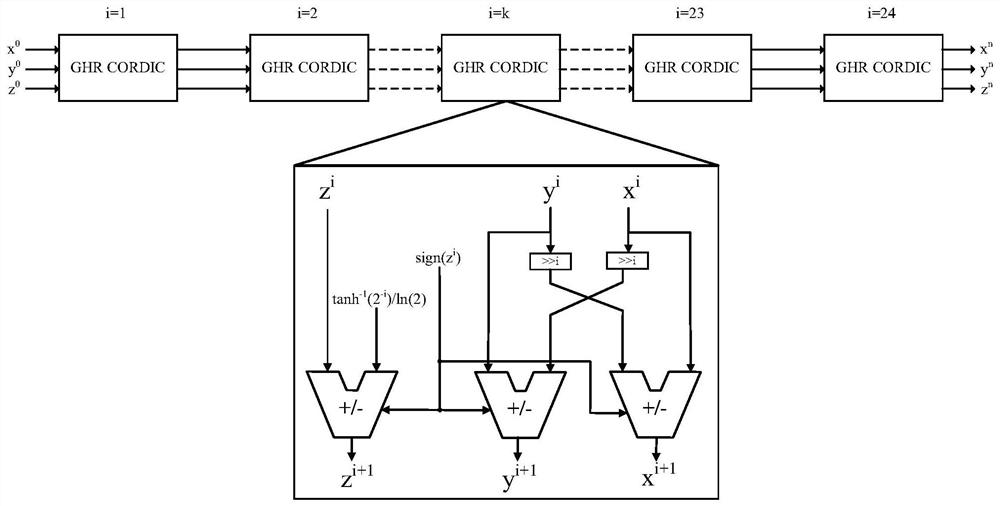

Reconfigurable floating-point operation device based on CORDIC algorithm

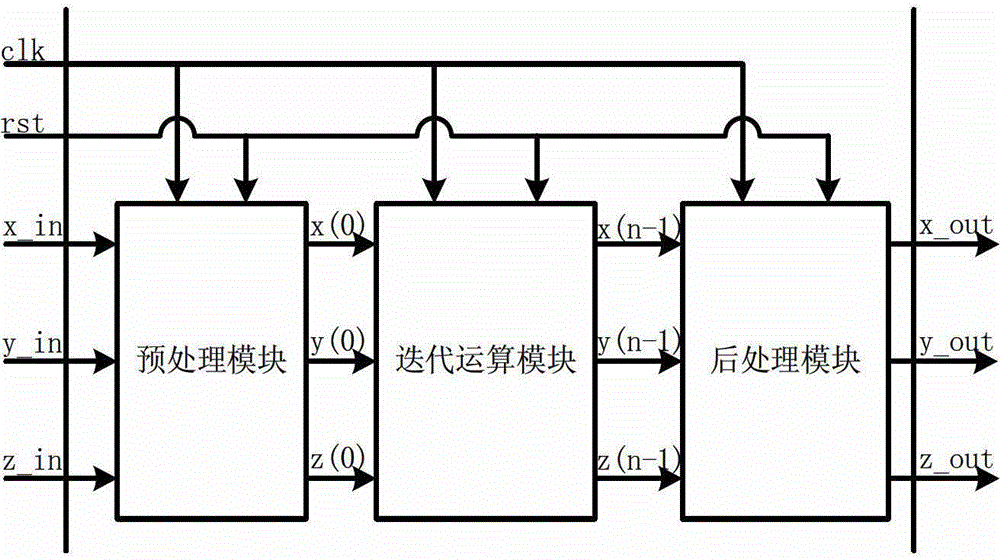

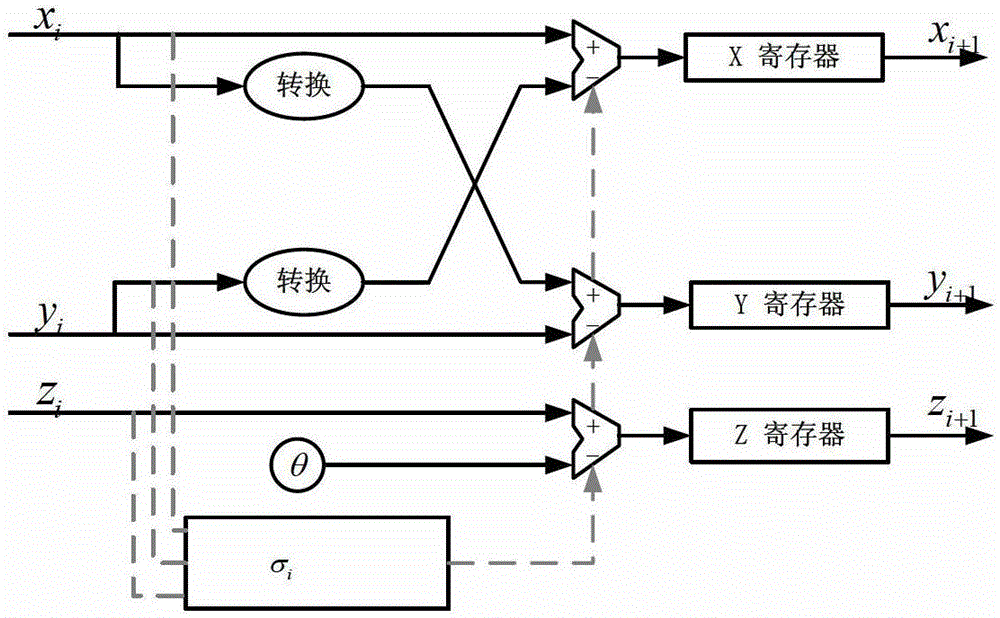

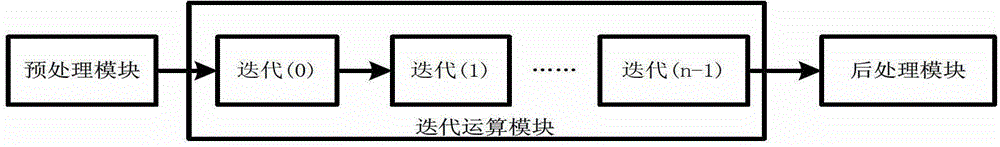

ActiveCN109062540AExtended region of convergenceReduce clock cyclesDigital data processing detailsReconfigurable antennaComputer module

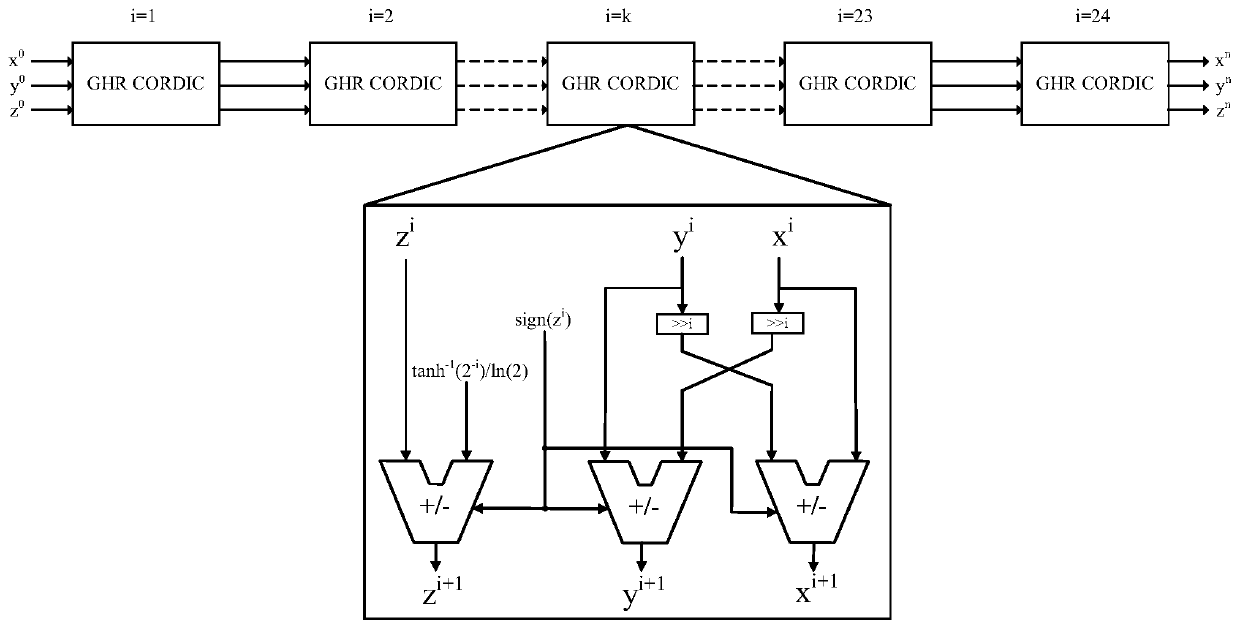

A reconfigurable floating-point arithmetic device based on CORDIC algorithm comprises a preprocessing module for completing input data from IEEE-754 standard, and maps it into the convergence region;a series-parallel hybrid reconfigurable CORDIC iterative unit module. The iterative operation part of CORDIC algorithm is composed of two parts: rotation modules A and B, wherein, the rotation moduleA is used to realize serial pipeline structure to maximize module reuse, the rotation module B is based on parallel prediction method of rotation direction and adopts tree adder structure to realize parallel structure in rotation mode; in the post-processing module, the corresponding result output is selected according to the encoded signal of the pre-processing module, and the mantissa normalization processing is completed to output the single-precision floating-point data format calculation result. The invention has the characteristics of simple principle, low delay, high precision and low hardware cost.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

Implementation method of single-precision floating point trigonometric function covering full circumferential angle

InactiveCN103150137ASave logic resourcesIncrease working frequencyDigital data processing detailsDigital signal processingOriginal data

The invention discloses an implementation method of single-precision floating point trigonometric function covering full circumferential angle, and belongs to the field of processing of digital signal. The method comprises following steps: firstly, a preprocessing module CORDIC-PRE receives input single-precision floating point data, records the quadrant information of original data, converts the single-precision floating point data within a set angle range into high-precision floating point data, and inputs the high-precision floating point data to an iterative operation module CORDIC-CORE; secondly, the CORDIC-CORE finishes iterative operation of the CORDIC algorithm to the input data by adopting high-precision floating point operation; the result is input to a postprocessing module CORDIC-POST; thirdly, the CORDIC-POST performs quadrant recovery to sine and cosine functional values to be required to be calculated as per the quadrant information recorded in the CORDIC-PRE aiming to the input data; and the data after being recovered is converted into the precision floating point data and output. The implementation method is suitable for actual operation of CORDIC algorithm.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

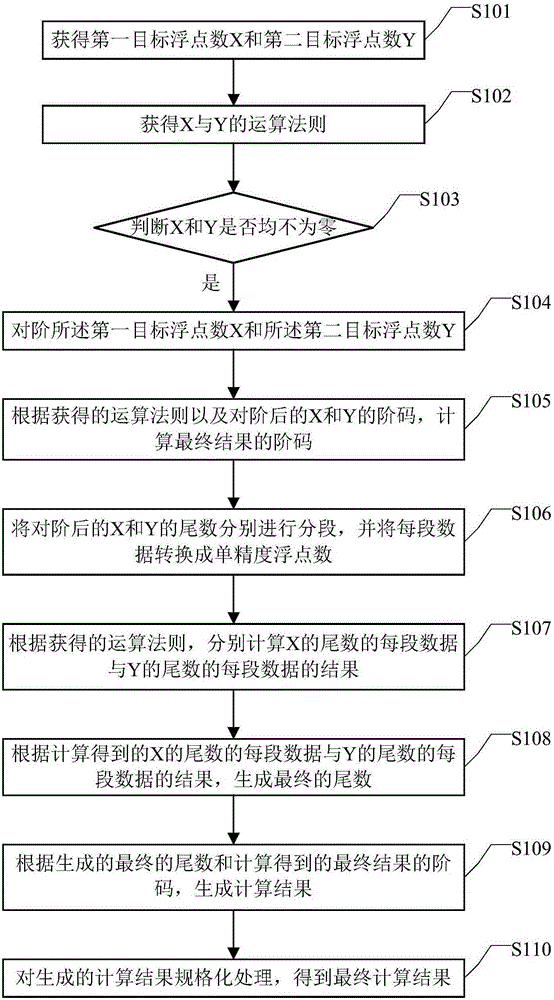

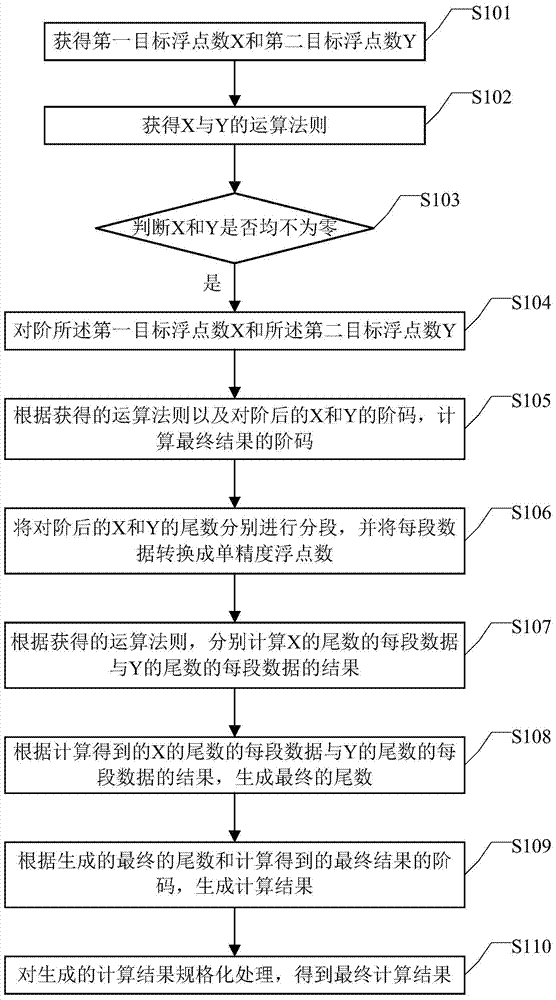

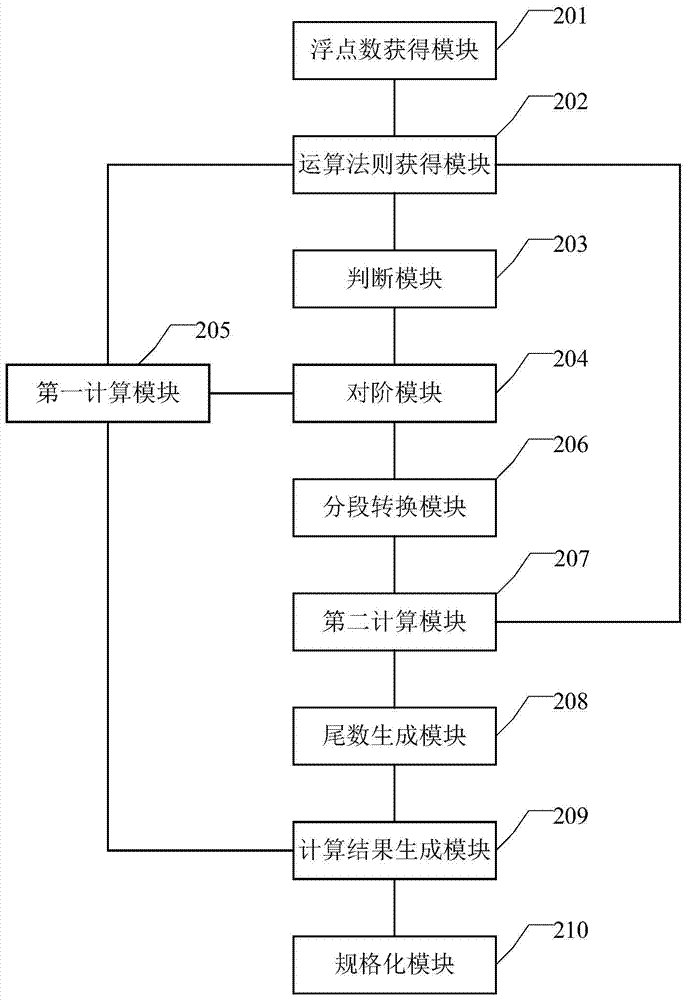

Method and device for processing floating-point number

ActiveCN105224284AImprove computing powerDigital data processing detailsParallel computingSingle-precision floating-point format

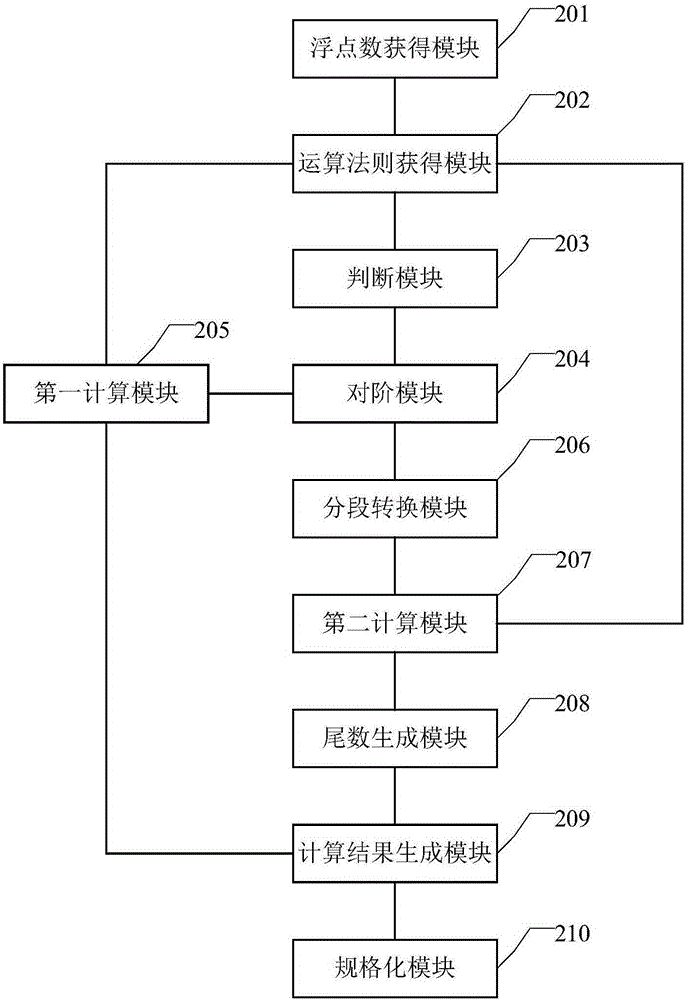

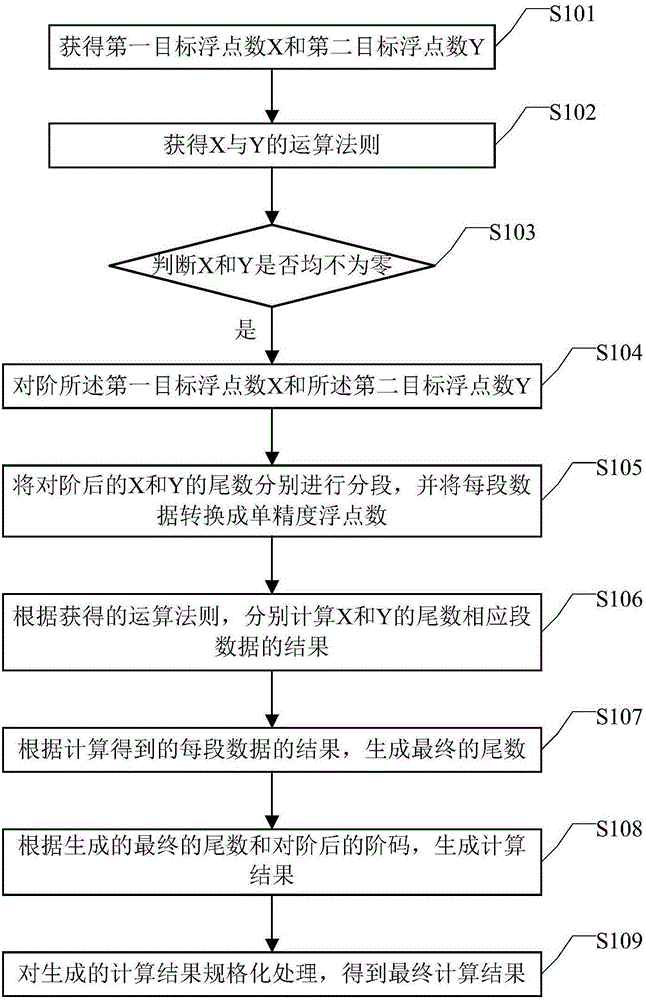

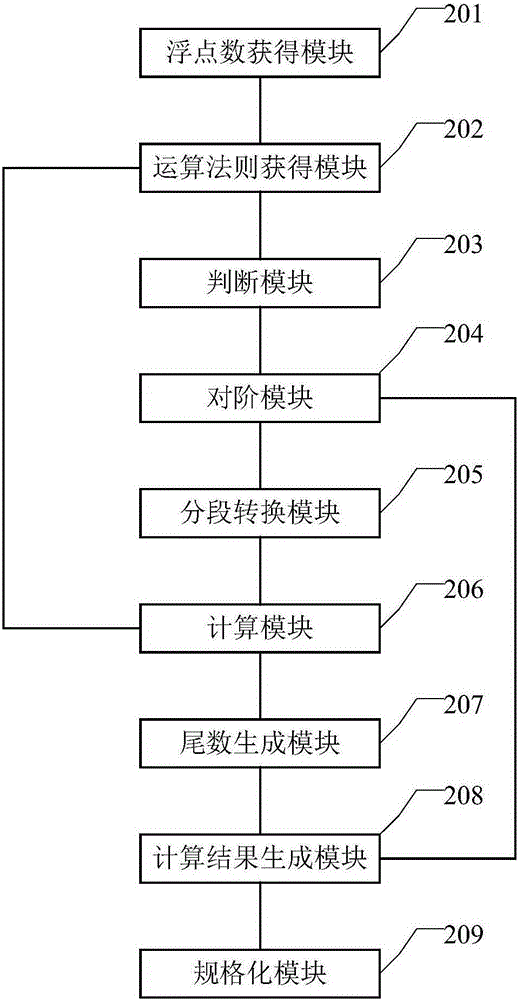

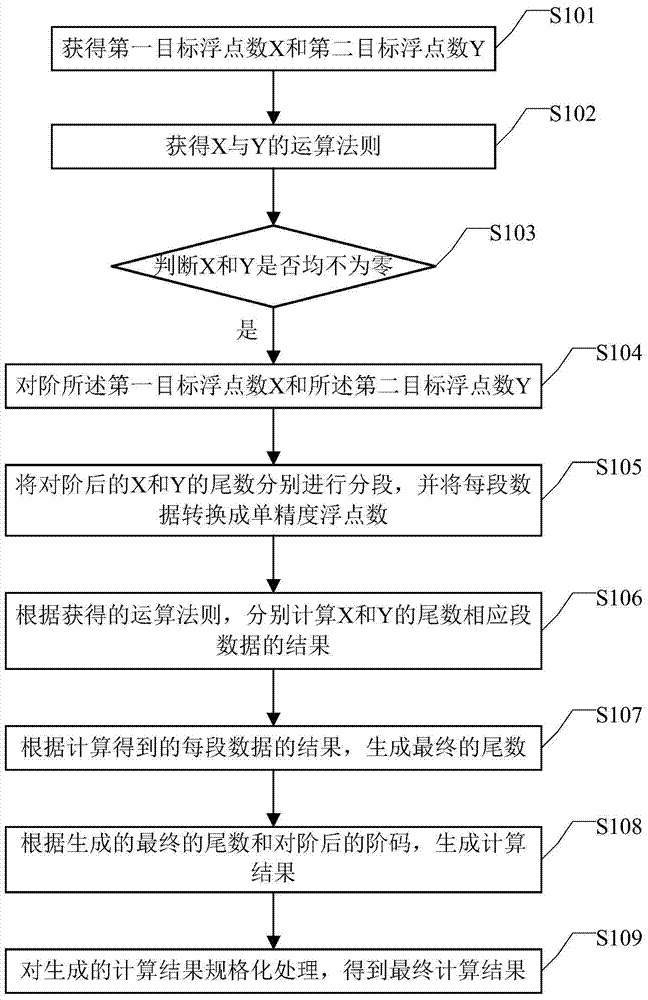

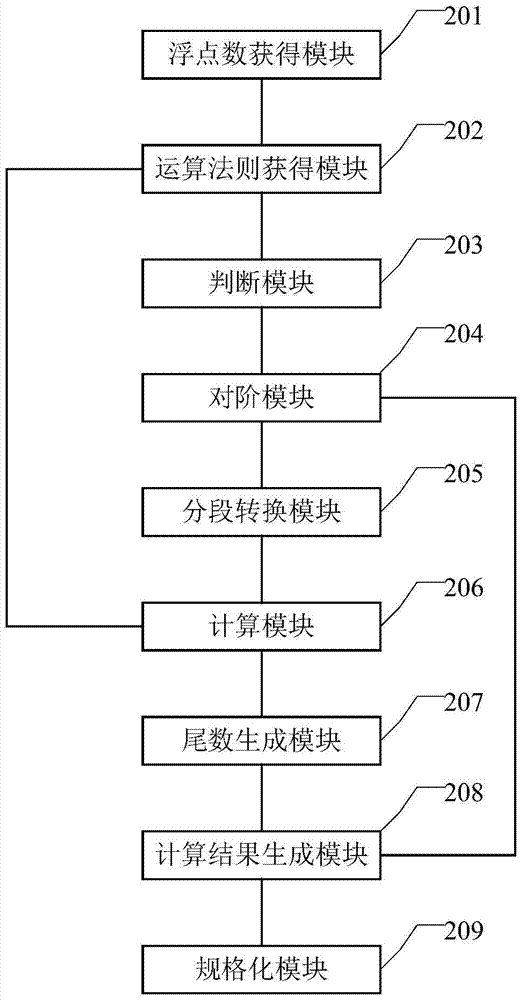

Embodiments of the invention disclose a method and a device for processing floating-point numbers. The method comprises: obtaining a first target floating-point number X and a second target floating-point number Y; obtaining an operation rule of the X and the Y; under the condition that the X and the Y are not zero, performing exponent matching on the X and the Y; calculating the exponent of a final result; respectively segmenting the mantissas of the X and the Y whose exponents are matched, and respectively calculating results of each segment data of the mantissa of the X and each segment data of the mantissa of the Y; according to calculation result, generating a final mantissa; according to the final mantissa and the exponent obtained by calculation, generating a calculation result; and performing normalizing processing on the calculation result, to obtain a final calculation result. Using the method, the mantissa of a floating-point number with high precision is segmented, and each segment of mantissa is converted to the floating-point number with single precision to calculate, so that lower-end CPU products which do not have double-precision floating-point number computing power have high-precision floating-point number computing power, and computing power of the lower-end CPU products on the high-precision floating-point number is improved.

Owner:BEIJING QIYI CENTURY SCI & TECH CO LTD

Single-precision floating-point data storing method and processor

InactiveCN101539850AAvoid complex processLess quantityProgram control using stored programsDigital data processing detailsProcessor registerParallel computing

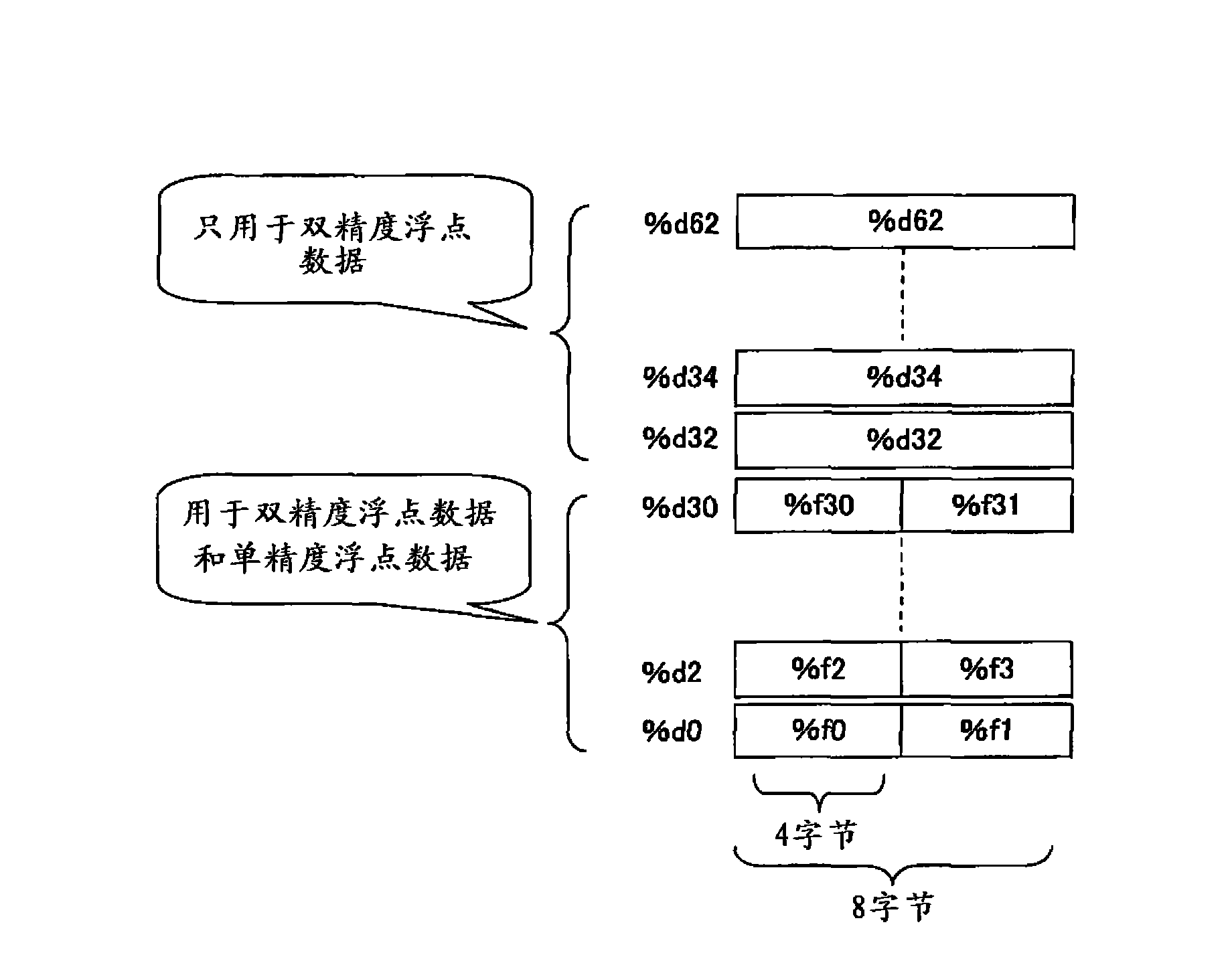

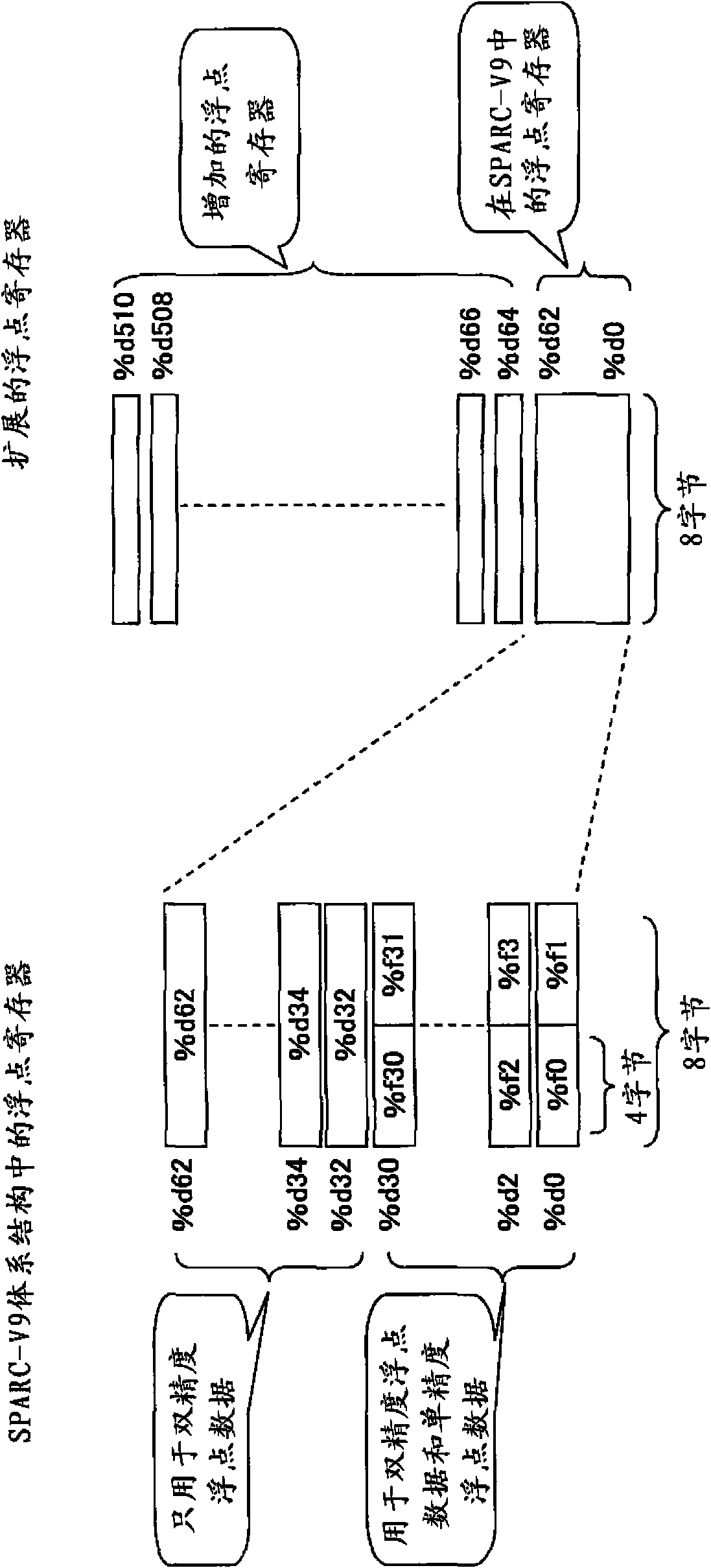

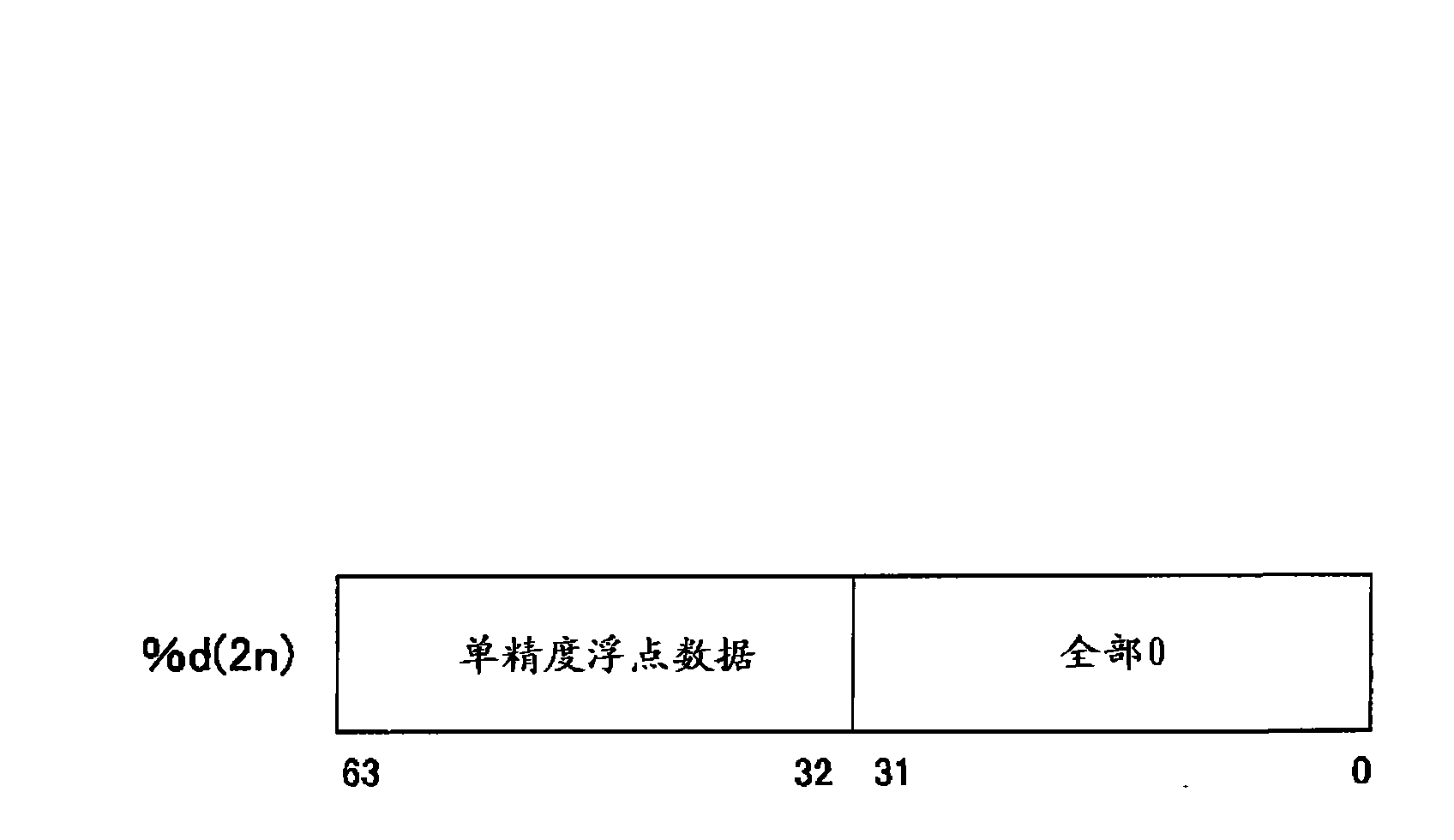

A single-precision floating-point data storing method for use in a processor including a register, which has a size that can store double-precision floating-point data, for storing double-precision floating-point data and single-precision floating-point data comprises writing input single-precision floating-point data to the high-order half of the register, and writing all zeros to the low-order half of the register if a single-precision floating-point data process is specified.

Owner:FUJITSU LTD

Method and device for processing floating-point number

ActiveCN105224283AImprove computing powerDigital data processing detailsComputer scienceSingle-precision floating-point format

Embodiments of the invention disclose a method and a device for processing floating-point numbers. The method comprises: obtaining a first target floating-point number X and a second target floating-point number Y; obtaining an operation rule of the X and the Y; determining whether the X and the Y are not zero; if the X and the Y are not zero, and exponents of the X and the Y are not equal, matching exponents of the X and the Y; respectively segmenting the mantissas of the X and the Y whose exponents are matched, converting each segment of data to a floating-point number with single precision; respectively calculating results of mantissa corresponding segment data, according to result of each segment of data obtained by calculation, generating final mantissas; and generating a calculation result; and performing normalizing processing on the calculation result. Using the method, the mantissa of a floating-point number with high precision is segmented, and each segment of mantissa is converted to the floating-point number with single precision to calculate, so that lower-end CPU products which do not have double-precision floating-point number computing power have high-precision floating-point number computing power, and computing power of the lower-end CPU products on the high-precision floating-point number is improved.

Owner:BEIJING QIYI CENTURY SCI & TECH CO LTD

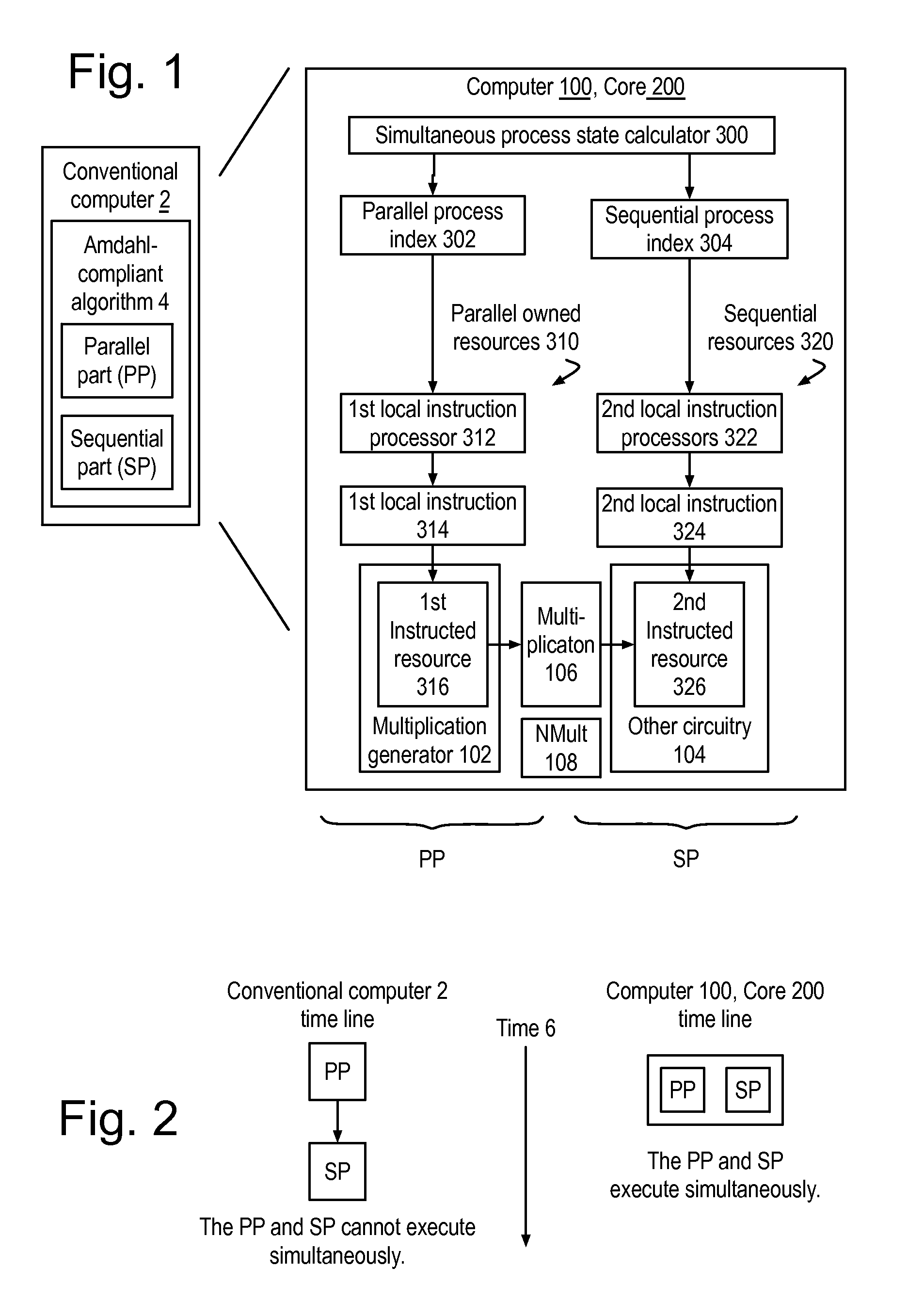

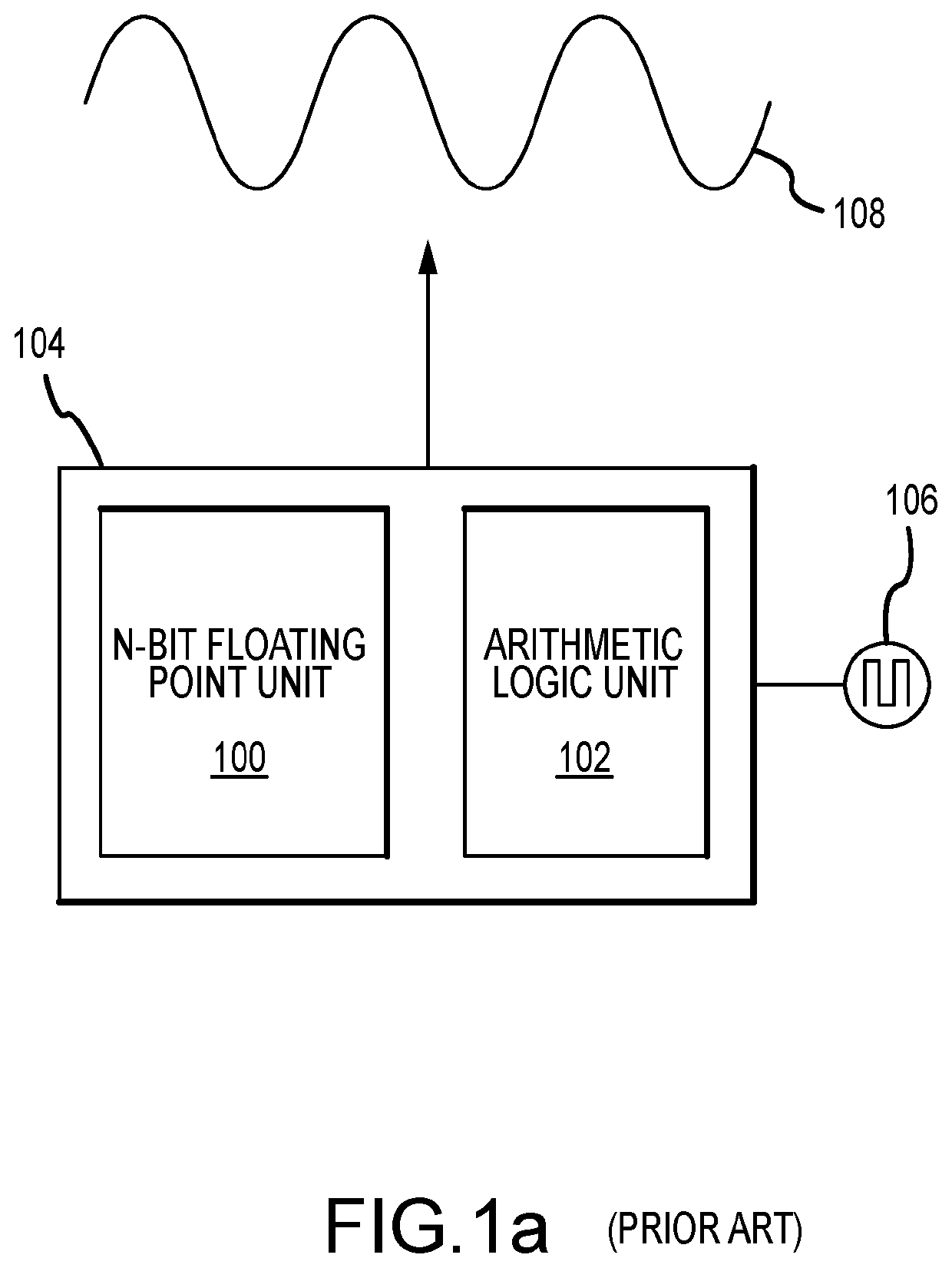

Computer for Amdahl-compliant algorithms like matrix inversion

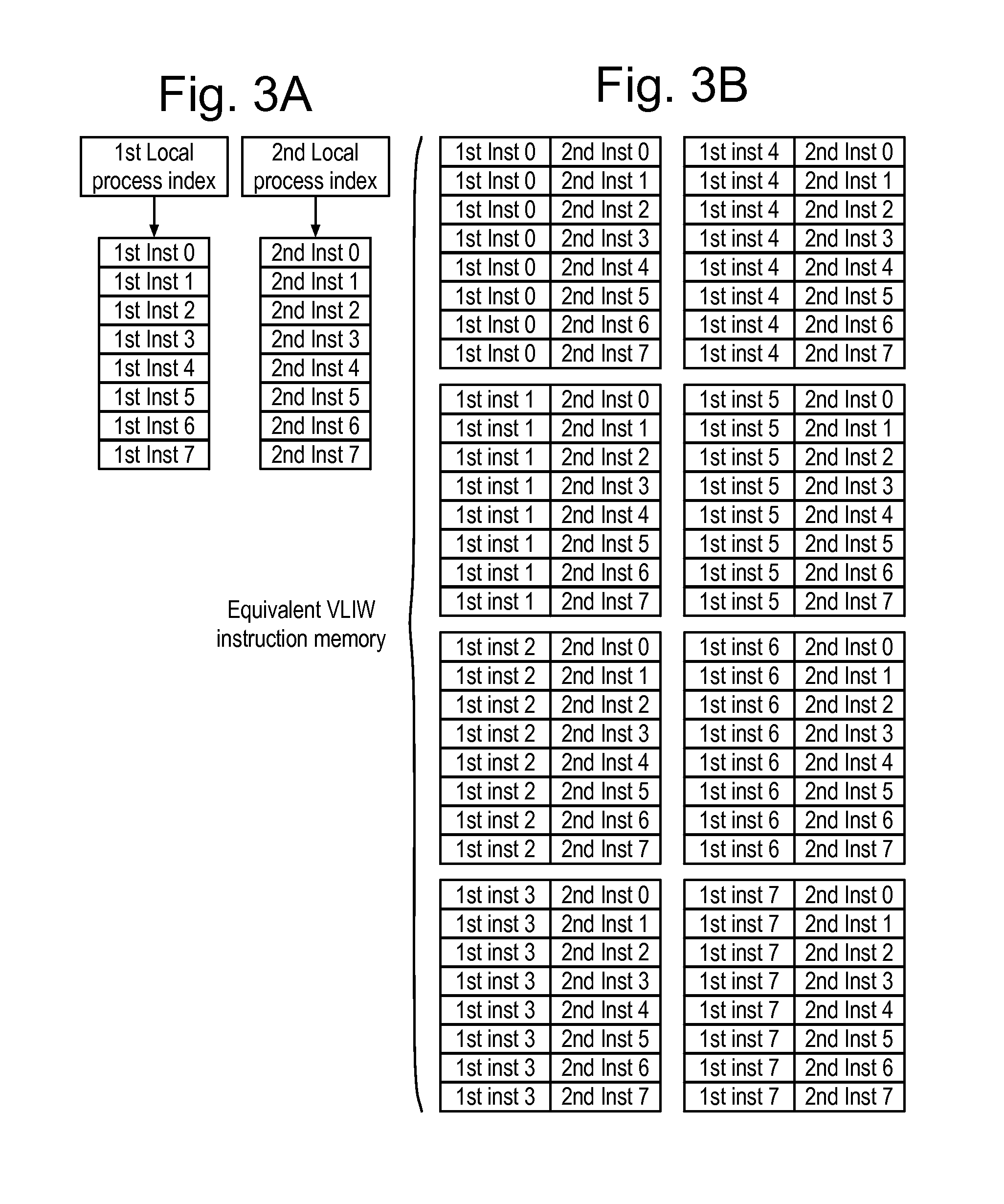

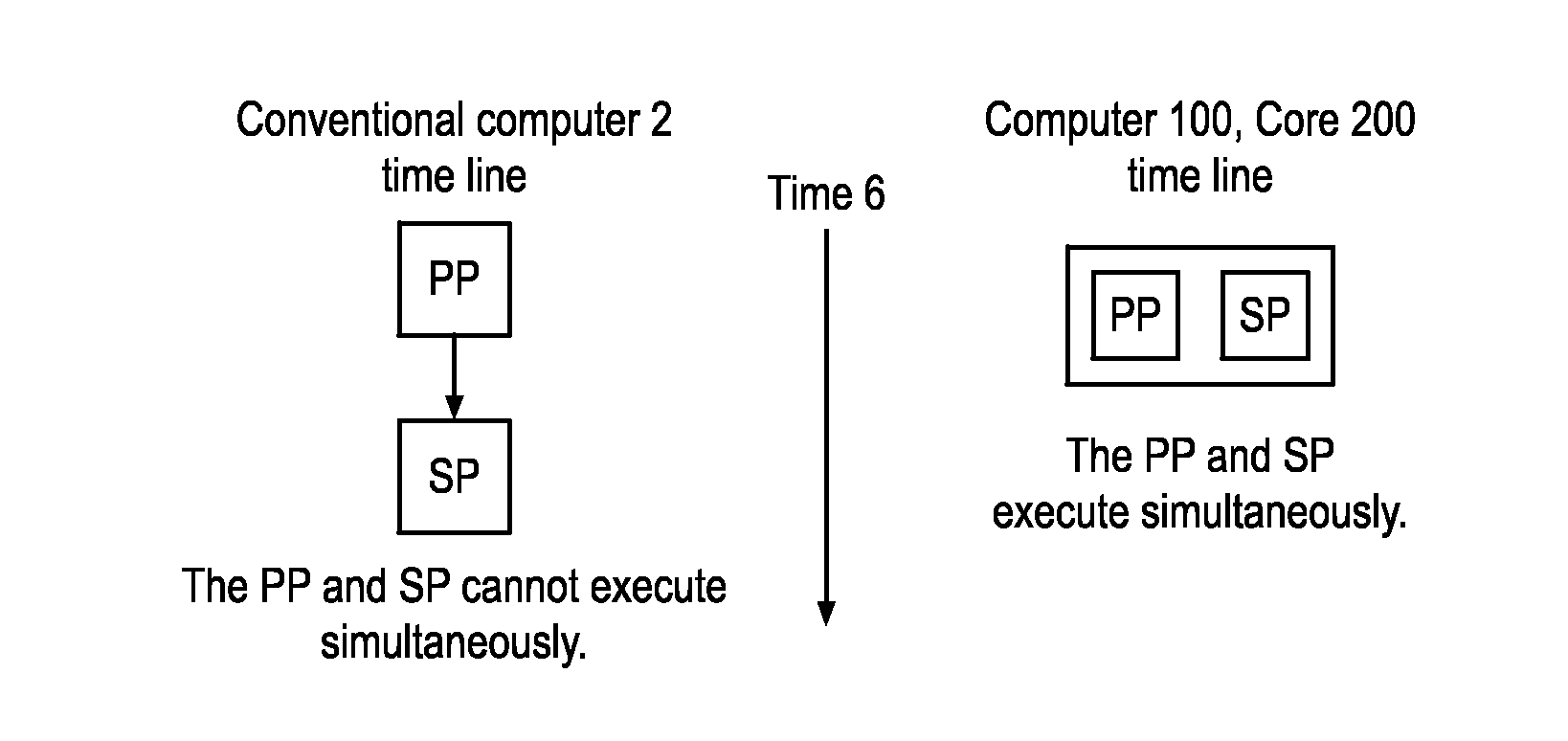

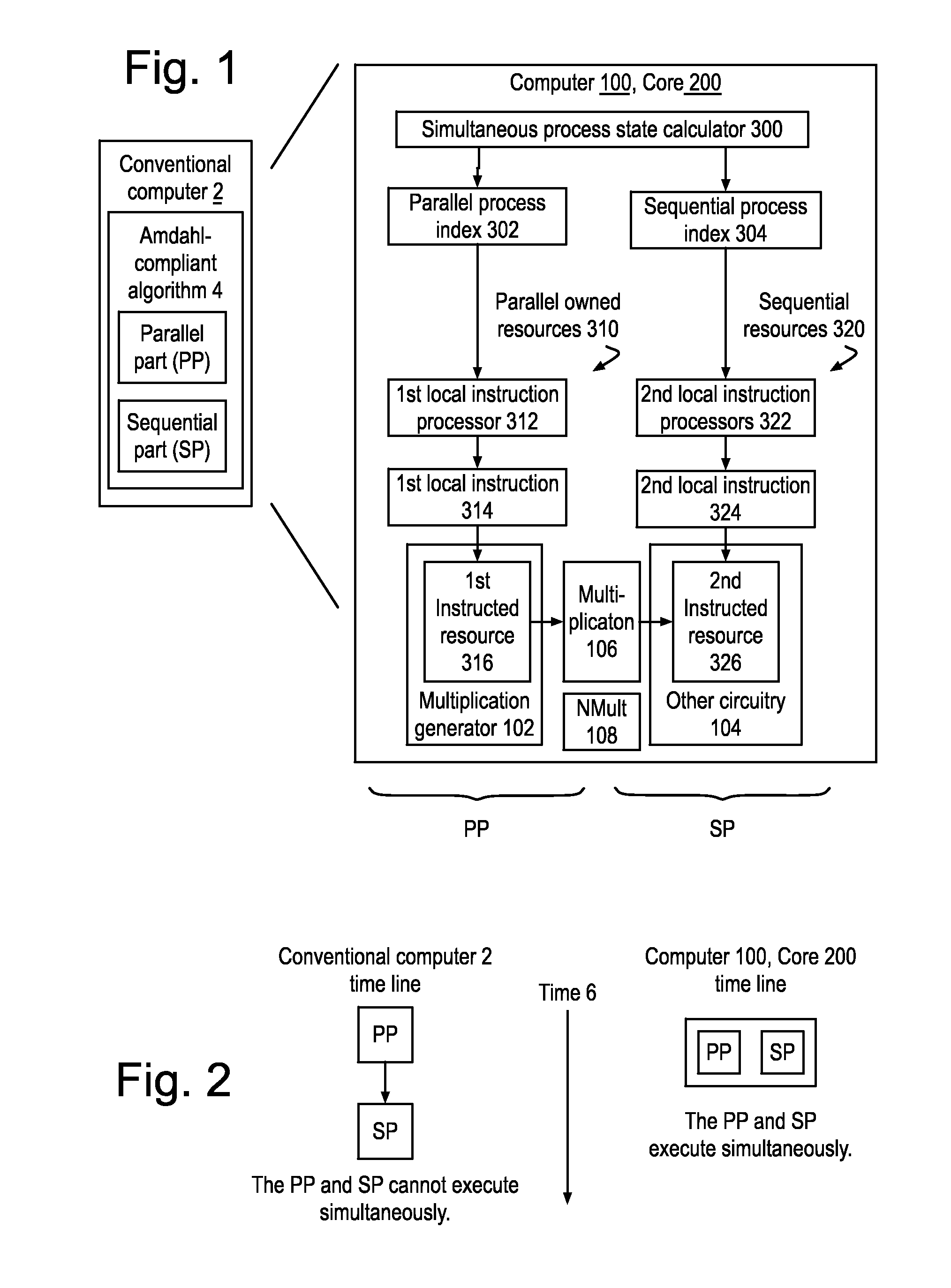

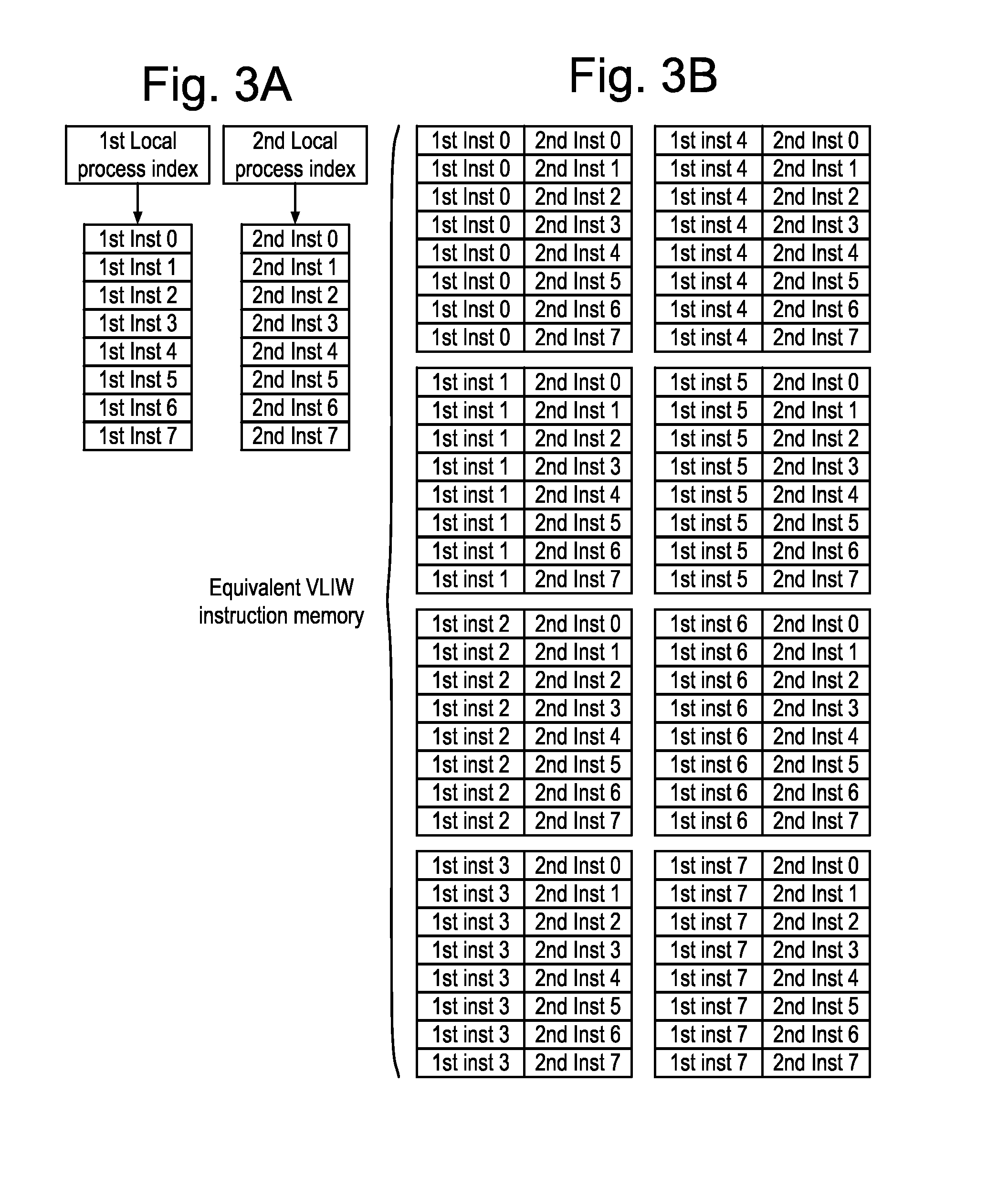

ActiveUS8892620B2More complexMaximum performanceComputation using non-contact making devicesDigital computer detailsSingle-coreSingle-precision floating-point format

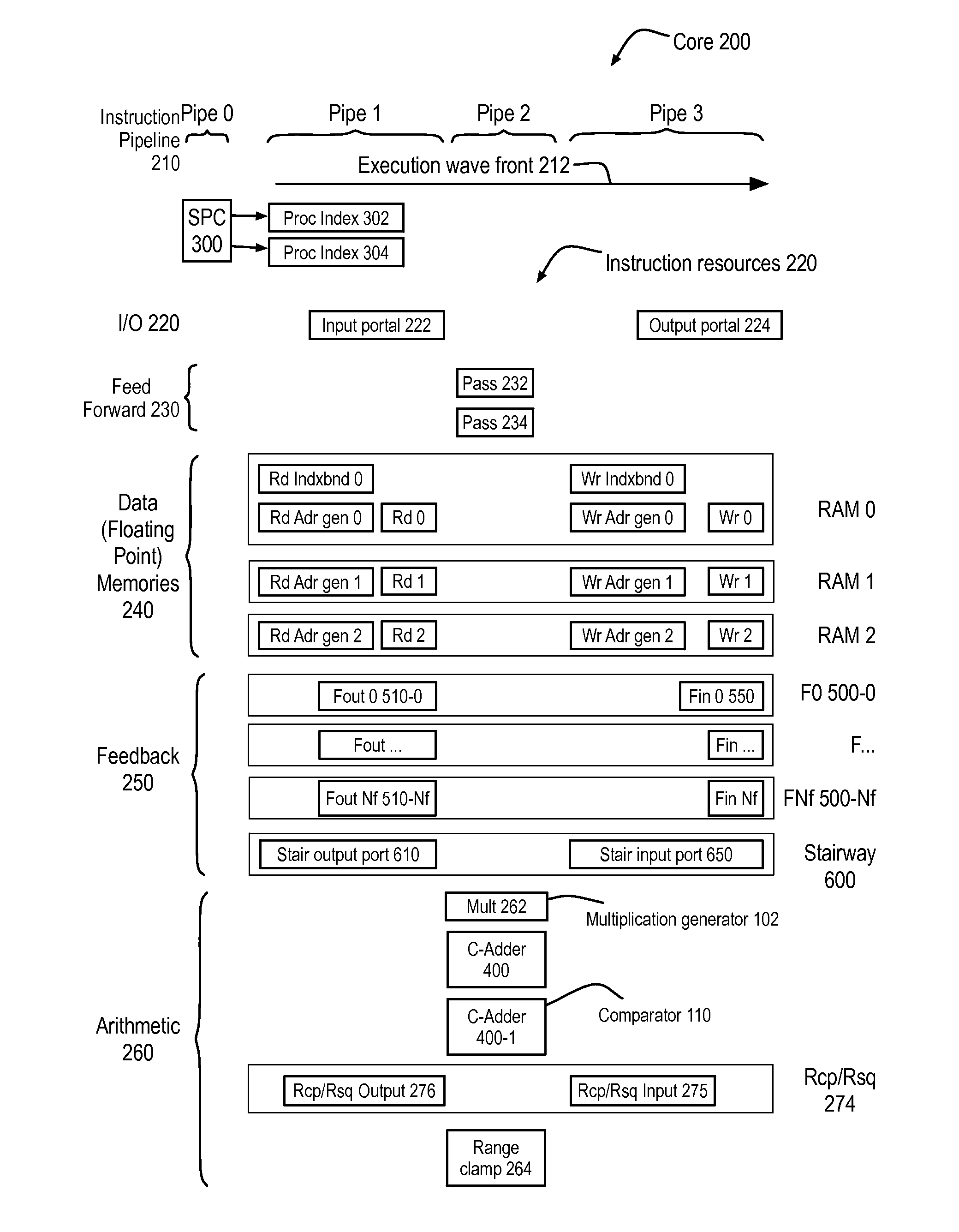

A family of computers is disclosed and claimed that supports simultaneous processes from the single core up to multi-chip Program Execution Systems (PES). The instruction processing of the instructed resources is local, dispensing with the need for large VLIW memories. The cores through the PES have maximum performance for Amdahl-compliant algorithms like matrix inversion, because the multiplications do not stall and the other circuitry keeps up. Cores with log based multiplication generators improve this performance by a factor of two for sine and cosine calculations in single precision floating point and have even greater performance for loge and ex calculations. Apparatus specifying, simulating, and / or layouts of the computer (components) are disclosed. Apparatus the computer and / or its components are disclosed.

Owner:QSIGMA

Computer for amdahl-compliant algorithms like matrix inversion

ActiveUS20150039866A1More complexMaximum performanceDigital computer detailsSpecific program execution arrangementsSingle-coreSingle-precision floating-point format

A family of computers is disclosed and claimed that supports simultaneous processes from the single core up to multi-chip Program Execution Systems (PES). The instruction processing of the instructed resources is local, dispensing with the need for large VLIW memories. The cores through the PES have maximum performance for Amdahl-compliant algorithms like matrix inversion, because the multiplications do not stall and the other circuitry keeps up. Cores with log based multiplication generators improve this performance by a factor of two for sine and cosine calculations in single precision floating point and have even greater performance for loge and ex calculations. Apparatus specifying, simulating, and / or layouts of the computer (components) are disclosed. Apparatus the computer and / or its components are disclosed.

Owner:QSIGMA

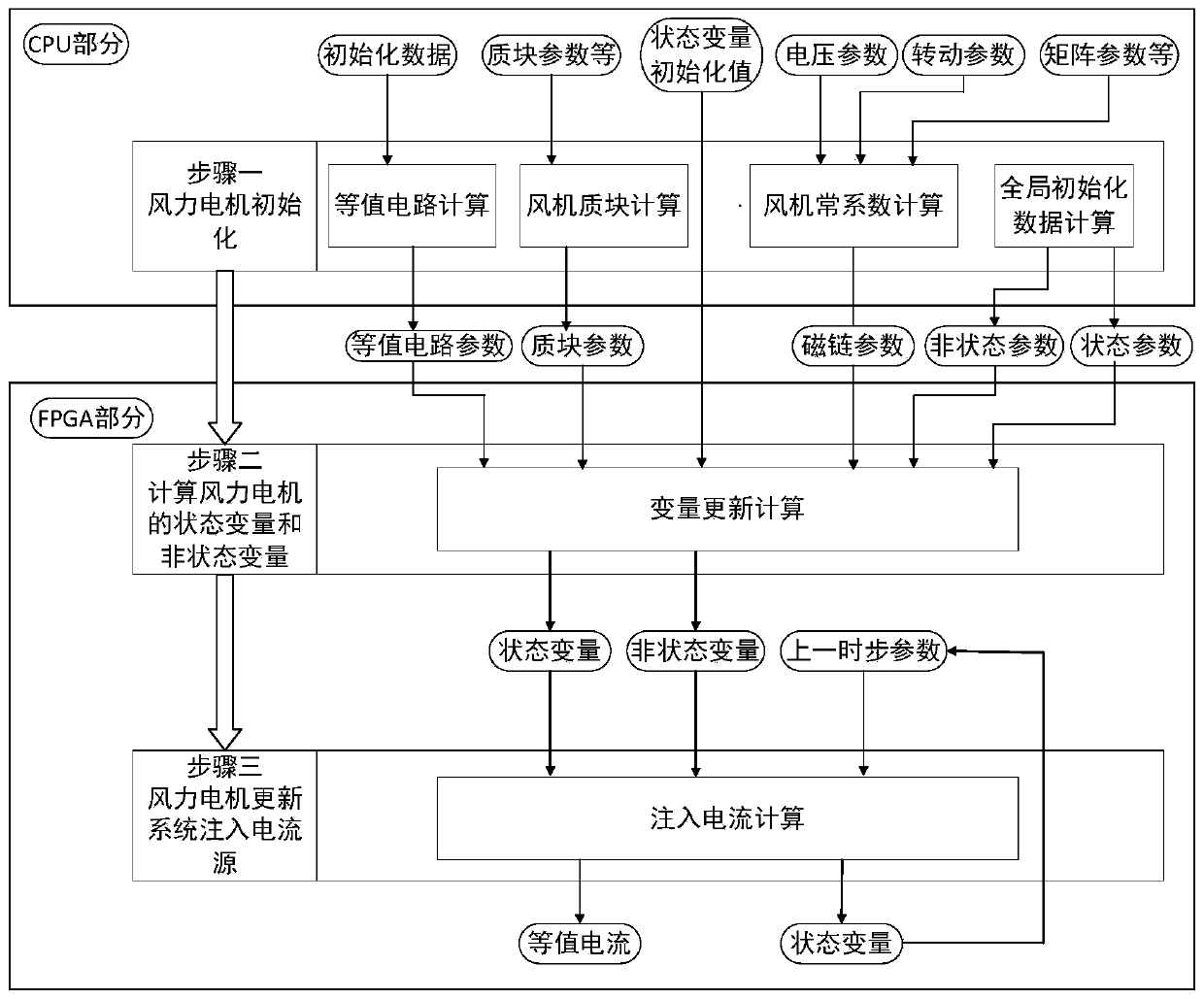

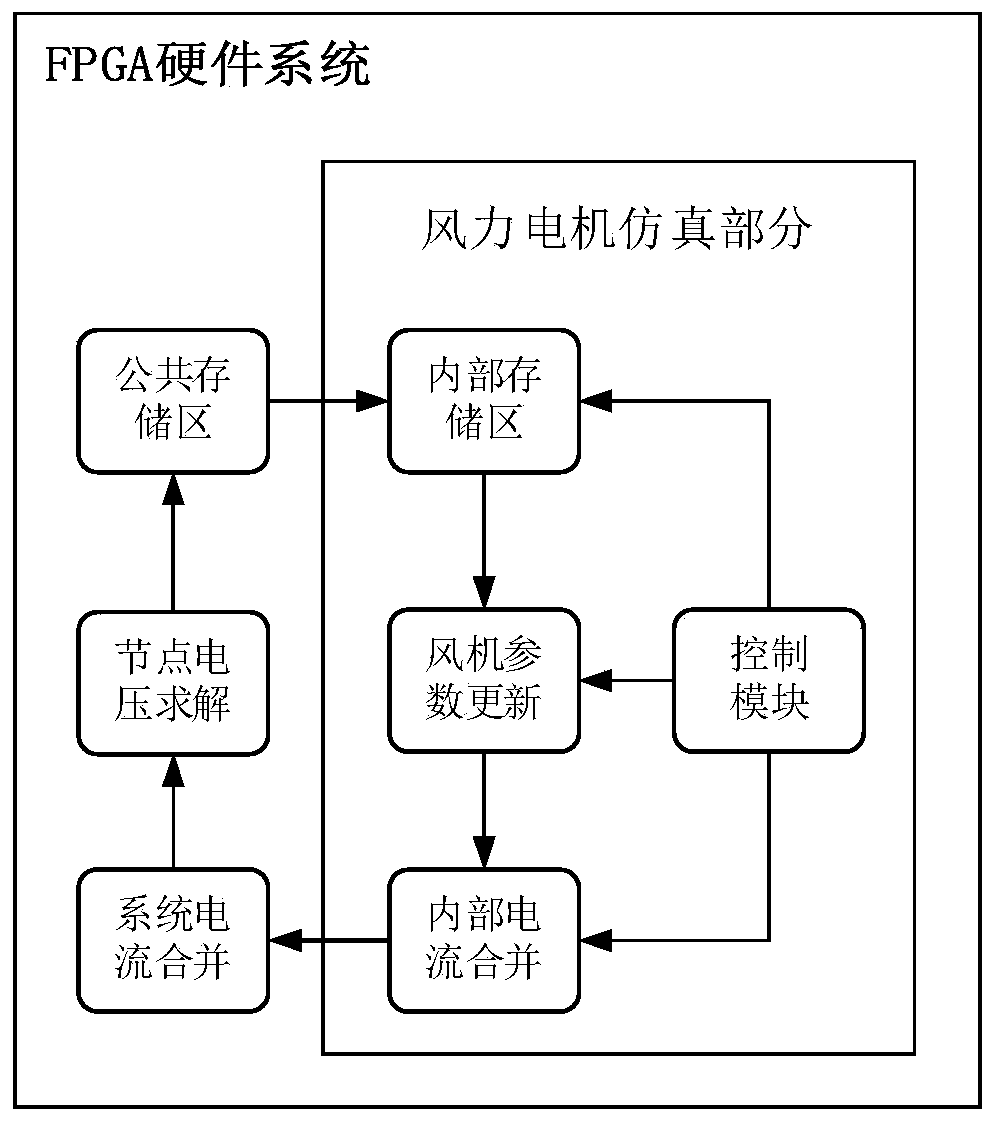

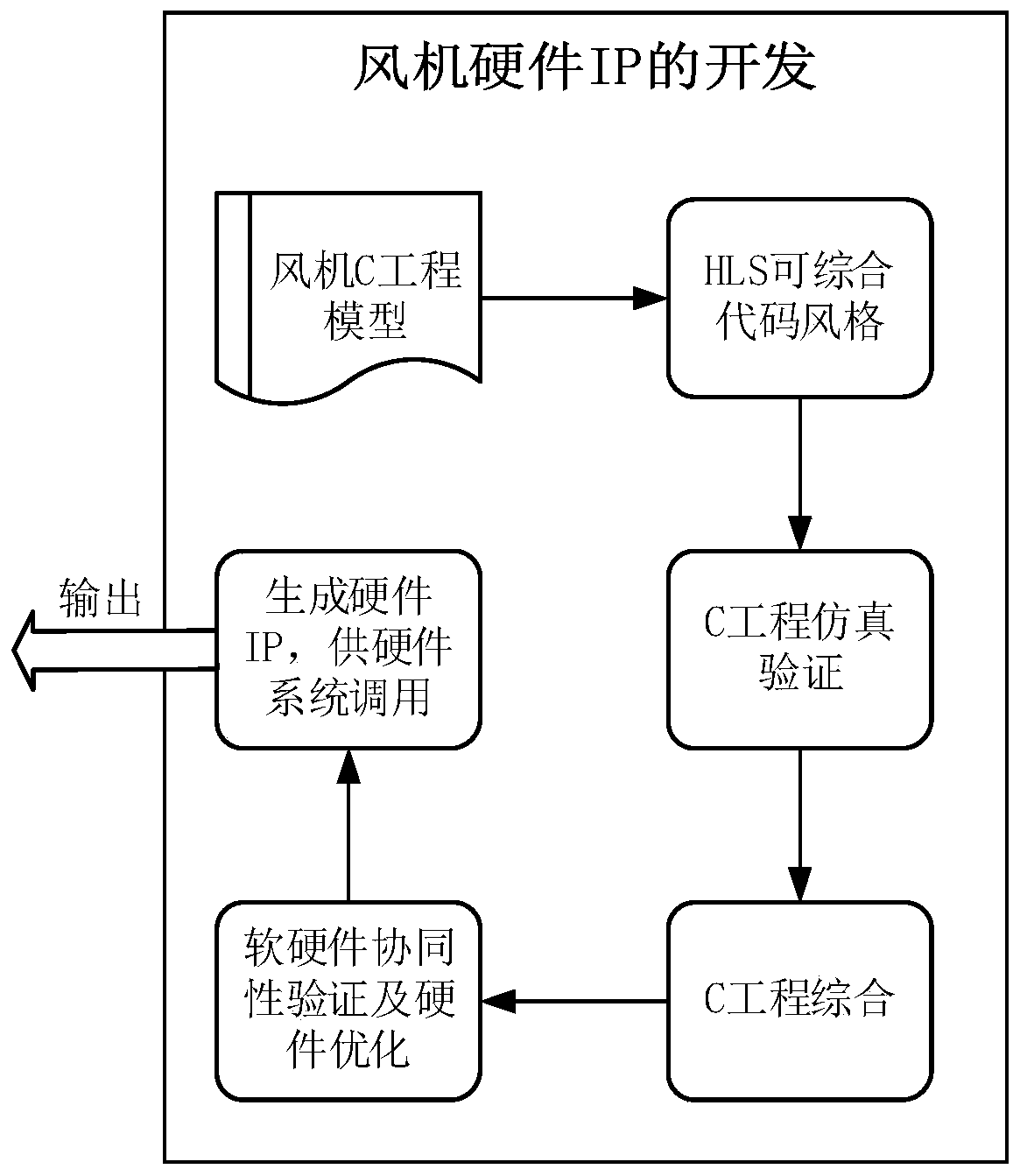

FPGA-based doubly-fed wind motor electromagnetic transient simulation method and simulation system

ActiveCN110334407AReal-time simulationGuaranteed Simulation AccuracyData processing applicationsDesign optimisation/simulationSingle-precision floating-point formatDevelopment period

The invention discloses an FPGA-based doubly-fed wind motor electromagnetic transient simulation method and simulation system, and belongs to the technical field of power system simulation and the field of hardware calculation acceleration. The FPGA-based doubly-fed wind motor electromagnetic transient simulation method comprises the following steps: performing real-time simulation on a decoupleddoubly-fed wind motor circuit on an FPGA according to an equivalent circuit model of a wind motor; rapidly realizing a parameter updating module of the wind power motor by utilizing an HLS high-levelcomprehensive technology, so that the development period of a hardware system is shortened; meanwhile, carrying out simulation calculation by using a single-precision floating-point number in the parameter updating module, so that the utilization rate of FPGA hardware resources is reduced while relatively high calculation precision is kept; and by adopting Park transformation, reducing repeated calculation of a parameter updating area, and further reducing hardware resource consumption. The FPGA-based doubly-fed wind motor electromagnetic transient simulation method and simulation system havethe advantages of being the clear and definite in system structure, being convenient to transplant and expand, being excellent in simulation performance, and being capable of achieving real-time simulation, thus being particularly suitable for electromagnetic transient real-time simulation calculation of the doubly-fed wind motor on an FPGA parallel architecture platform.

Owner:SHANGHAI JIAO TONG UNIV +1

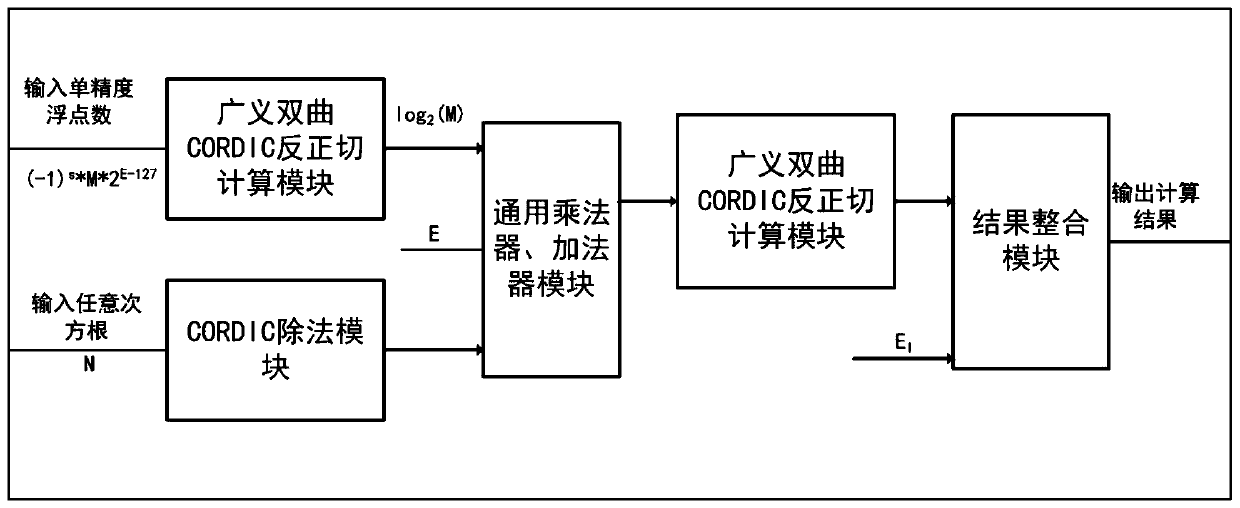

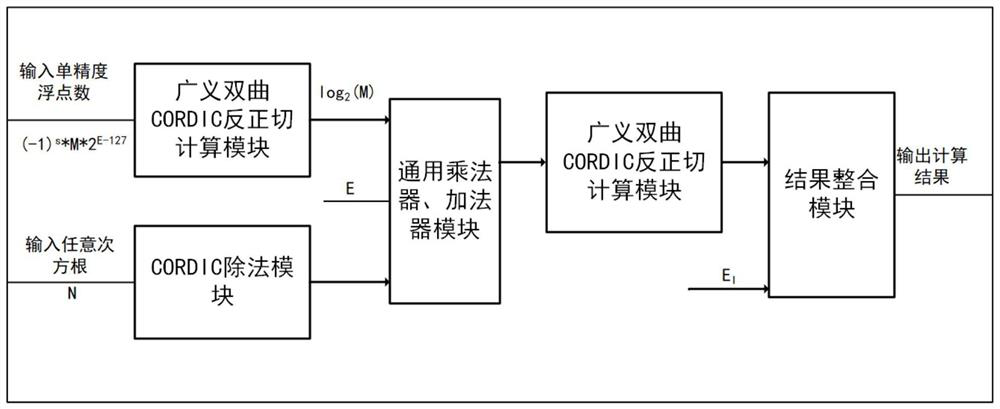

Arbitrary power square root solving method for single-precision floating-point number and solver of arbitrary power square root solving method

The invention provides an arbitrary power square root solving method for a single-precision floating-point number and a solver of the arbitrary power square root solving method. The solver comprises:a division calculation module for carrying out division operation on an input power root value N; an arc tangent value calculation module for carrying out arc tangent value calculation operation on amantissa part M of the input single-precision floating-point number and obtaining a log2M; a calculation module for carrying out multiplication and addition operation on an exponent part E of a single-precision floating-point number, a reciprocal 1 / N of the root value N of the power and the log2M of the numerical value; a sine and cosine calculation module for solving hyperbolic sine and cosine values with 2 as the bottom for the calculation result obtained by the calculation module; and a calculation result integration module for summing the solved hyperbolic sine and hyperbolic cosine valuesand integrating the sum with an intermediate calculation result of the index part E to obtain a final calculation result in a single-precision floating-point number format. The solver provided by theinvention can calculate any power root value of any single-precision floating-point number, and has certain universality.

Owner:NANJING UNIV

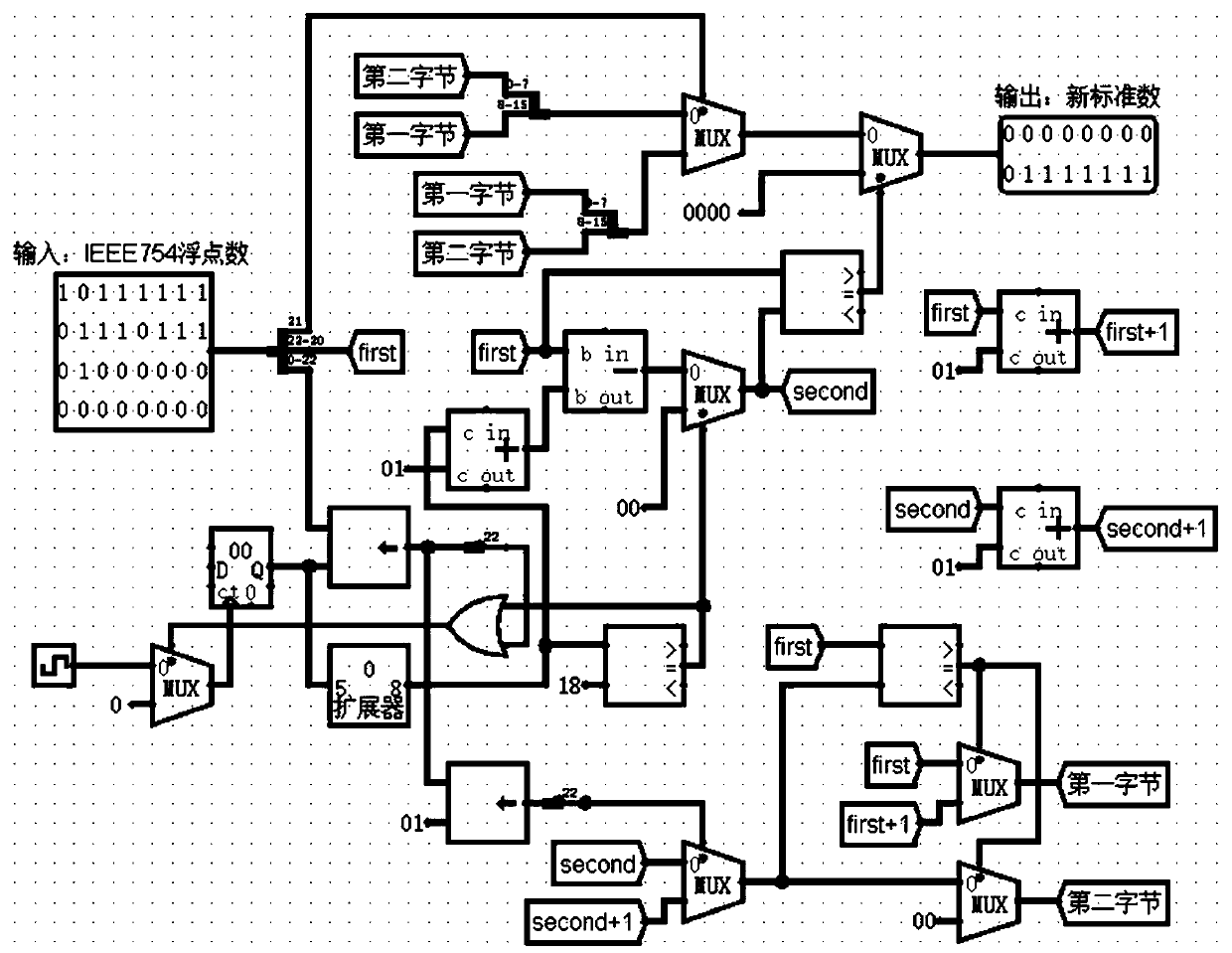

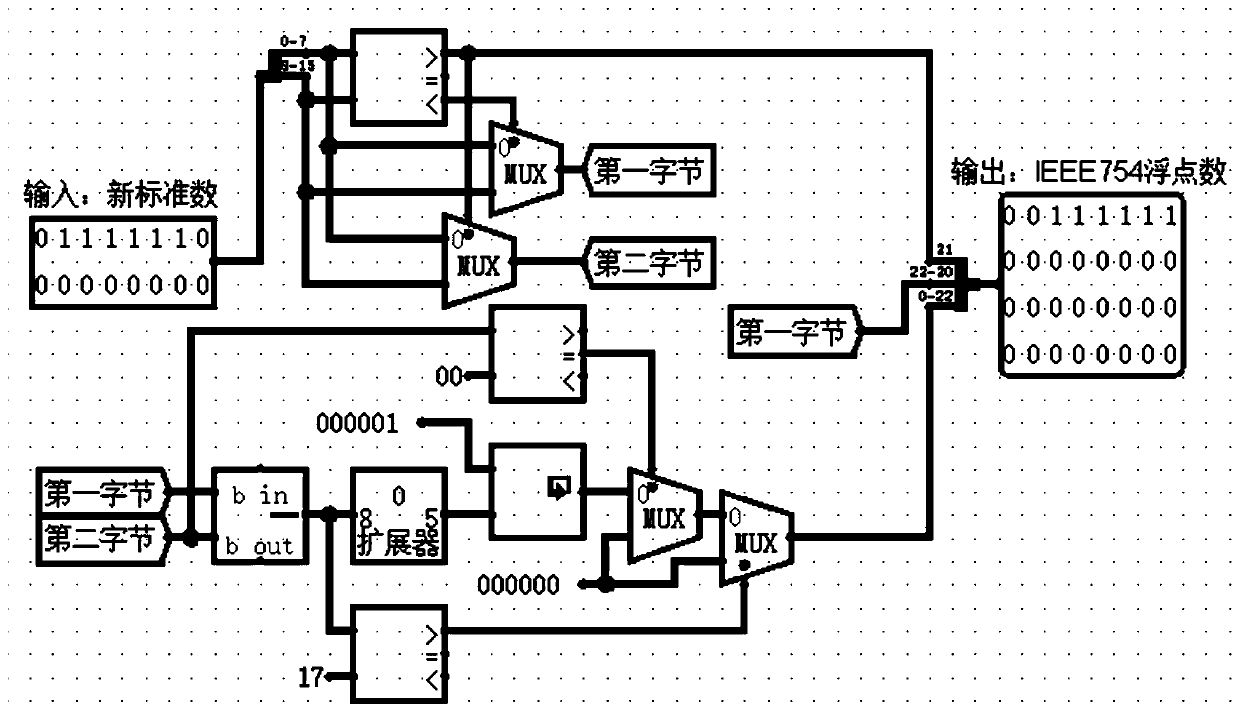

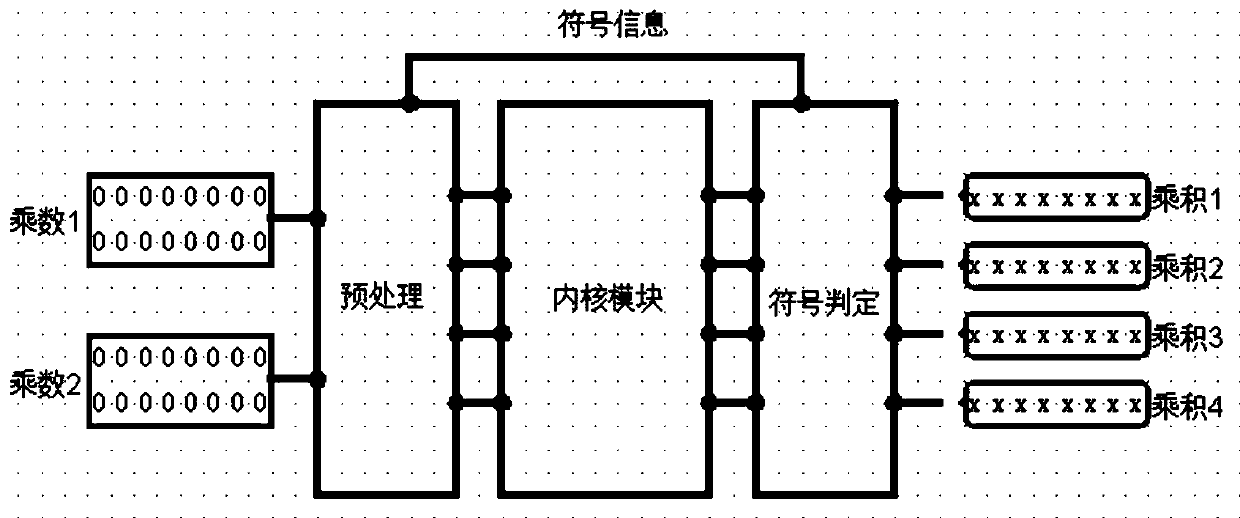

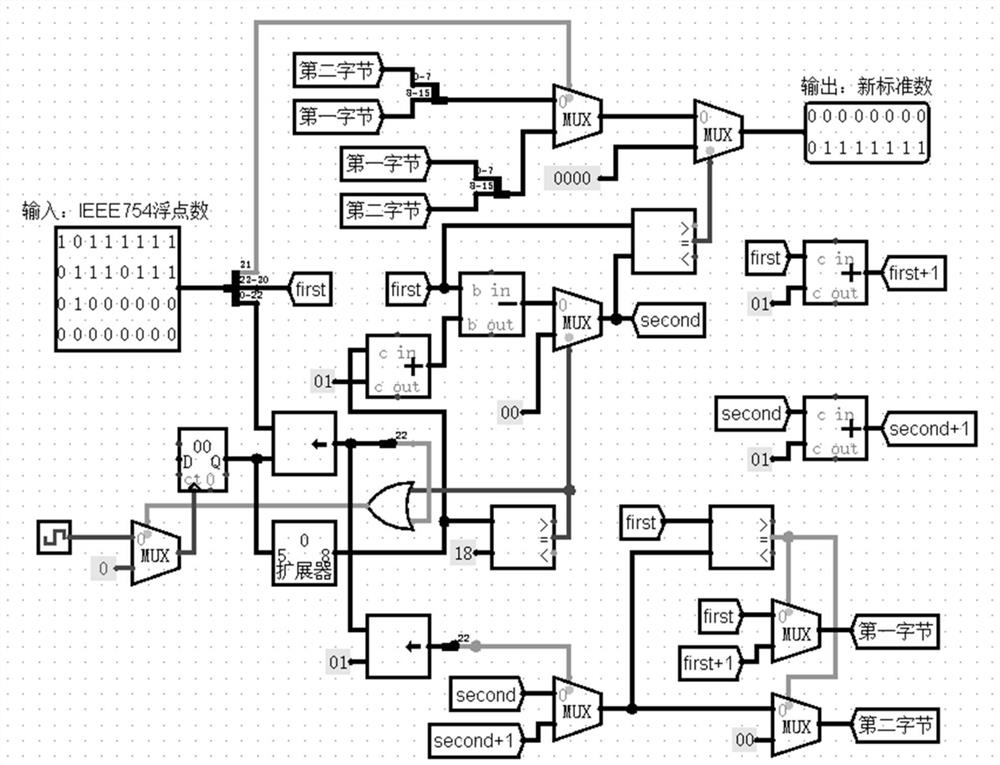

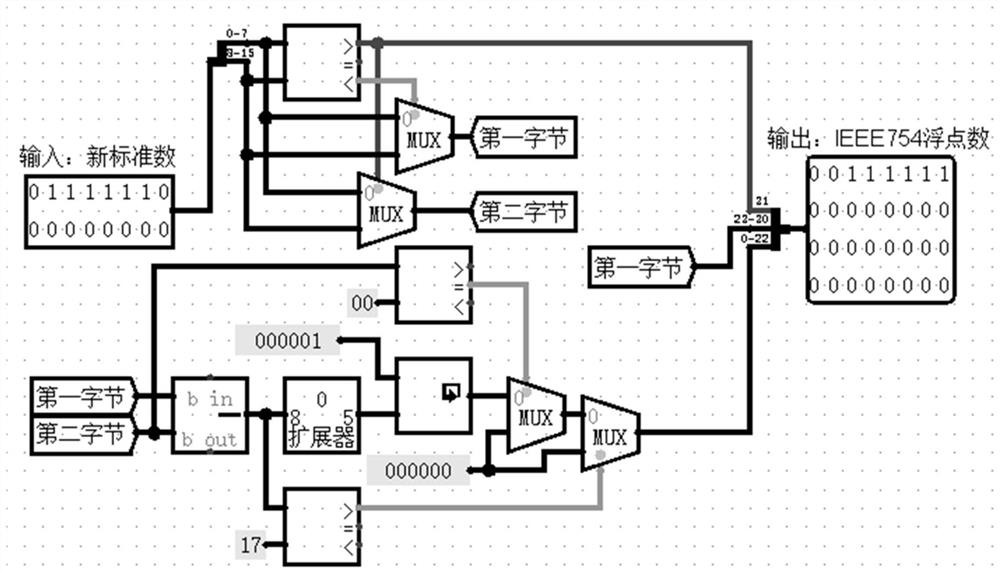

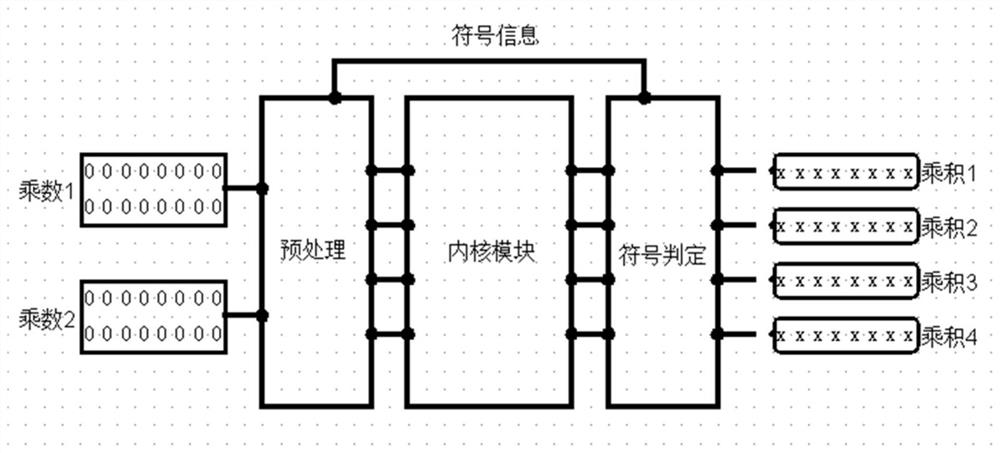

Data conversion method, multiplier, adder, terminal device and storage medium

ActiveCN110888623AThe numerical value represents a large rangeReduce computational overheadComputation using non-contact making devicesNeural architecturesData transformationBinary multiplier

The invention relates to a data conversion method, a multiplier, an adder, terminal equipment and a storage medium. The method comprises the following steps: inputting a floating-point number F; converting the input floating-point number F according to the following conversion rules: a formula (shown in the description), ai is an integer number, each integer number is n bits, i is a serial number,and k is the number of integer numbers; according to the converted floating-point number F, setting the converted new standard number as a number formed by arranging k integer numbers ai of n bits from high to low in a descending order or ascending order; when the floating-point number F is equal to 0, enabling the k integer numbers of n bits to be all negative infinity; and outputting the converted new standard number. According to the method, the advantage of large numerical representation range of the single-precision floating-point number is reserved, and the calculation overhead of the floating-point number multiplication operation is reduced, so that the calculation overhead of the deep neural network algorithm can be reduced, and a solution is provided for the deployment of the deep neural network algorithm on low-cost and low-power equipment.

Owner:JIMEI UNIV

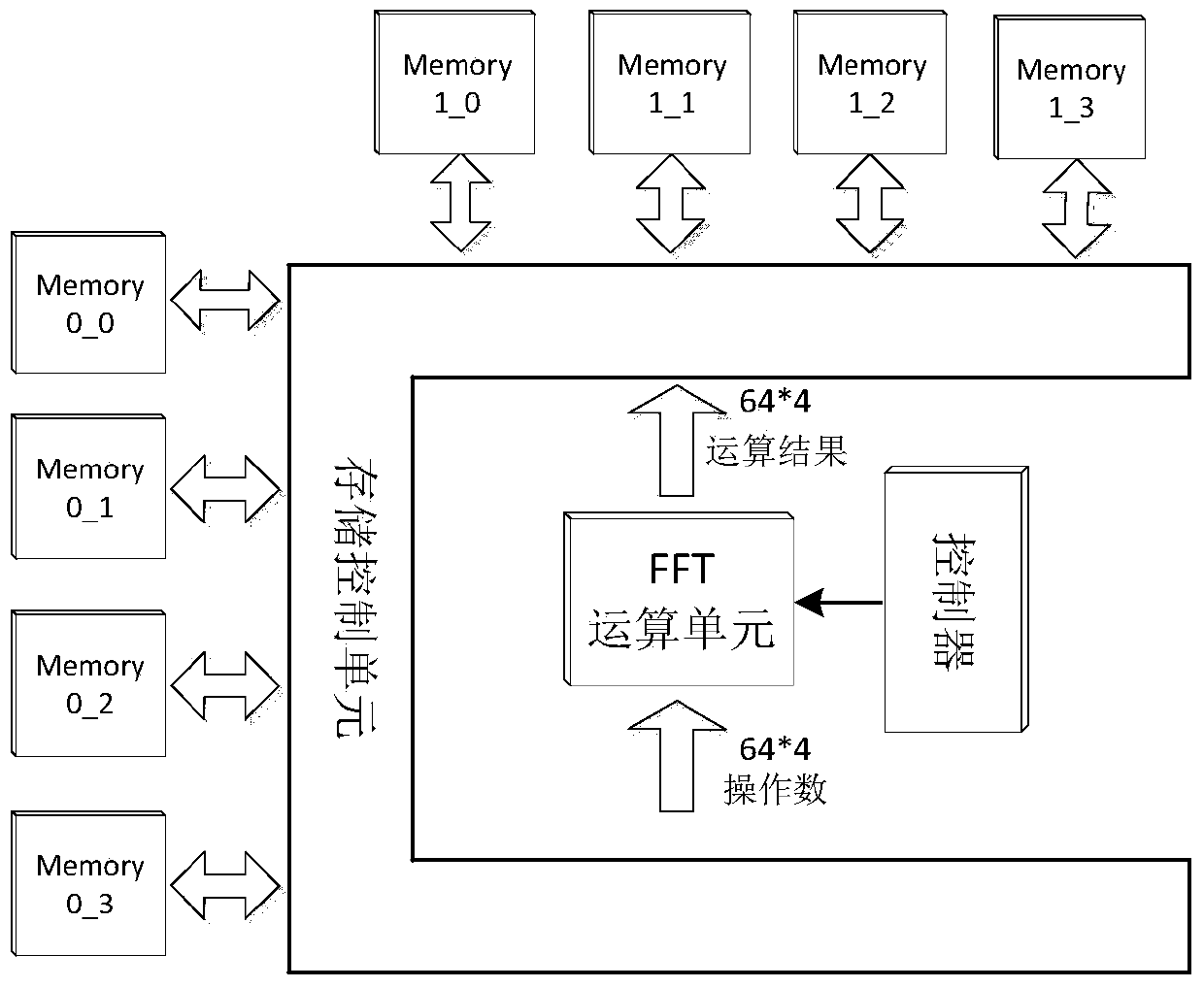

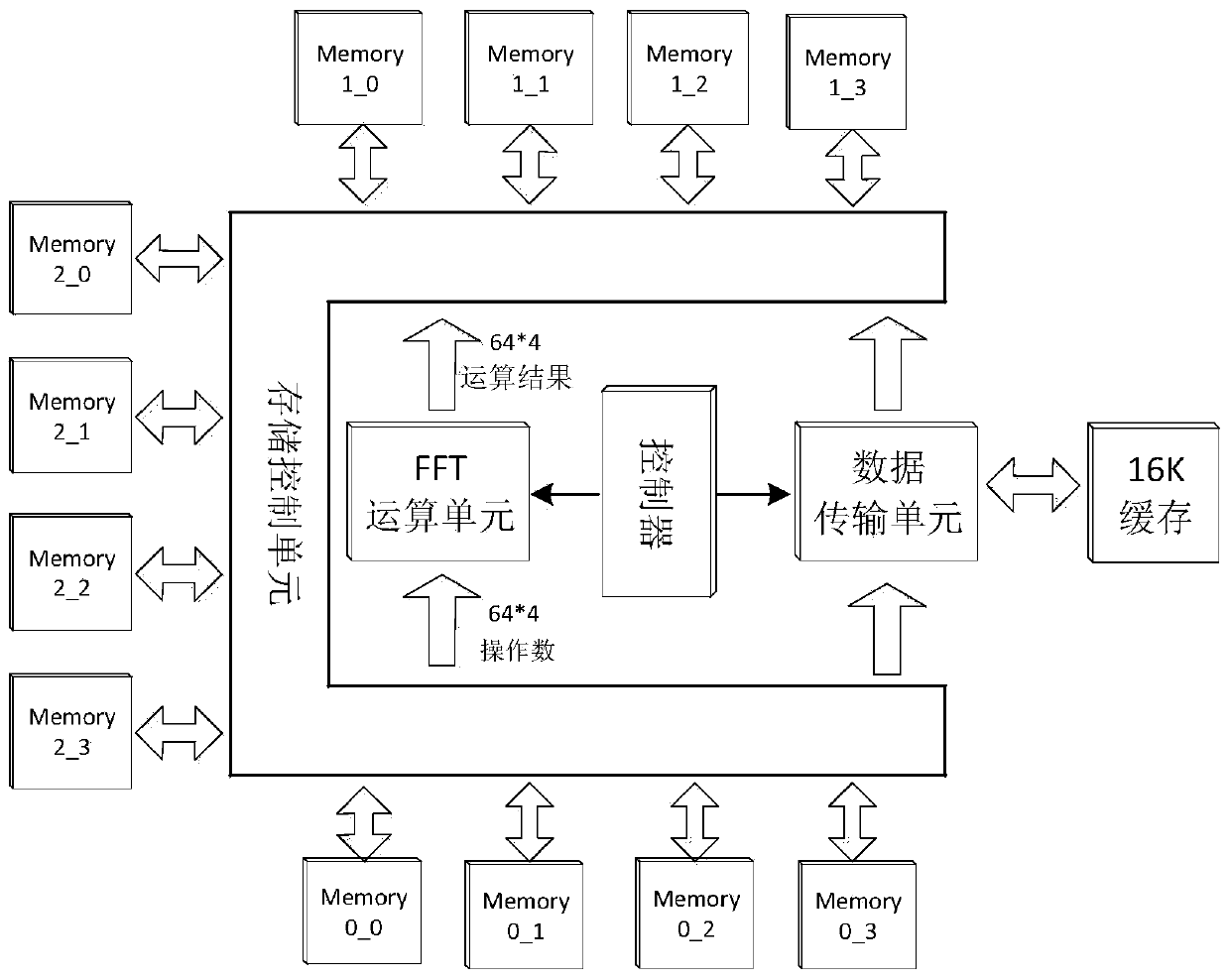

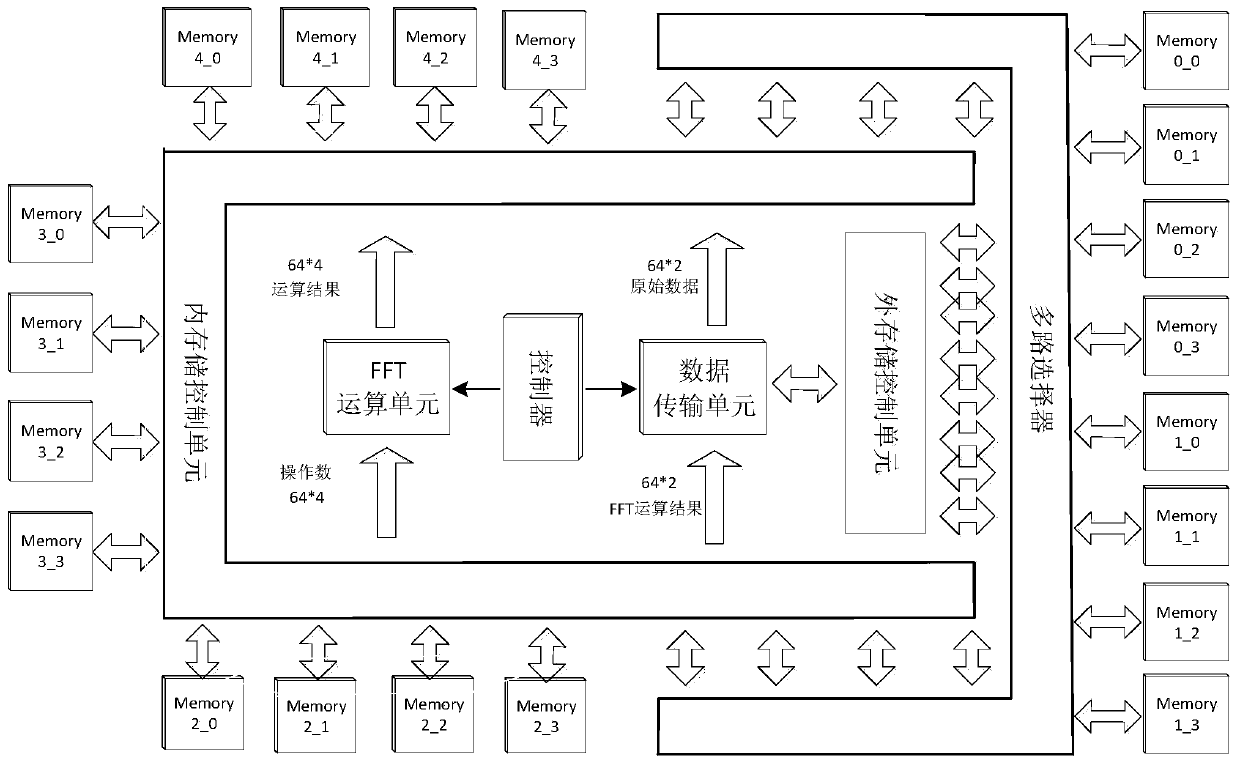

1-D/2-D hybrid architecture FFT (Fast Fourier Transform) processor

ActiveCN103699517ASave storage resourcesUniform speedComplex mathematical operationsFast Fourier transformComputer architecture

The invention discloses a 1-D / 2-D hybrid architecture FFT processor, which is characterized in that the processor executes FFT or IFFT (Inverse Fast Fourier Transform) operation of any 2n point 32-bit single-precision floating point number from 32 point to 8K point through a one-dimensional FFT operation mode, executes FFT or IFFT operation of 16K point 32-bit single-precision floating point number through a two-dimensional operation mode, and realizes FFT / IFFT operation of any 2n point (n = 5, 6... 14) single-precision floating point number. The FFT processor provided by the invention carries out FFT or IFFT operation on data through a one-dimensional operation and two-dimensional operation hybrid mode, comprehensively considers FFT operation speed, storage resource consumption and flexibility, integrates the advantages of fast operation speed of the one-dimensional FFT processor and less storage resource of the two-dimensional FFT processor, and realizes balance between speed and resource.

Owner:HEFEI UNIV OF TECH

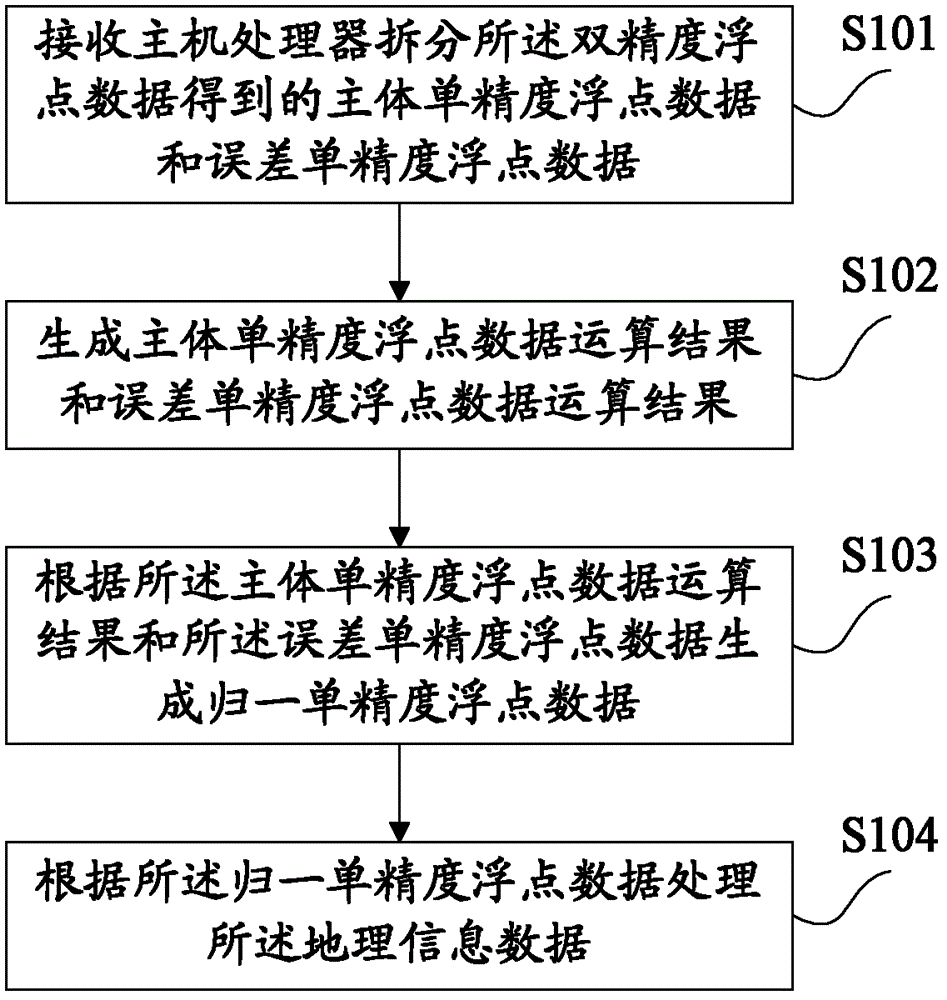

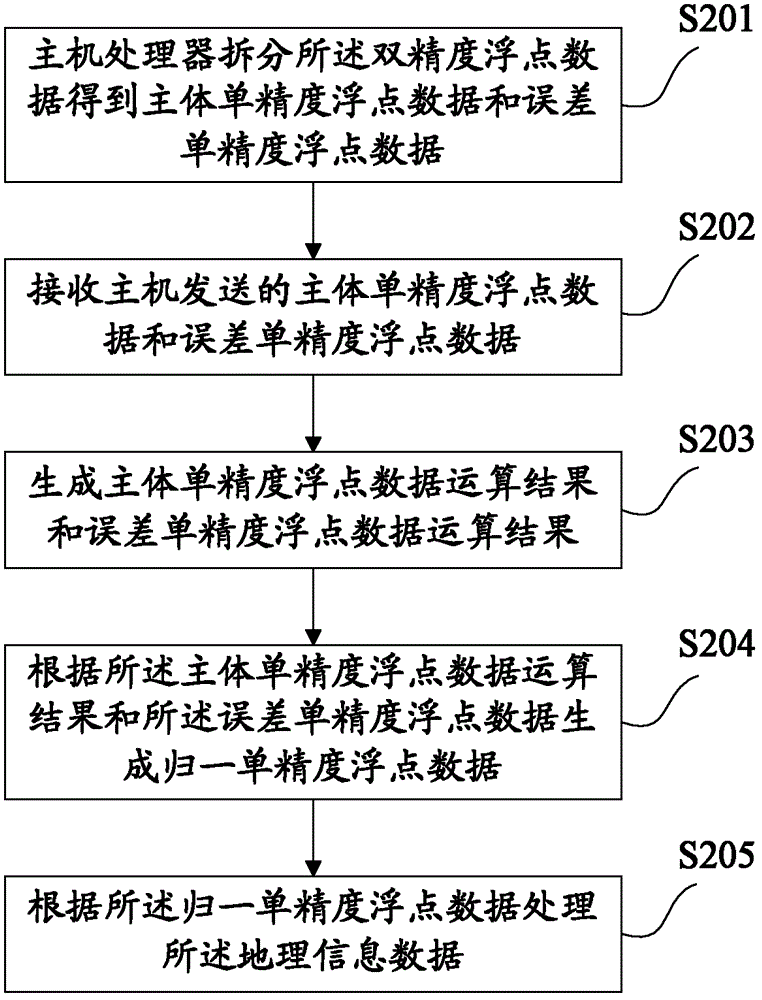

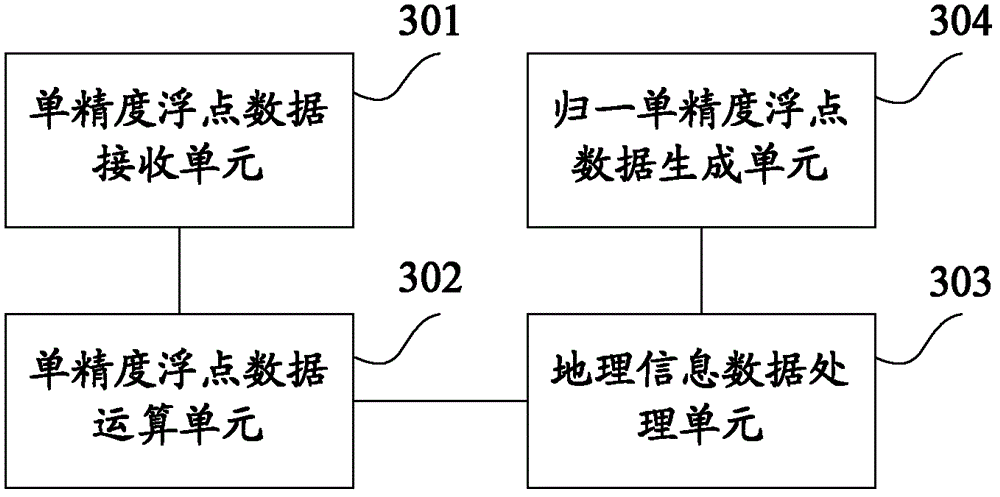

Method, device and system for geographic information data processing based on graphics processing unit (GPU)

InactiveCN102750663ARealize processingImprove processing efficiencyProcessor architectures/configurationComputational scienceGraphics processing unit

An embodiment of the invention discloses a method, a device and a system for geographic information data processing based on a graphics processing unit (GPU). The method includes the following steps: receiving main body single-precision floating point data and error single-precision floating point data which are respectively obtained through double-precision floating point data dividing operated by a main machine processor; operating the main body single-precision floating point data and the error single-precision floating point data according to a preset operation rule and leading the operation result to generate unified single-precision floating point data; and processing geographic information data according to the unified single-precision floating point data. In the embodiment, the double-precision floating point data are divided by the main machine processor, the GPU operates the divided single-precision floating point data, the geographic information data are processed according to the operation result, geographic information data processing with the GPU is achieved, and processing efficiency is improved.

Owner:CHINA DIGITAL VIDEO BEIJING

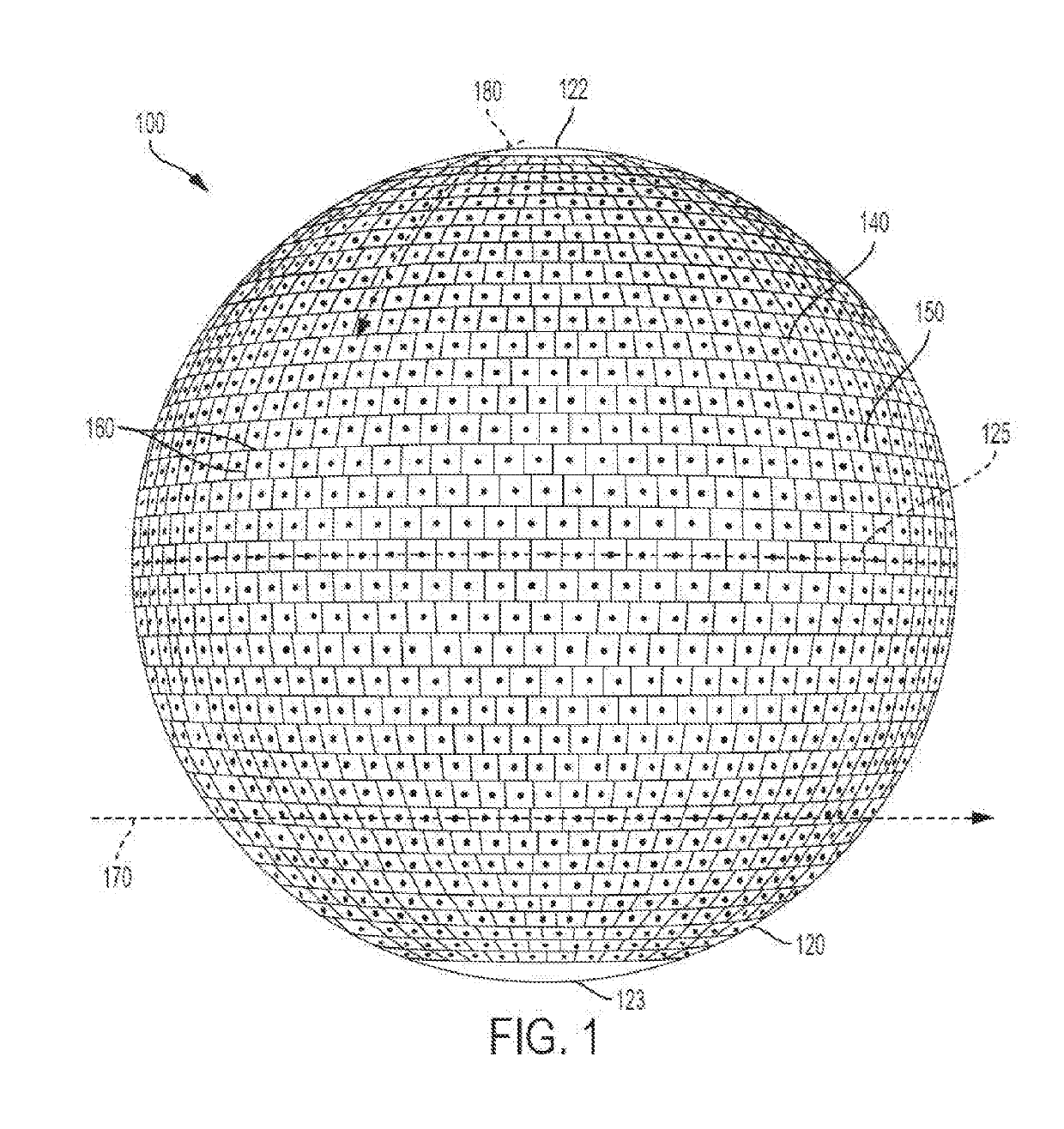

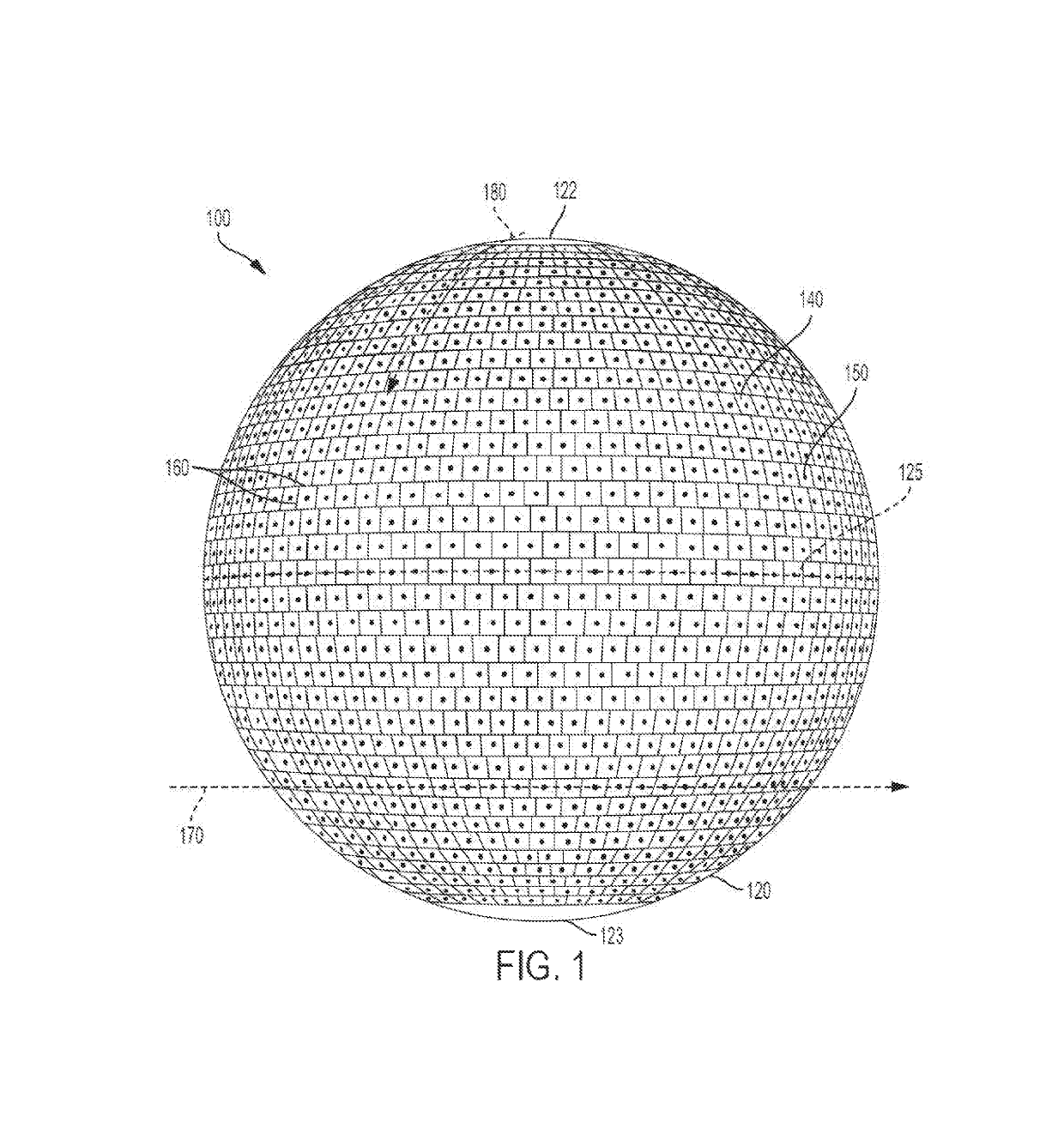

Planet-scale positioning of augmented reality content

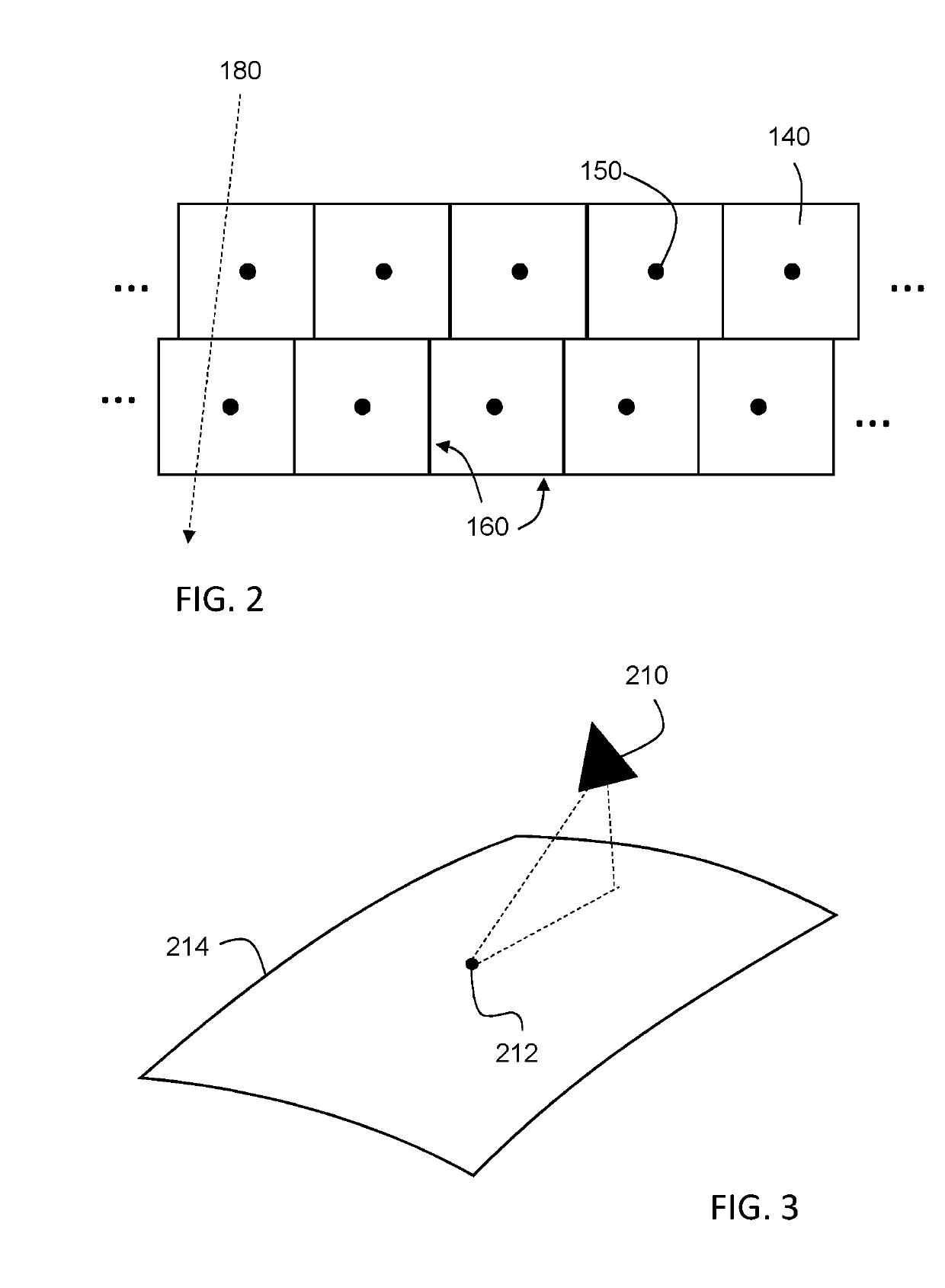

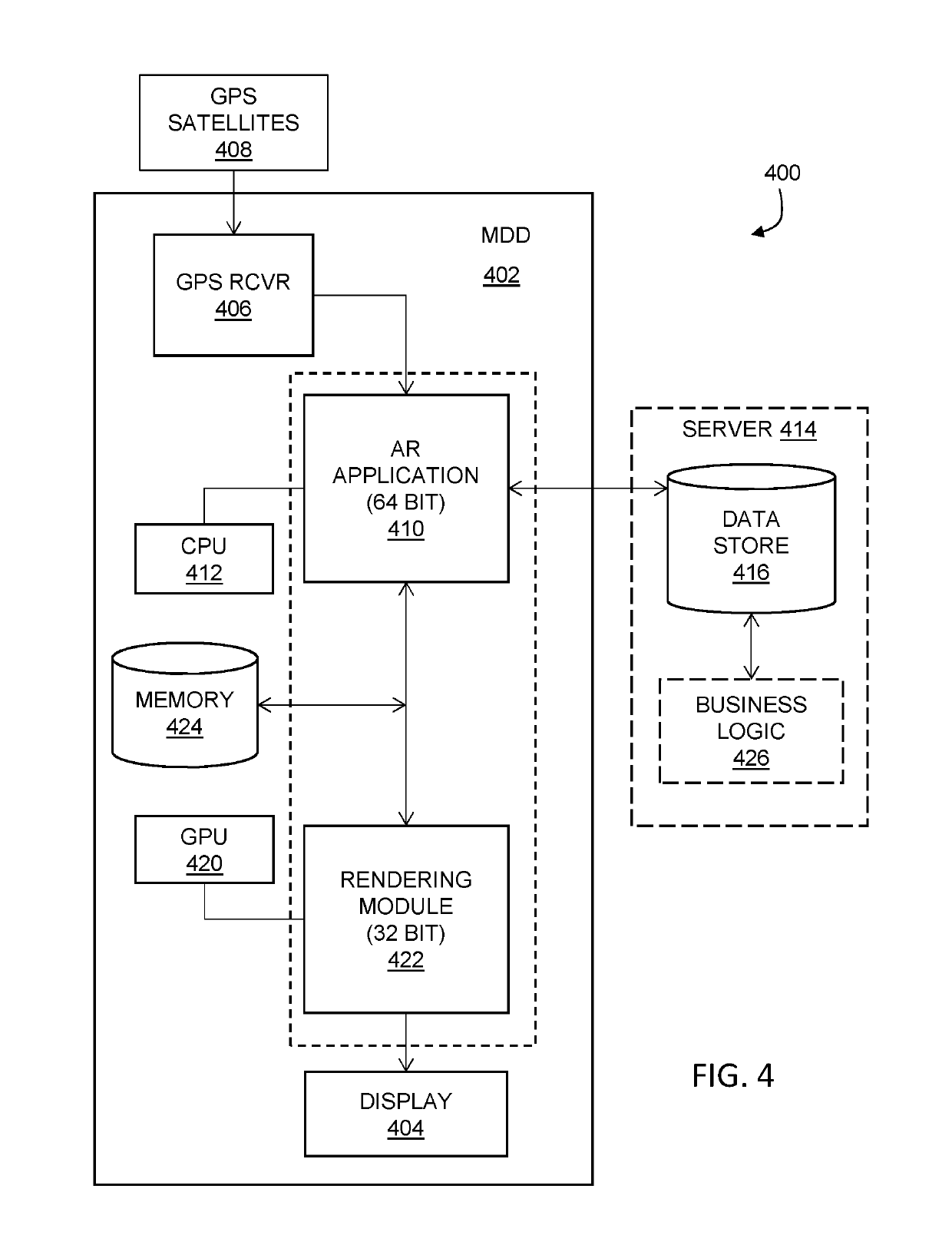

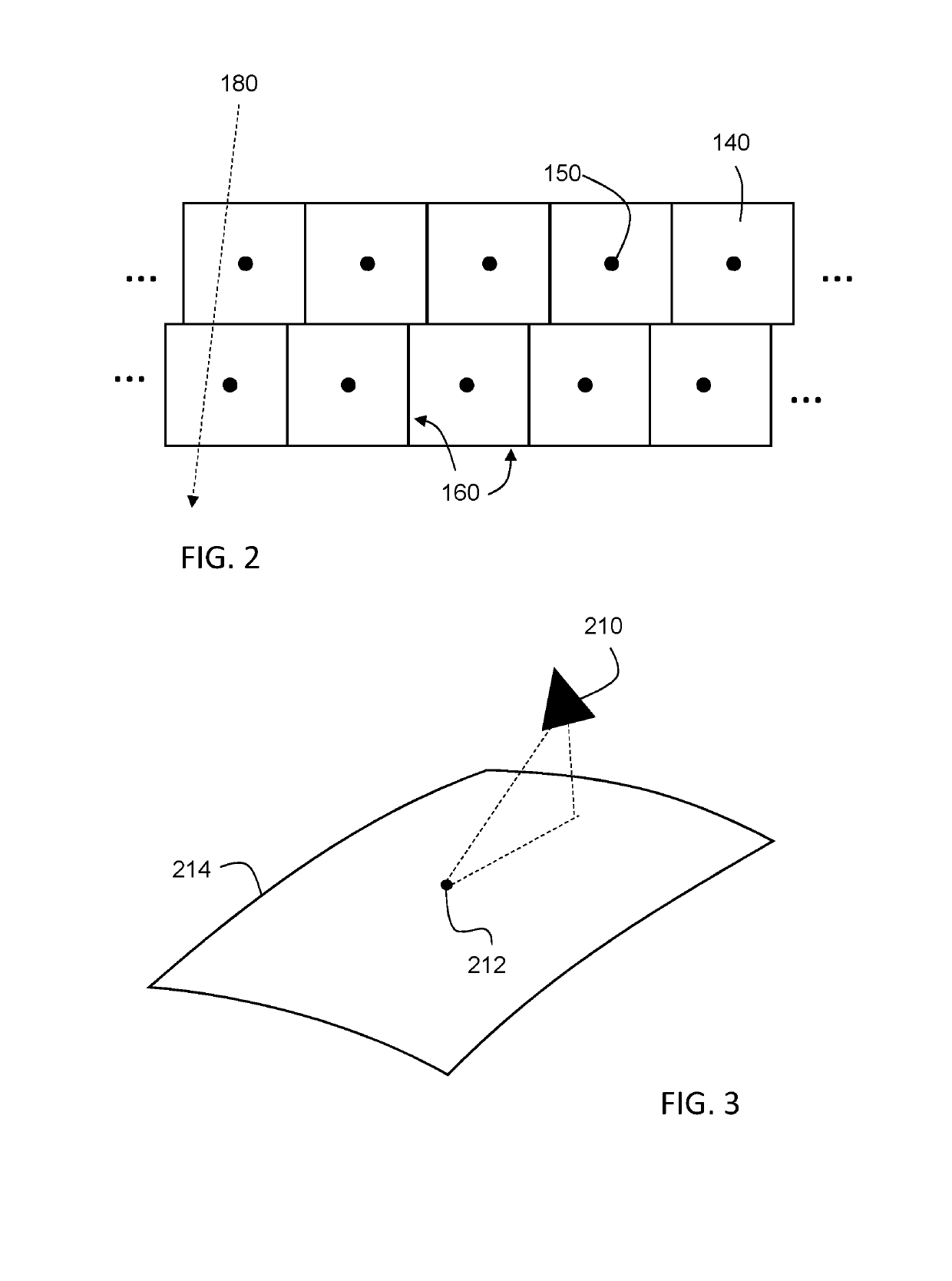

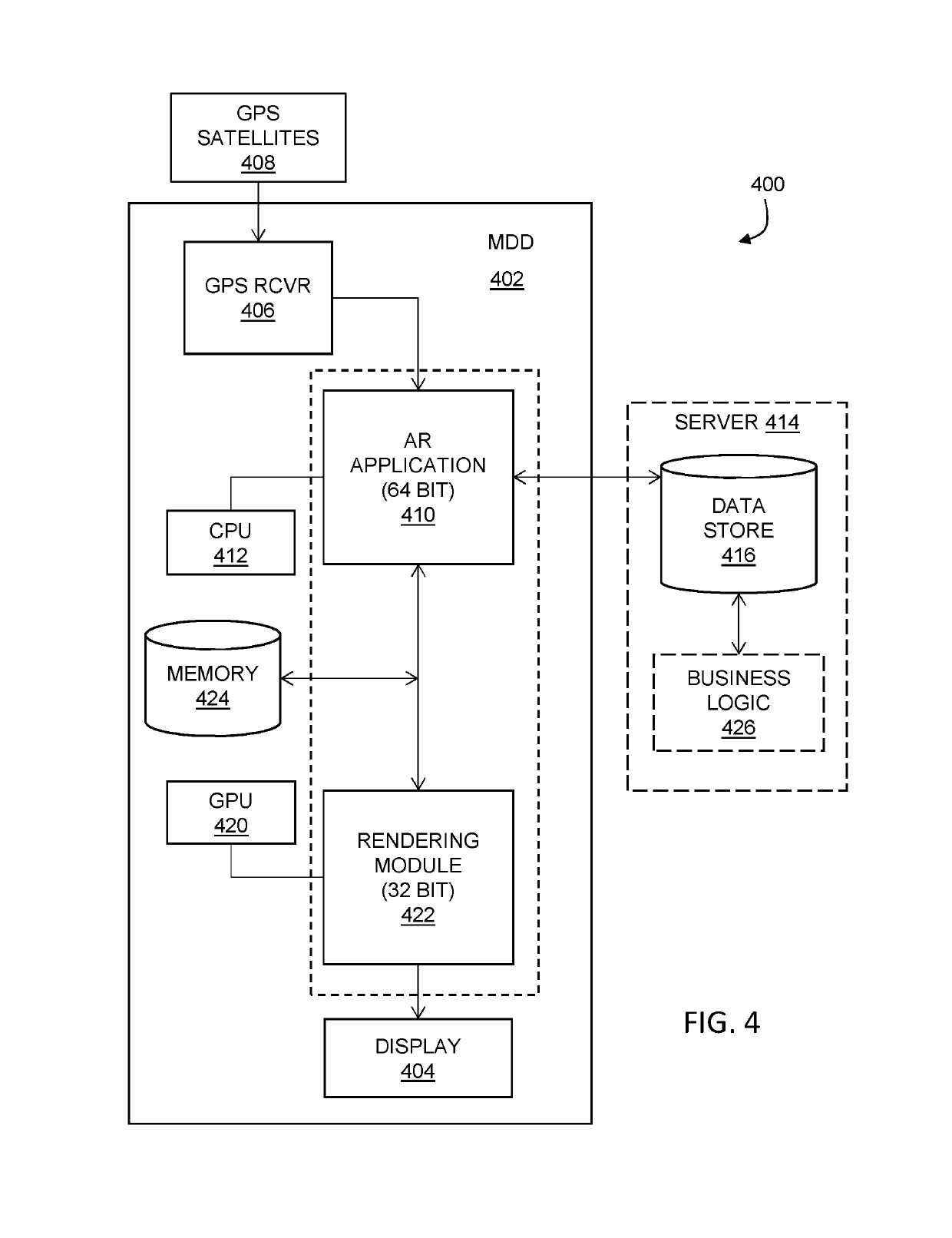

Cell-based augmented reality (AR) content positioning systems may include a reference grid of cells, each of which includes a 32-bit intracellular coordinate system based on a respective reference point of the cell. Cell topology is selected such that the intracellular coordinate systems may utilize single-precision floating point numbers while retaining the ability to define content positions with, e.g., millimeter-level precision. Accordingly, rendering of AR content may be performed at a high precision using 32-bit devices and methods.

Owner:YOUAR INC

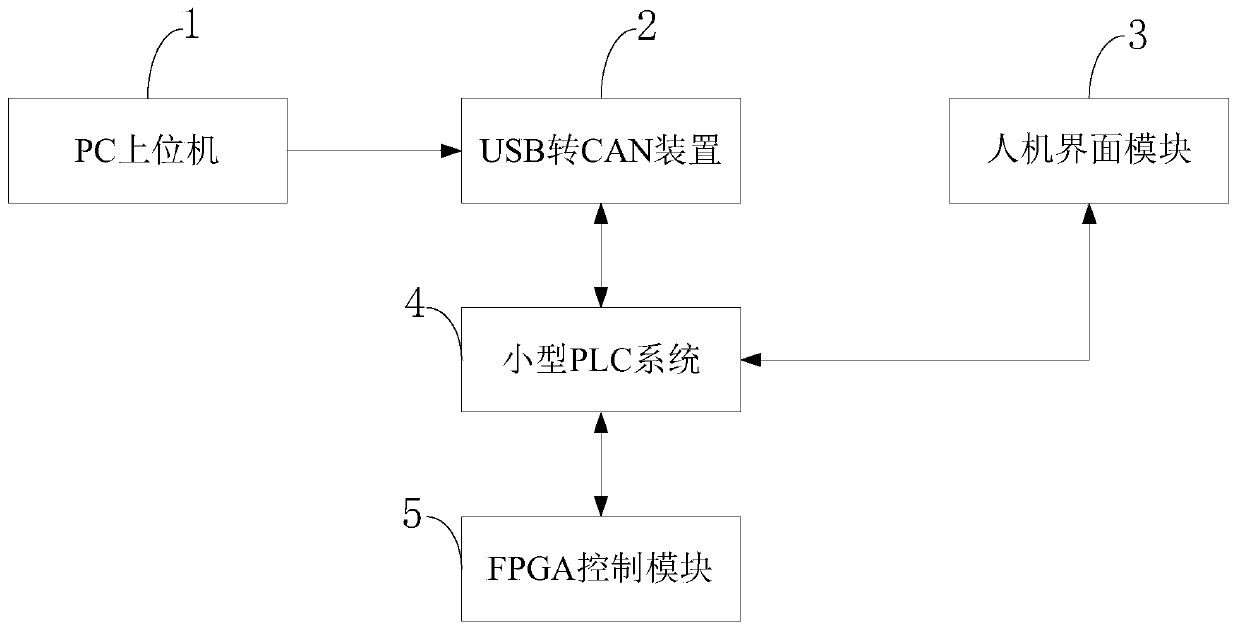

PLC floating-point number and fixed-point number mutual conversion control system and method

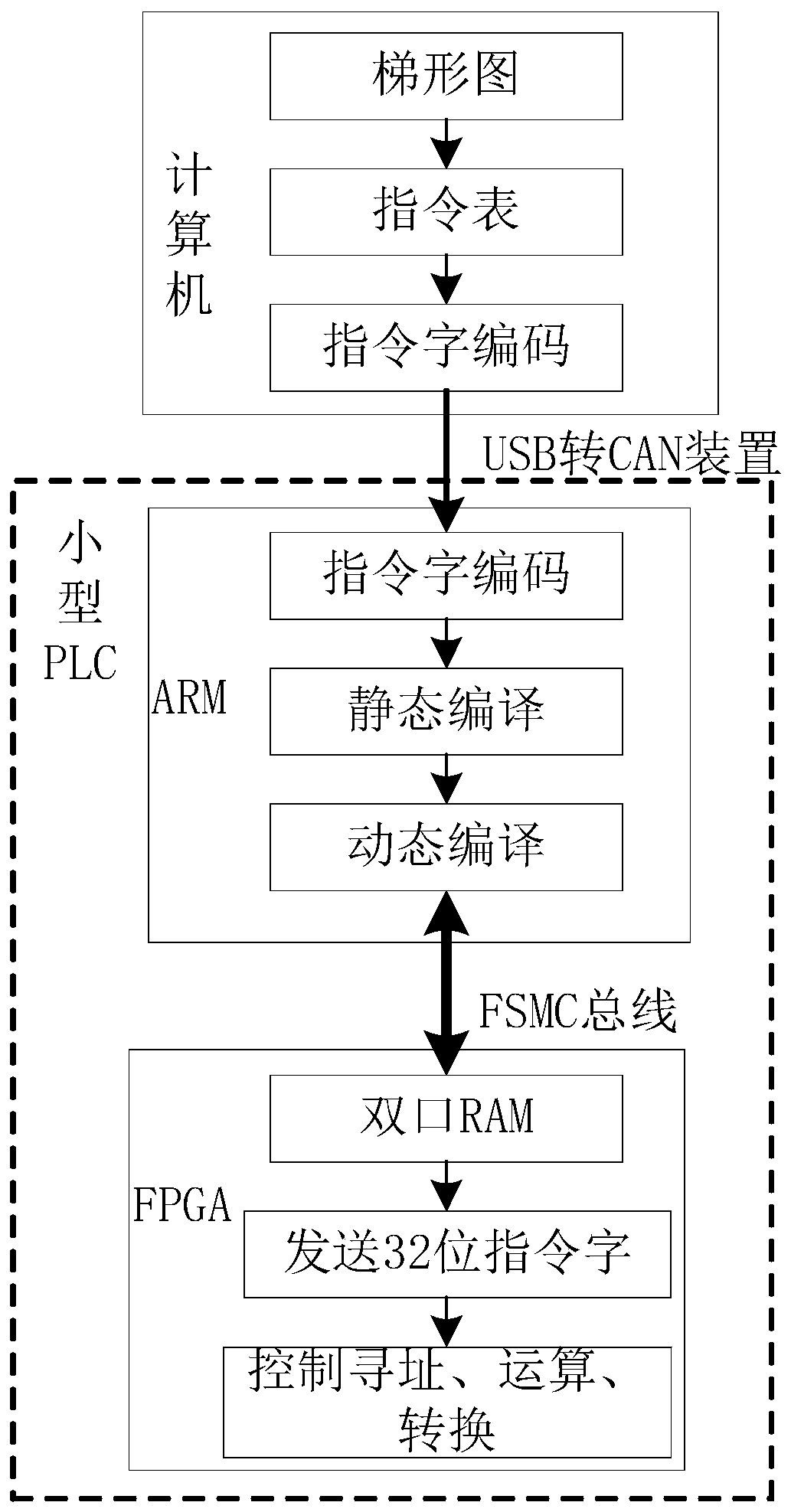

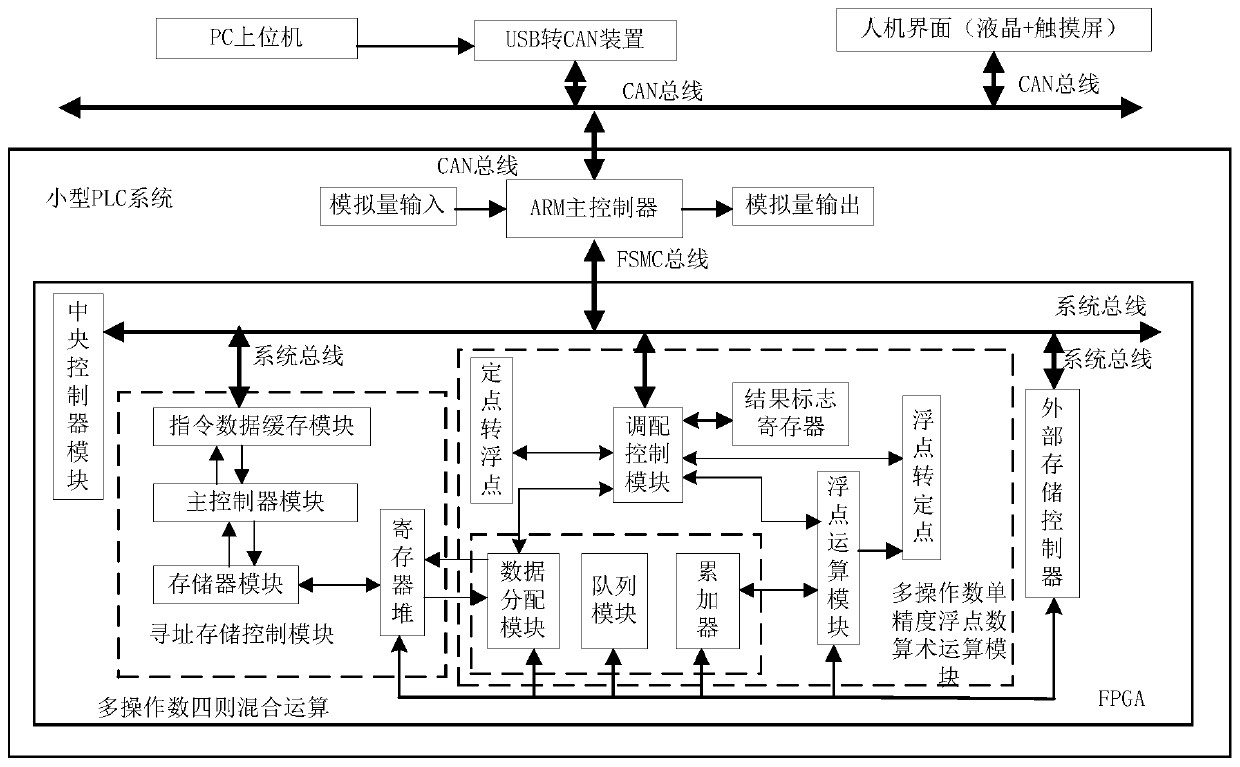

ActiveCN111123818AExecution does not affectImprove processing speedProgramme control in sequence/logic controllersControl storeBus mastering

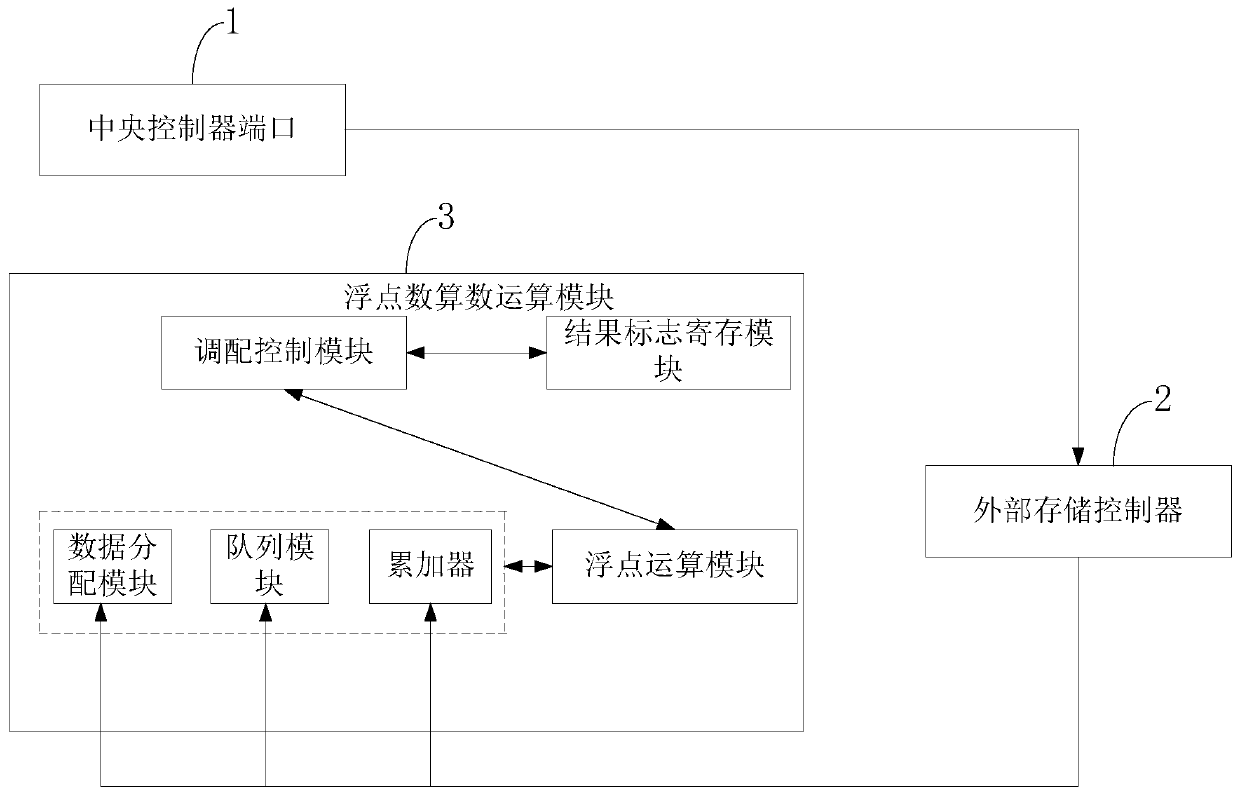

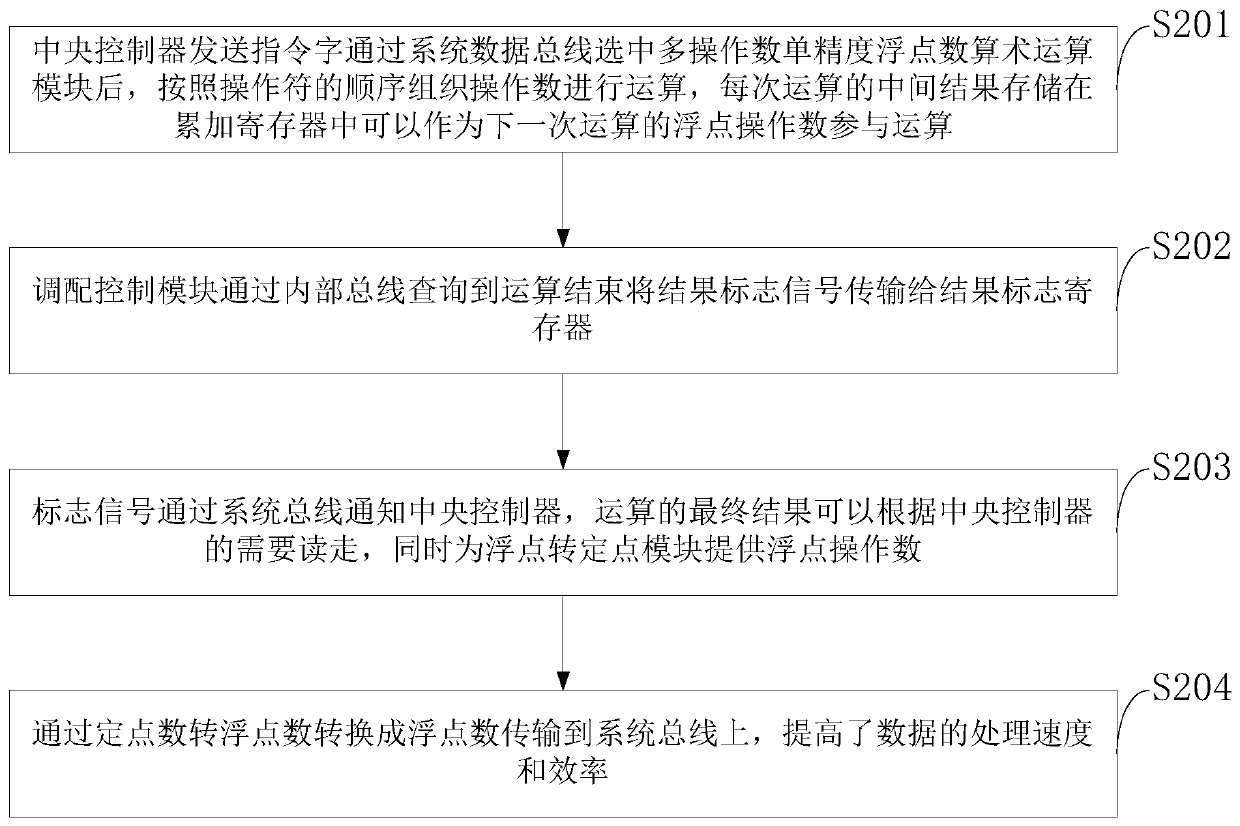

The invention belongs to the technical field of PLC control, and discloses a PLC floating-point number and fixed-point number mutual conversion control system and method. The system comprises: a central controller port, which is used for controlling an external storage controller and a floating-point number arithmetic operation module through a data bus, an address bus and a control bus; the external storage controller, which is used for transmitting operands to a register file module, a data distribution module, a queue module, an accumulator module and a floating-point operation module through internal data channel lines; and the floating-point number arithmetic operation module, which is used for carrying out single-precision floating-point number operation. According to the invention,the mutual conversion efficiency of the floating-point number and the fixed-point number is improved, and the conversion precision is high; a small PLC with an ARM-FPGA framework is adopted, an ARM serves as a control center, the high-speed parallel operation performance of an FPGA is applied, a control logic unit for mutual conversion of floating-point and fixed-point numbers is implanted into the FPGA processor, the defects of a single module are overcome, and high conversion precision and efficiency are achieved.

Owner:GREE ELECTRIC APPLIANCES INC

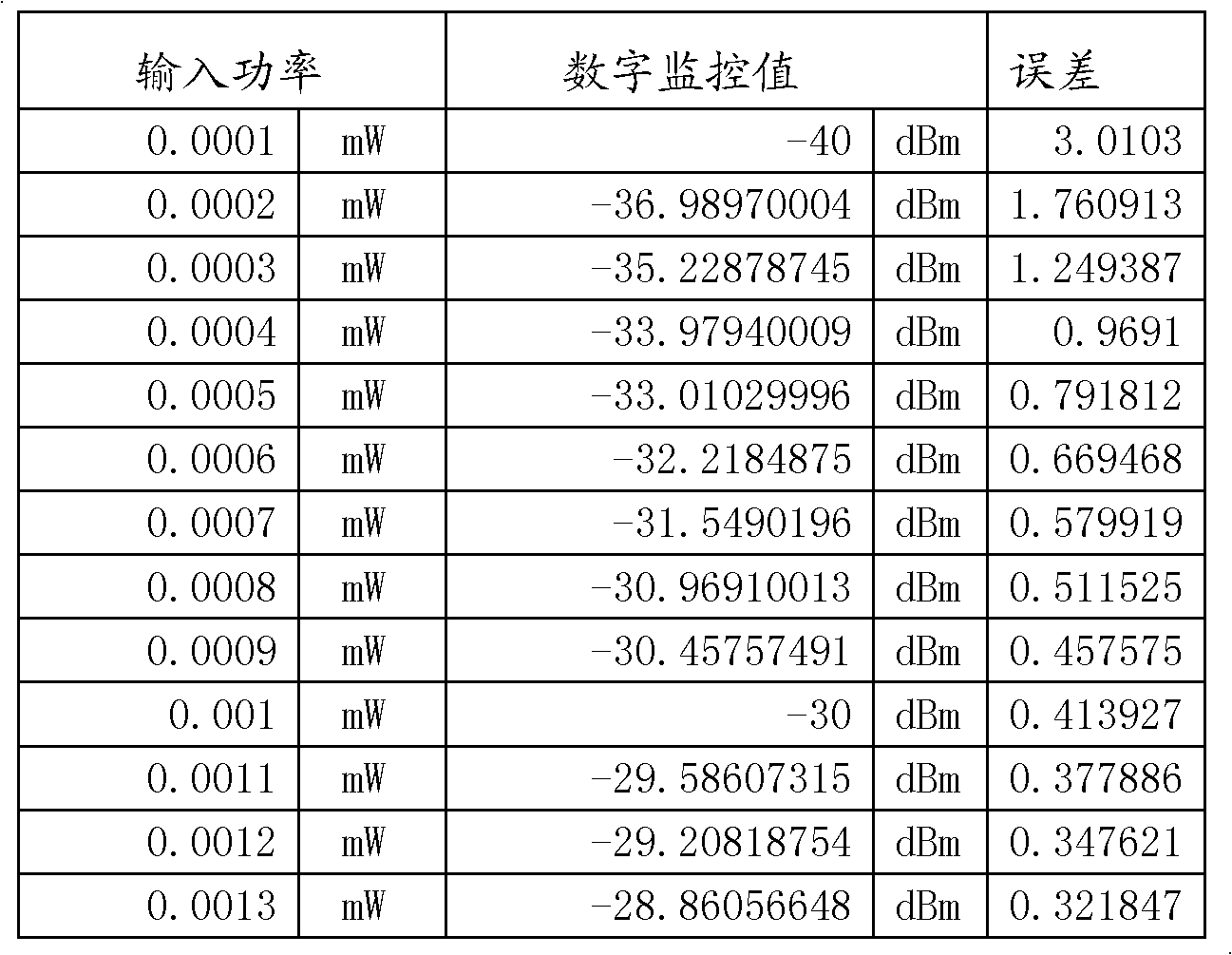

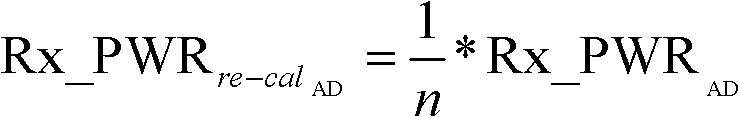

Method for improving digital monitoring precision of optical power on receiving end of passive optical network optical line terminal (PON OLT) optical module

ActiveCN102624450AImprove monitoring accuracyNarrow down the scope of monitoringMultiplex system selection arrangementsElectromagnetic transmissionOptical ModuleSmall form factor

The invention discloses a method for improving digital monitoring precision of optical power on a receiving end of a passive optical network optical line terminal (PON OLT) optical module. The method is based on a small form factor-8472 (SFF-8472) protocol, at least four continuous bytes in reserved bytes of the SFF-8472 protocol are selected and are defined as calibration bytes, a float-point number with single precision in the calibration bytes is adopted as a calibration value, and the calibration value is more than 1 but less than 10; a digital monitored sample value of the input power monitored by a digital diagnostics monitoring interface (DDMI) is divided by the calibration value to obtain the calibrated input power sample value, so that the monitoring precision can be effectively improved. Under the situation that a number register is not changed, the monitoring range is narrowed, so that the internal minimal unit is reduced, the error can be effectively reduced, and the monitoring precision requirement of the optical power on the receiving end of the PON OLT can be met.

Owner:SOURCE PHOTONICS CHENGDU

Planet-scale positioning of augmented reality content

Owner:YOUAR INC

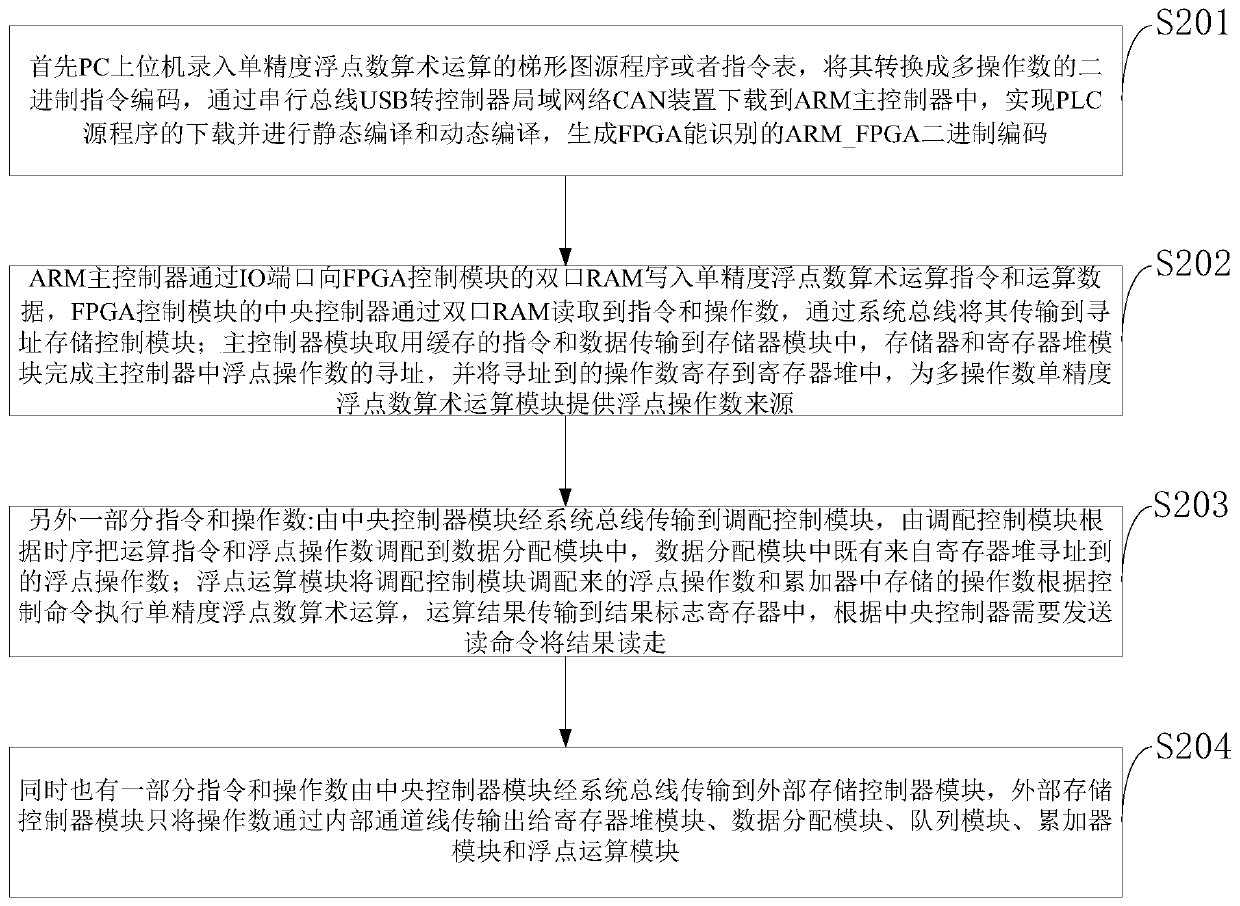

Single-precision floating-point arithmetic operation control system and method for small PLC

ActiveCN111078190AImprove operating speedImprove operating precisionDigital data processing detailsComputer architectureHuman–machine interface

The invention belongs to the technical field of PLC control. The invention discloses a single-precision floating-point arithmetic operation control system and method for a small PLC. After an ARM maincontroller completes data configuration of an FPGA control module, the ARM main controller sends an operation instruction of single-precision floating-point operands to a dual-port RAM, then a central controller sends a bit instruction to a addressing storage control module to finish addressing and storage of the floating point operands, a single-precision floating point operand arithmetic operation module performs arithmetic operation on the addressing and storage floating point operands, and the central controller of the FPGA control module reads a single-precision operation instruction from the dual-port RAM. According to the invention, an ARM+FPGA is adopted, the ARM serves as a control center, the advantage of cooperative work of the ARM and an FPGA is fully utilized, high-speed parallel operation performance of the FPGA is used for achieving single-precision floating-point operand arithmetic operation, and a computer inputs an instruction from a human-computer interface of a PLCediting module according to an operation code and an operand.

Owner:GREE ELECTRIC APPLIANCES INC

A Method for Solving Arbitrary Roots of Single-precision Floating-point Numbers and Its Solver

ActiveCN111078187BVersatilityLower latencyDigital data processing detailsMechanical engineeringSingle-precision floating-point format

The invention provides a method and a solver for solving an arbitrary power root of a single-precision floating-point number. The solver includes: a division calculation module, which is used to divide the input power root value N; an arctangent value calculation module, which is used to calculate the arctangent value of the mantissa part M of the input single-precision floating-point number and obtain Log value log 2 M; Calculation module, used for the exponent part E of the single-precision floating-point number, the reciprocal 1 / N of the root value N and the logarithmic value log 2 M performs multiplication and addition operations; the sine and cosine calculation module is used to calculate the base 2 hyperbolic sine and cosine values for the calculation results obtained by the calculation module; the calculation result integration module uses the obtained hyperbolic sine and hyperbolic cosine The values are summed and integrated with the intermediate calculation result of the exponent part E to obtain the final calculation result in single-precision floating-point format. The solver of the present invention can calculate any root value of any single-precision floating-point number, and has certain generality.

Owner:NANJING UNIV

Method and device for processing floating point numbers

ActiveCN105224283BImprove computing powerDigital data processing detailsData segmentParallel computing

The embodiment of the present invention discloses a floating-point number processing method and device. The method includes: obtaining the first target floating-point number X and the second target floating-point number Y; obtaining the algorithm of X and Y; judging whether X and Y are not zero ;If both X and Y are not zero and the order codes of X and Y are not equal, then for order X and Y; the mantissas of X and Y after the order will be segmented respectively, and each segment of data will be converted to single precision Floating-point numbers; respectively calculate the results of the corresponding segment data of the mantissas of X and Y; generate the final mantissa according to the calculated results of each segment of data; then generate the calculation results; and normalize the calculation results. By applying the embodiment of the present invention, the mantissa of the high-precision floating-point number is segmented, and each segment of the mantissa is converted into a single-precision floating-point number for calculation, so that low-end GPU products that do not have the ability to calculate double-precision floating-point numbers have high-precision floating-point numbers. The calculation ability of points has improved the calculation ability of low-end GPU products for high-precision floating-point numbers.

Owner:BEIJING QIYI CENTURY SCI & TECH CO LTD

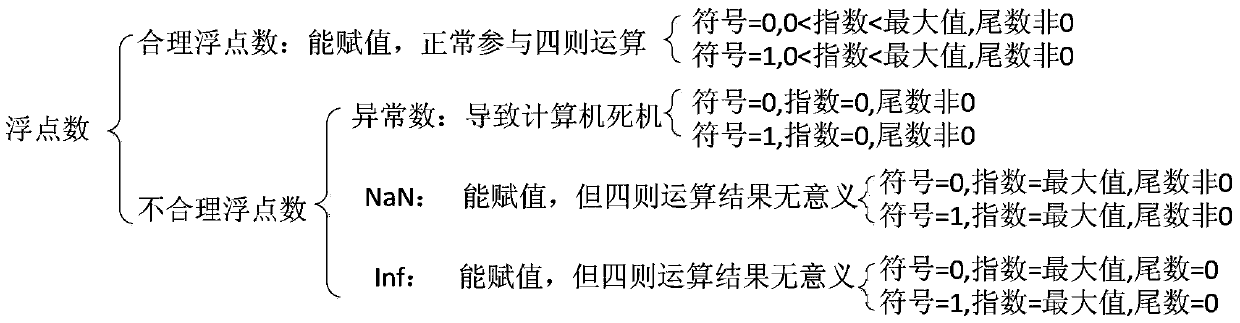

A floating-point data protection method for data link transmission process

ActiveCN104991756BSolve the crash problemSolve the resultDigital data processing detailsProtection procedureTransfer procedure

The invention discloses a floating-point data protection method in the data link transmission process, which abstracts the floating-point data in the transmission process into the representation forms of single-precision floating-point numbers and double-precision floating-point numbers, and then performs bit field operations on them to construct its Data structure, and then get rid of its abnormal numbers and unreasonable numbers to get the correct floating point numbers, thus solving the problem of computer crash or wrong results caused by floating point data errors in the process of multi-byte data link transmission, making embedded The system has higher security and reliability.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

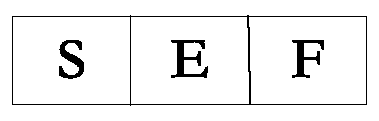

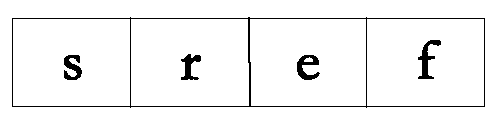

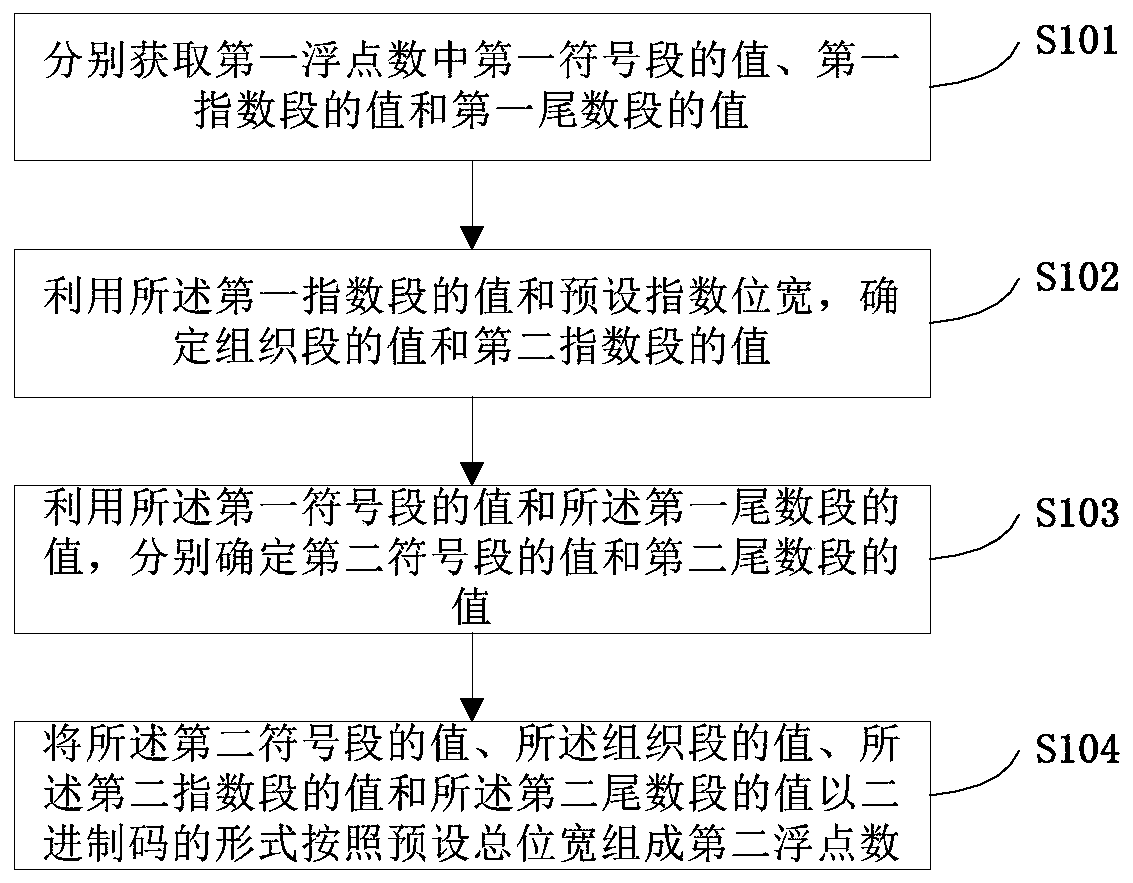

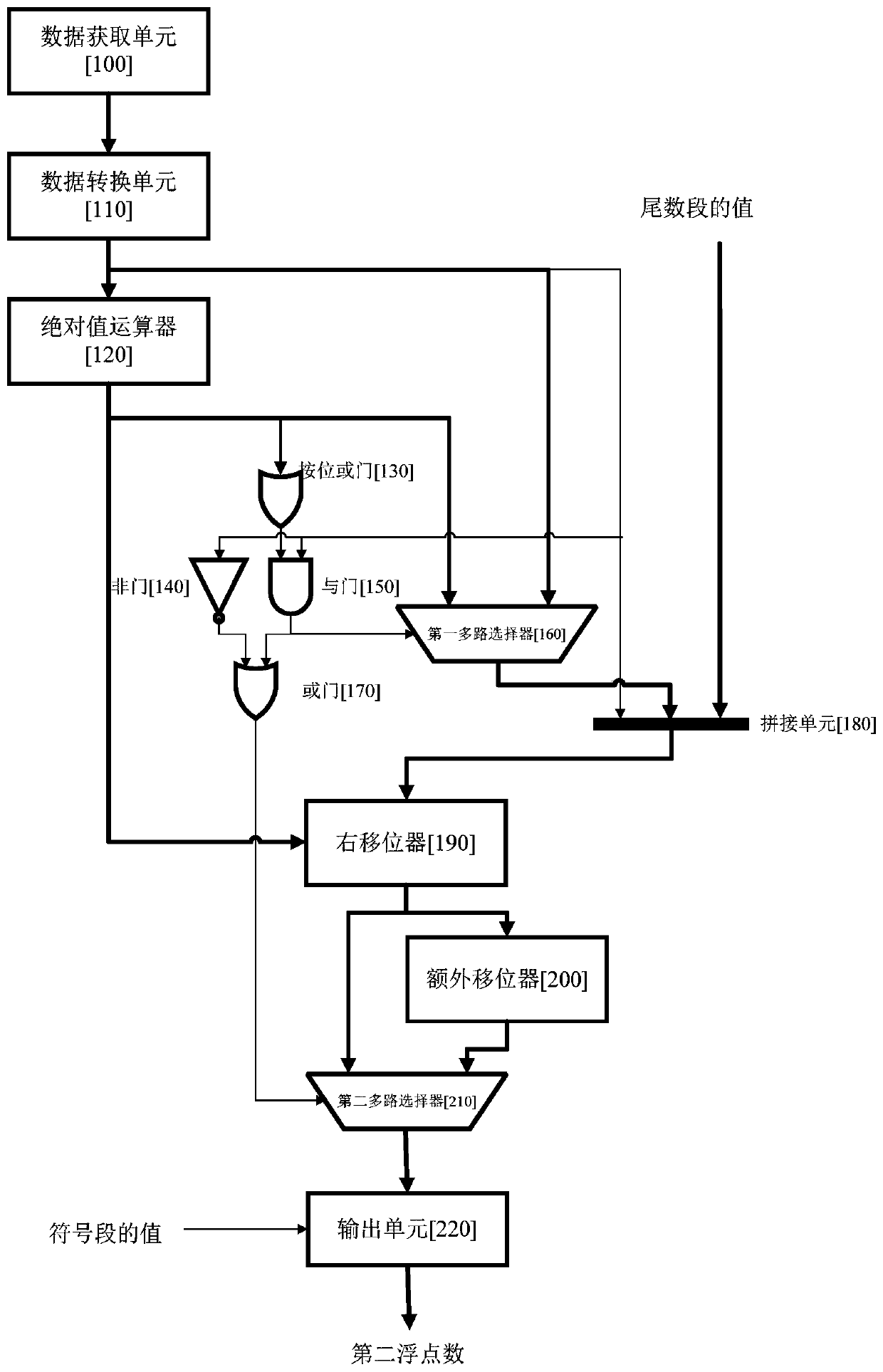

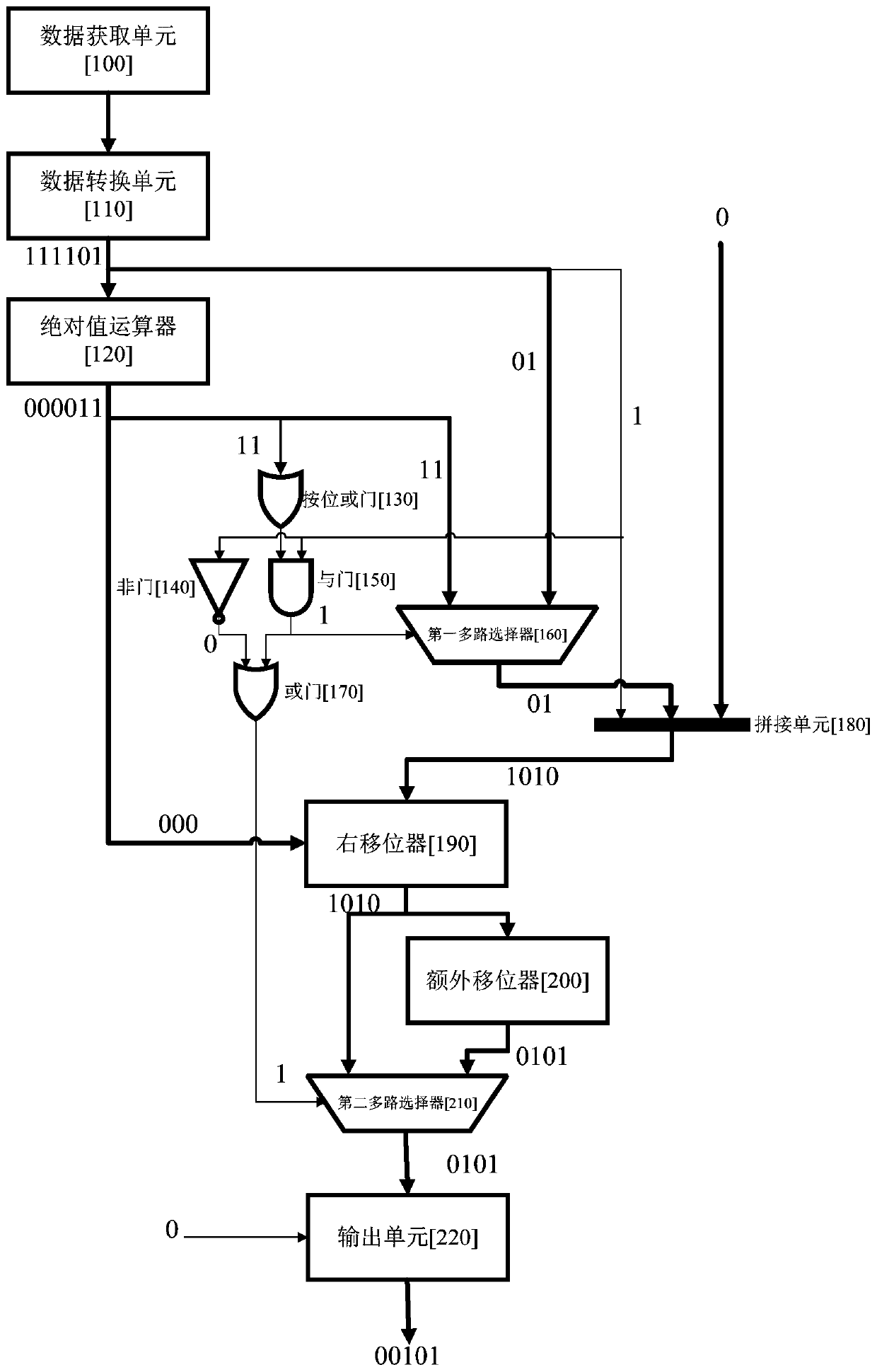

Floating-point number conversion method and device

PendingCN111313905AImprove training efficiencyGuaranteed accuracyCode conversionEnergy efficient computingData setAlgorithm

The invention discloses a floating-point number conversion method and a floating-point number conversion device, which can convert a single-precision floating-point number based on an IEEE 754 specification into a floating-point number in a posit data format, namely a second floating-point number. In the training process of a plurality of neural networks, the operation data approximately obeys normal distribution; data can be concentrated near 0 through transformation; however, the floating-point number of the posit data format in the invention can ensure the precision near 0 in the neural network training process; moreover, the preset total bit width of the floating-point number in the posit data format can be regulated and controlled, so that the data bit width can be reduced to a greatextent, resources required for storage and resources consumed in the read-write process are reduced, and the efficiency of neural network training is improved.

Owner:NANJING UNIV

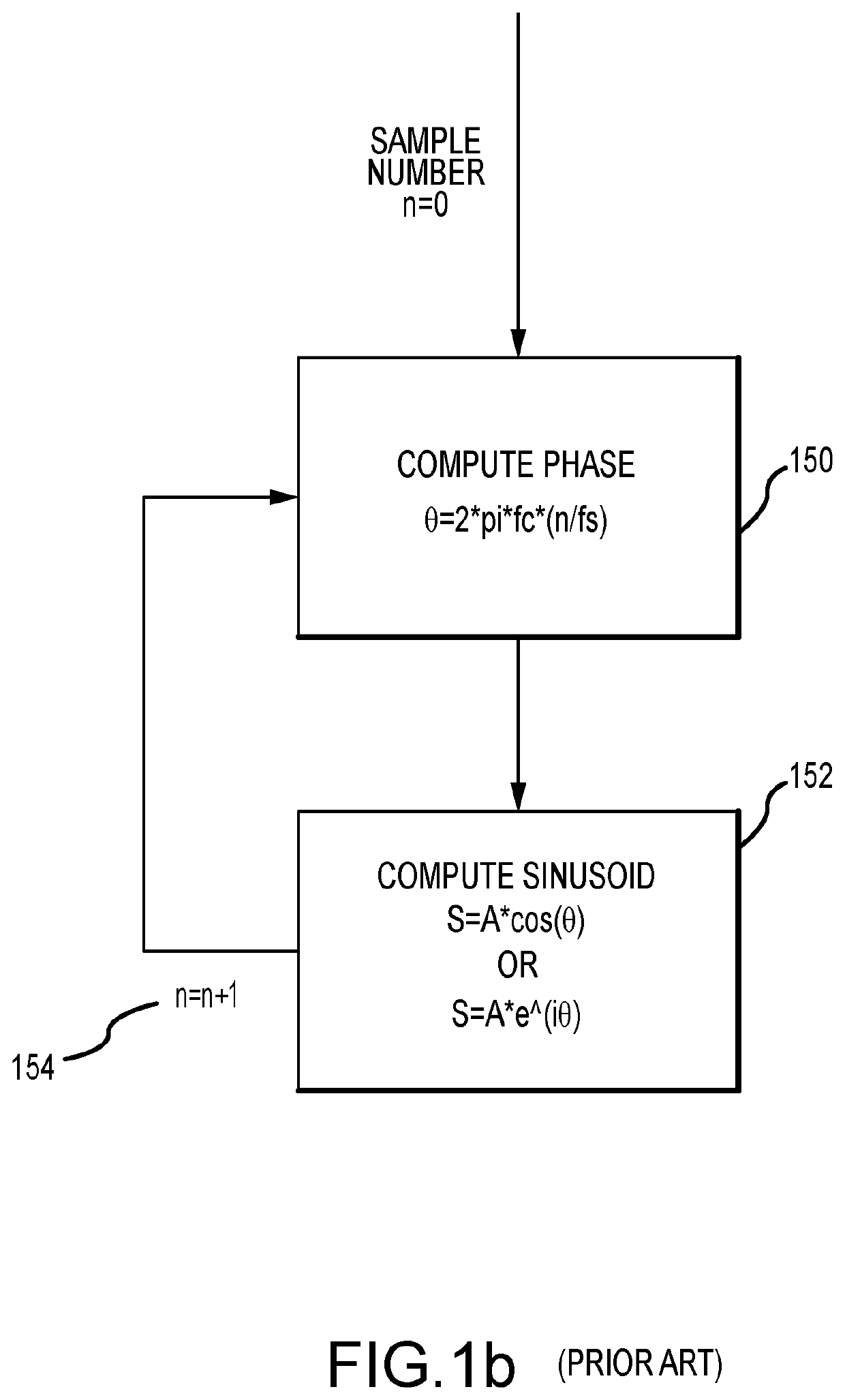

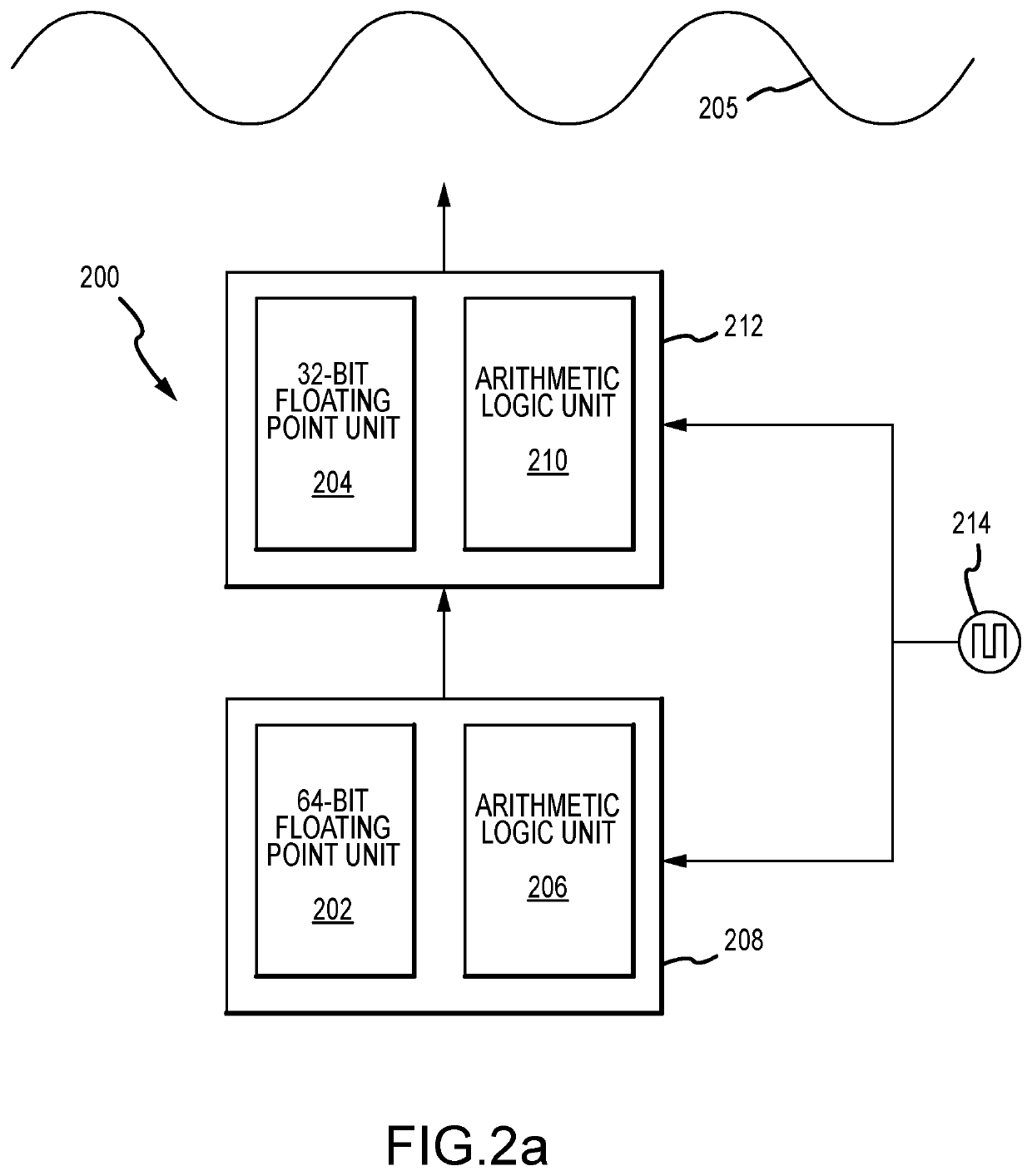

Computationally efficient mixed precision floating point waveform generation

ActiveUS20200409660A1Pointing accuratelyReducing generally unacceptable lossInterprogram communicationConcurrent instruction executionMachine epsilonSingle-precision floating-point format

Computationally efficient mixed precision floating point waveform generation takes advantage of the high-speed generation of waveforms with single-precision floating point numbers while reducing the generally unacceptable loss of precision of pure single-precision floating point to generate any waveform that repeats in 2π. This approaches computes a reference phase in double precision as the modulus of the phase with 2π and then computes offsets to that value in single precision. The double precision reference phase is recomputed as needed depending on how quickly the phase grows and how large a machine epsilon is desired.

Owner:RAYTHEON CO

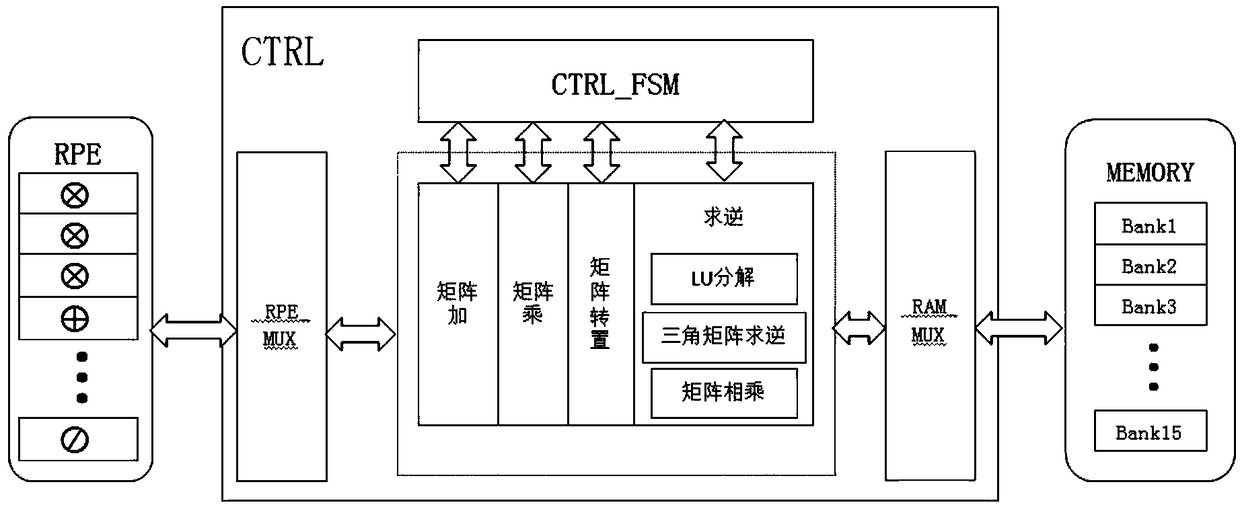

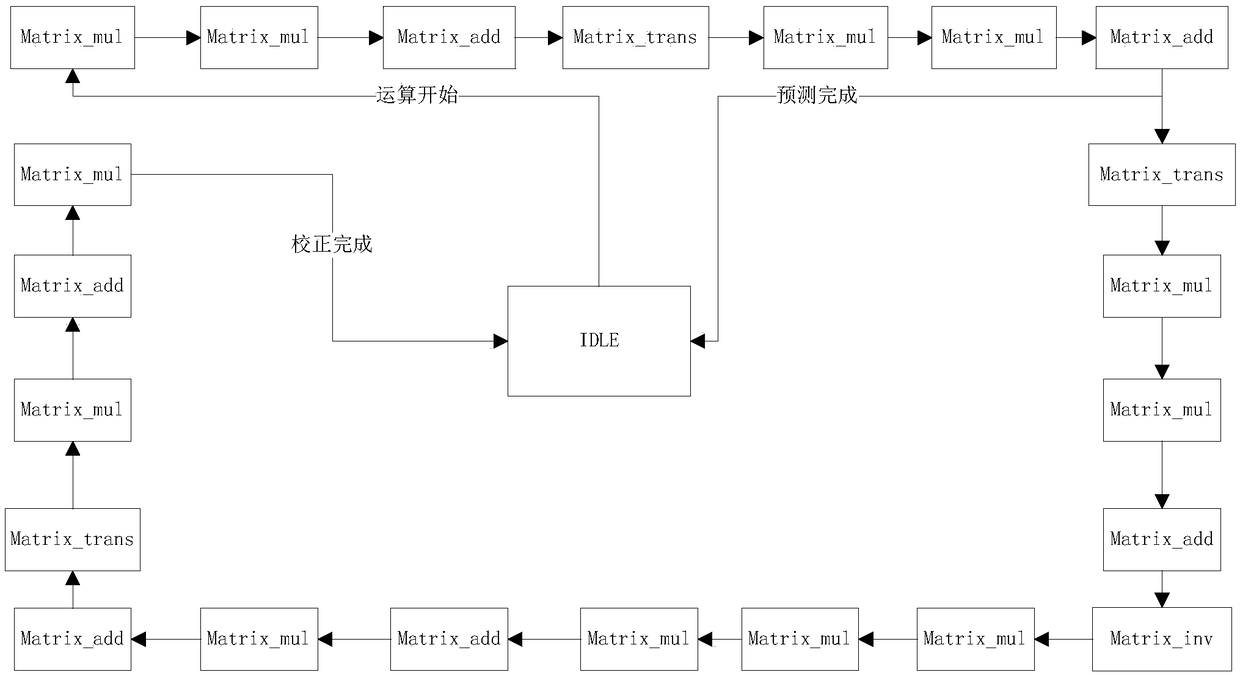

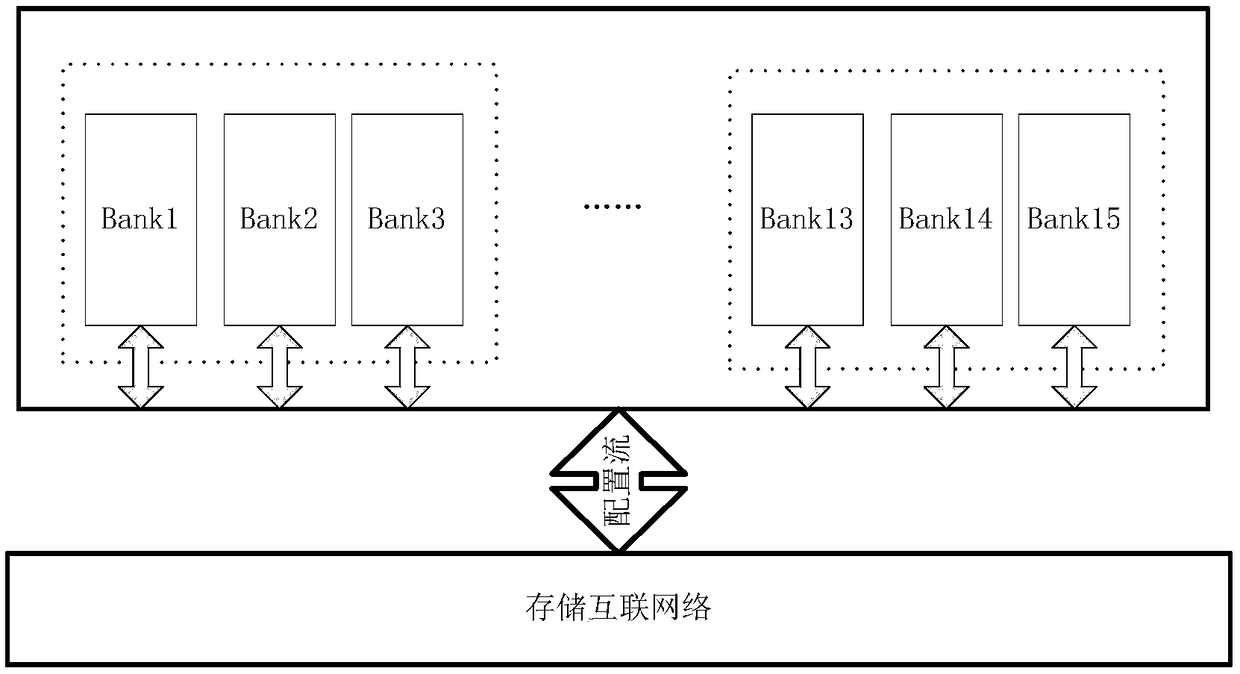

An arbitrary order Kalman filtering system

InactiveCN109376332AImprove reuse rateWide range of applicationsDigital data processing detailsComplex mathematical operationsSystems designParallel computing

The invention relates to an arbitrary-order Kalman filtering system, comprising: a configurable memory array comprising a plurality of memory banks, wherein the memory banks are globally shared; a configurable computing array, including single-precision floating-point number multiplier, a single-precision floating-point number adder and a single-precision floating-point number divider; a matrix basic operation module, completing matrix addition, matrix subtraction, matrix transposition and matrix inversion; and the global configurable computing array is shared by time-sharing multiplexing; a state machine, according to the recurrence equation of the Kalman filter algorithm, the matrix basic operation module is called step by step, the intermediate result of the matrix basic operation module is stored in the memory array, and then the intermediate result is called according to the recurrence equation. The invention multiplexes the computing resource array and the storage resource arraythrough time-sharing and folding mode, thereby effectively reducing resources and area, and reducing power consumption. Multi-path parallel method is used to design the basic matrix operation, which can effectively improve the real-time performance and data processing ability of the system design.

Owner:NANJING UNIV

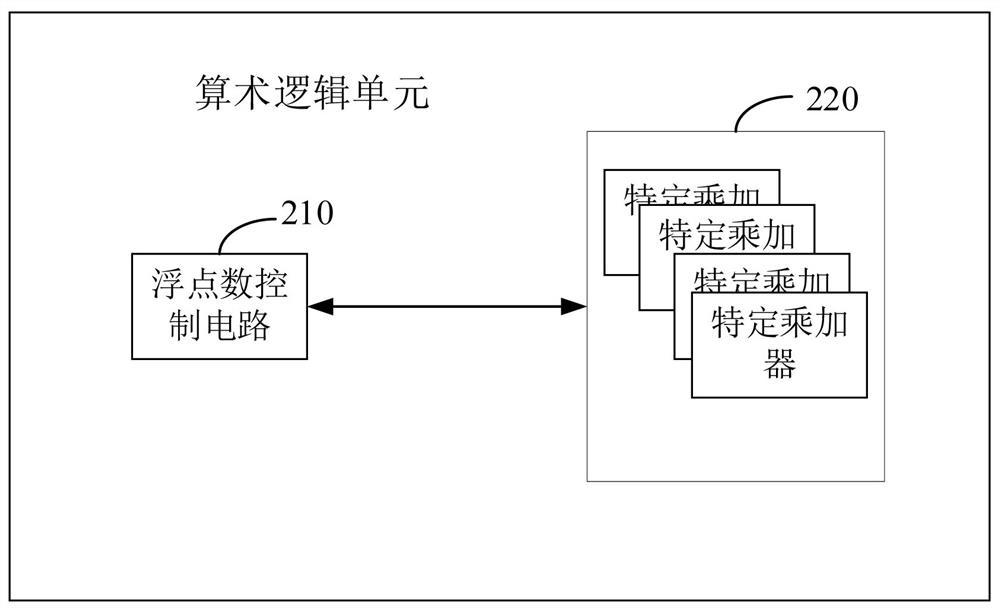

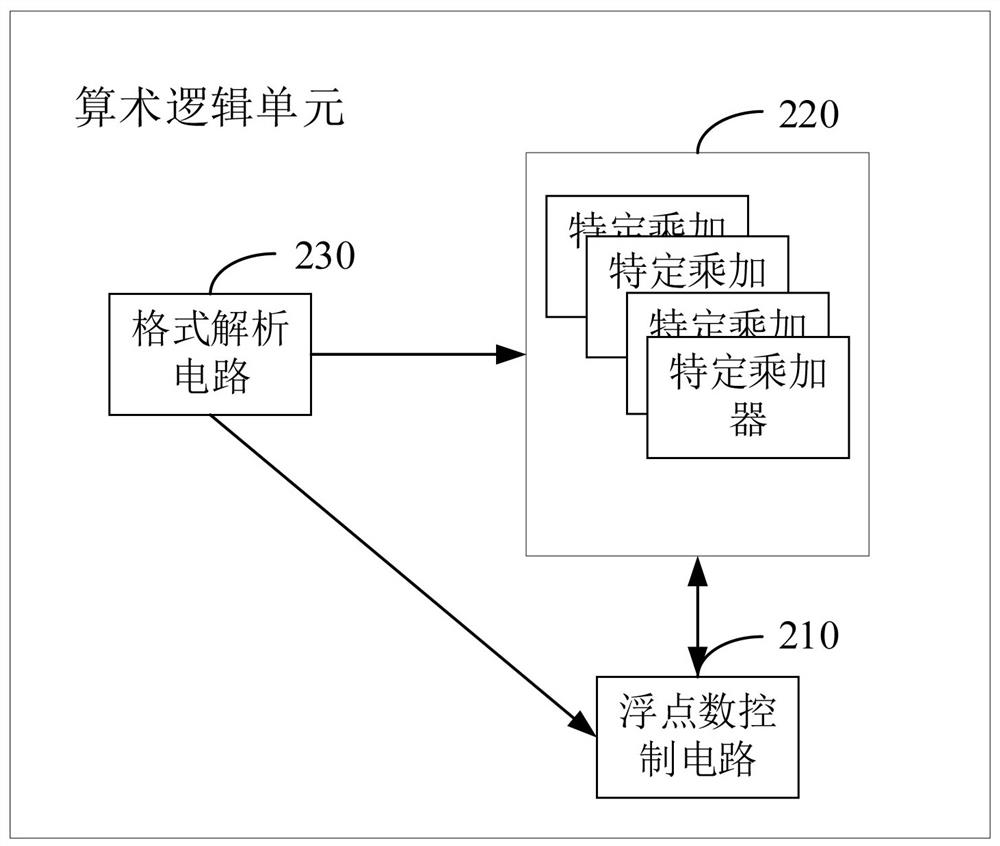

An arithmetic logic unit, a floating point number processing method, a gpu chip, and an electronic device

ActiveCN114461176BDigital data processing detailsProcessor architectures/configurationArithmetic logic unitLogic cell

Owner:XIANGDIXIAN COMPUTING TECH (CHONGQING) CO LTD

Method and device for processing floating point numbers

ActiveCN105224284BImprove computing powerDigital data processing detailsParallel computingSingle-precision floating-point format

Embodiments of the invention disclose a method and a device for processing floating-point numbers. The method comprises: obtaining a first target floating-point number X and a second target floating-point number Y; obtaining an operation rule of the X and the Y; under the condition that the X and the Y are not zero, performing exponent matching on the X and the Y; calculating the exponent of a final result; respectively segmenting the mantissas of the X and the Y whose exponents are matched, and respectively calculating results of each segment data of the mantissa of the X and each segment data of the mantissa of the Y; according to calculation result, generating a final mantissa; according to the final mantissa and the exponent obtained by calculation, generating a calculation result; and performing normalizing processing on the calculation result, to obtain a final calculation result. Using the method, the mantissa of a floating-point number with high precision is segmented, and each segment of mantissa is converted to the floating-point number with single precision to calculate, so that lower-end CPU products which do not have double-precision floating-point number computing power have high-precision floating-point number computing power, and computing power of the lower-end CPU products on the high-precision floating-point number is improved.

Owner:BEIJING QIYI CENTURY SCI & TECH CO LTD

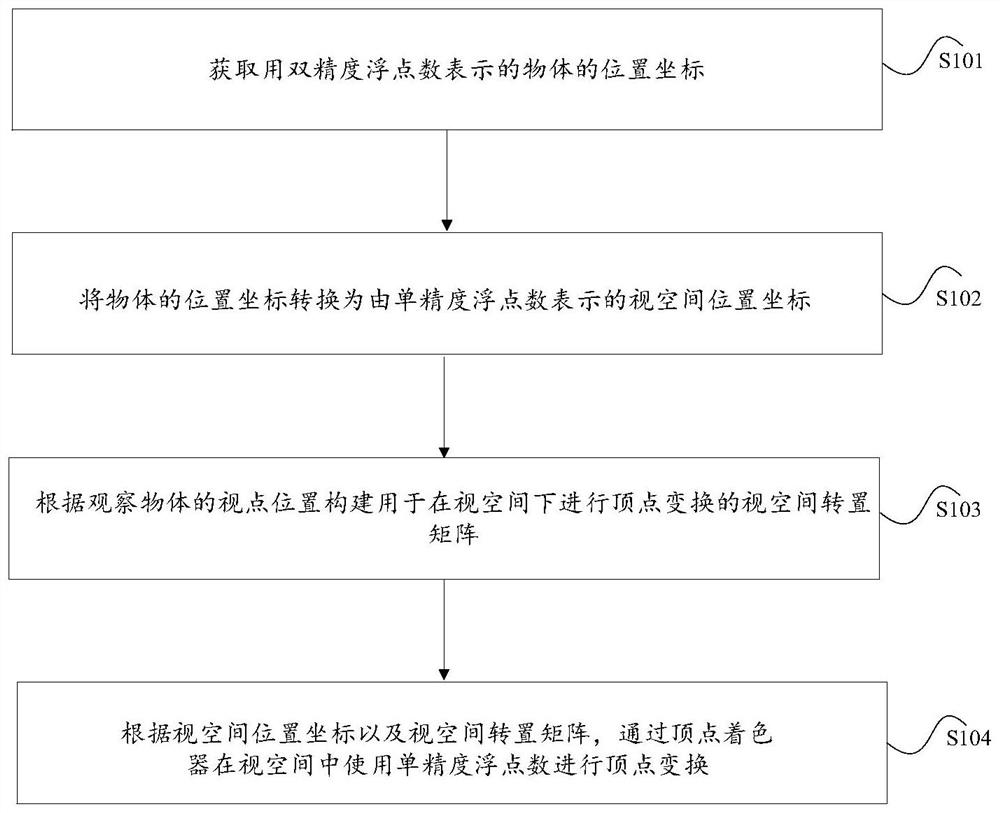

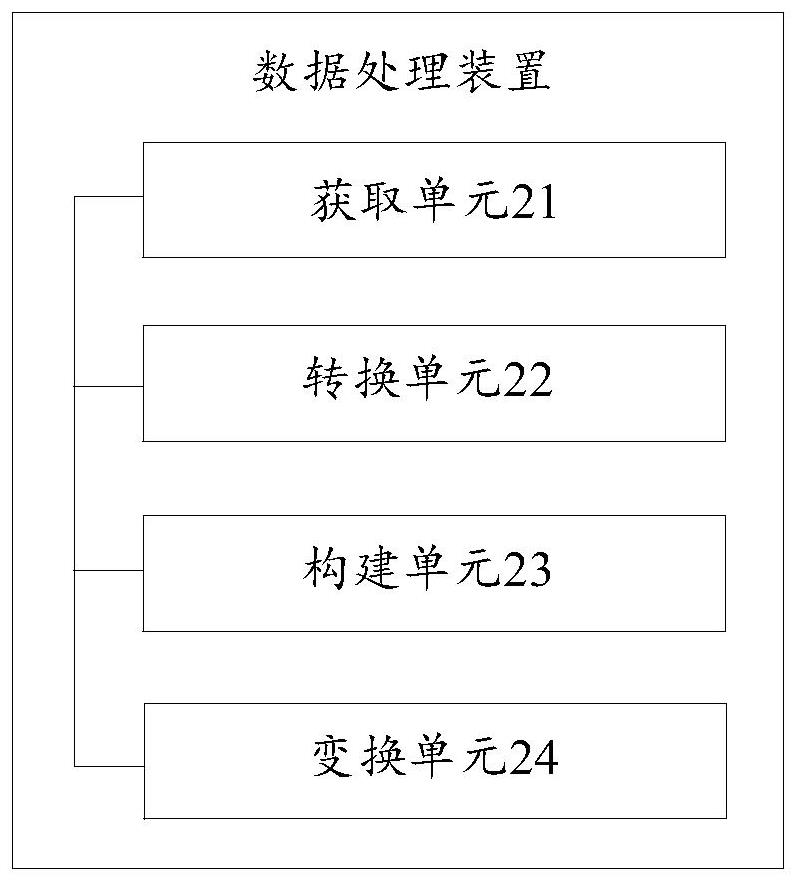

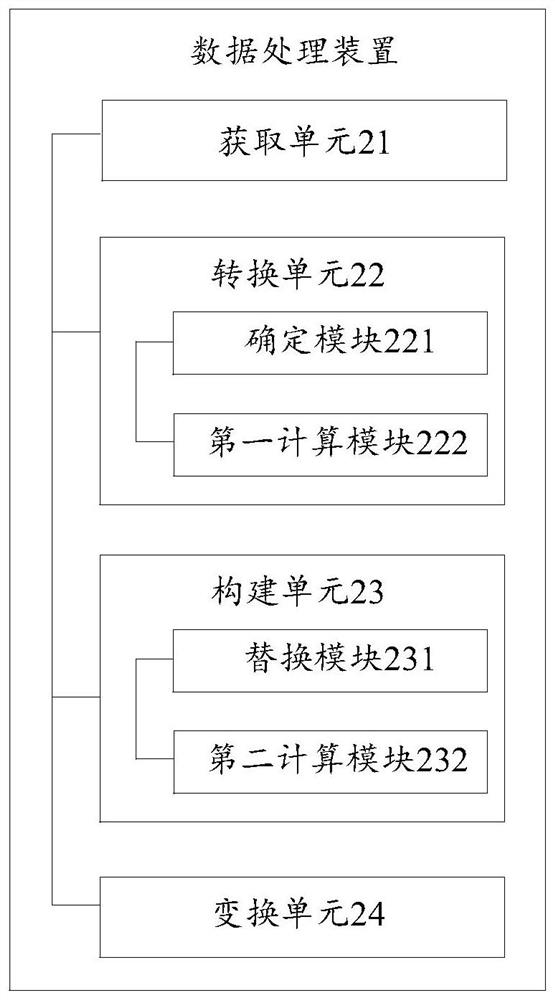

Data processing method and device

The invention discloses a data processing method and device. The method comprises the following steps: acquiring a position coordinate of an object represented by a double-precision floating-point number; converting the position coordinate of the object into a visual space position coordinate represented by a single-precision floating-point number, wherein the visual space is a camera space; constructing a visual space transpose matrix used for performing vertex transformation in a visual space according to a viewpoint position for observing the object, wherein the visual space transpose matrix is a model-viewport-perspective matrix represented by a single-precision floating-point number; and according to the visual space position coordinates and the visual space transpose matrix, performing vertex transformation in the visual space by using a single-precision floating-point number through a vertex shader. According to the method and the device, the problem of picture jitter in the application of the existing virtual earth technology is solved.

Owner:北京中航双兴科技有限公司

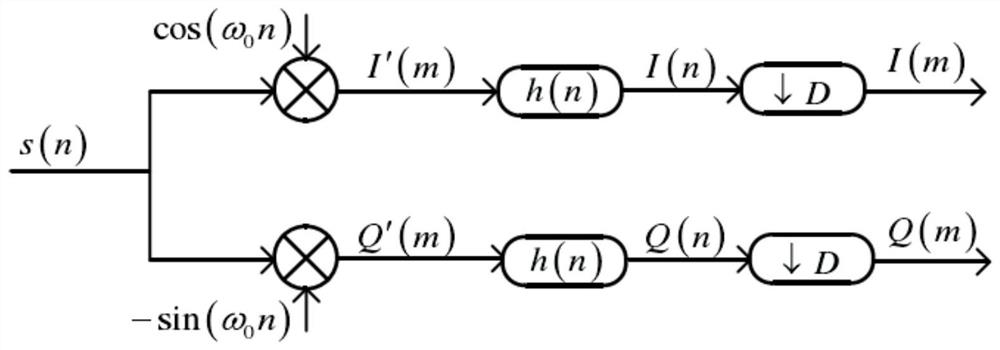

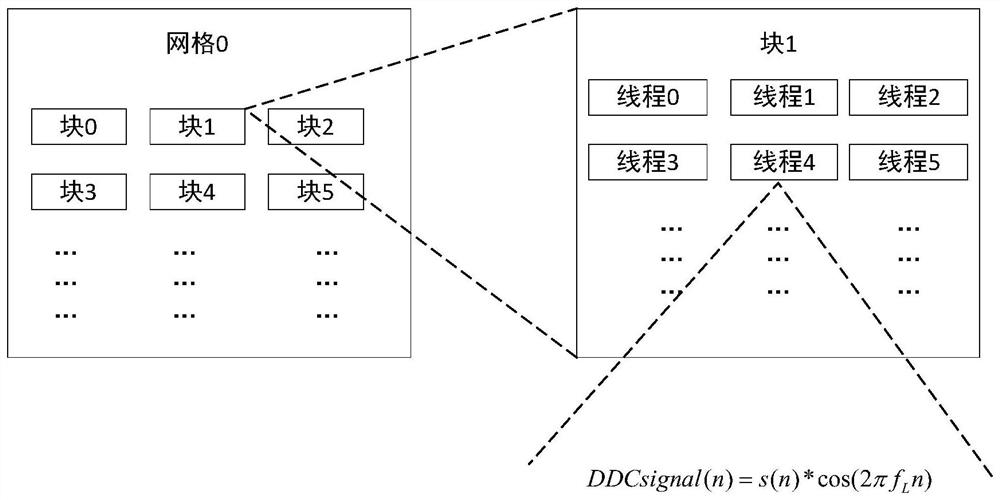

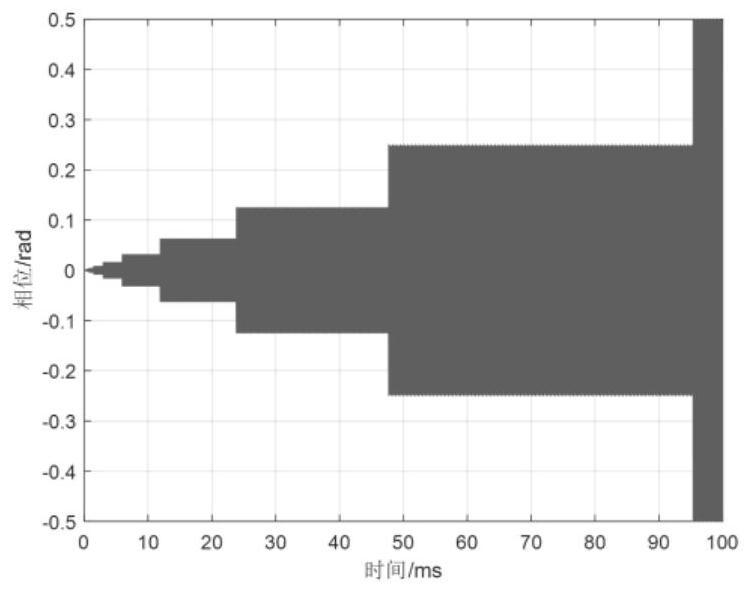

Method for realizing single-precision floating-point number accumulative error control in down-conversion based on GPU (Graphics Processing Unit)

ActiveCN114510268AShort debugging and development cycleStop the spreadConcurrent instruction executionSimulationTerm memory

The invention discloses a method for realizing accumulative error control in down-conversion based on a GPU (Graphics Processing Unit), which relates to the technical field of communication, and can be used for strictly controlling the accumulative error among K limited data points by analyzing the values of the frequency resolution, the actual sampling frequency and the down-conversion frequency required by engineering and calculating the relationship among the three values. And the phase value is returned to zero every K points, so that the propagation of error accumulation is prevented. According to the method, a lookup table is not used for calculating the phase value, precious on-chip memory resources are saved, the resource utilization rate is higher, accumulated errors are controlled within limited data points, and error accumulation is smaller. According to the method for calculating the accumulation of the control errors of the down-conversion based on the GPU, aiming at the relation between the local frequency of the down-conversion and the sampling frequency, the accuracy requirement is met while the frequency of the down-conversion is ensured to be flexible and variable, and calculation results show that the accumulation errors can be effectively controlled at the order of magnitude of 1e-8.

Owner:PLA PEOPLES LIBERATION ARMY OF CHINA STRATEGIC SUPPORT FORCE AEROSPACE ENG UNIV

Floating-point number conversion circuit

PendingCN111310909AImprove training efficiencyReduce data widthDigital data processing detailsPhysical realisationData setAlgorithm

The invention discloses a floating-point number conversion circuit which can convert a single-precision floating-point number based on an IEEE 754 specification into a single-precision floating-pointnumber in a poit data format, namely a second floating-point number. In the training process of a plurality of neural networks, the operation data approximately obeys normal distribution; data can beconcentrated near 0 through transformation; however, the precision of the single-precision floating-point number in the posit data format in the invention can be ensured near 0 in the neural network training process; moreover, the preset total bit width of the single-precision floating-point number in the posit data format can be regulated and controlled, so that the data bit width can be reducedto a great extent, resources required for storage and resources consumed in the read-write process are reduced, and the neural network training efficiency is improved.

Owner:NANJING UNIV

Data conversion method, multiplier, adder, terminal device and storage medium

ActiveCN110888623BThe numerical value represents a large rangeReduce computational overheadComputation using non-contact making devicesNeural architecturesData transformationBinary multiplier

The present invention relates to a data conversion method, a multiplier, an adder, a terminal device and a storage medium. The method includes: inputting a floating-point number F; converting the input floating-point number F according to the following conversion rules, and the conversion rules are: wherein, a i is an integer number, each integer number is n bits, i represents the serial number, and k represents the number of integers; according to the converted floating-point number F, the new standard number converted into k n-bits is set integer a i Numbers arranged in descending order or ascending order from high order to low order; when the floating point number F=0, the k n-bit integer numbers are negative infinity; the converted new standard number is output. The present invention not only retains the advantages of a large numerical representation range of single-precision floating-point numbers, but also reduces the calculation overhead of floating-point number multiplication operations, so it can reduce the calculation overhead of deep neural network algorithms, and provide low-cost, low-power Deployment on consumer devices provides a solution.

Owner:JIMEI UNIV